Стабилизатор переменного напряжения

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН

„„Я0„„1272316

А1 (5ц 4 б 05 1 !2

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (2 I ) 3904761/24-07 (22) 04.06.85 (46) 23.11.86. Бюл. № 43 (71) Институт электродинамики AH УССР и Институт проблем моделирования в энергетике АН УССР (72) К. А. Липковский, Ю. В. Сидоренко, В. А. Халиков и А. Л. Шихутский (53) 621.316.722.! (088.8) (56) Авторское свидетельство СССР № 935892, кл. Ci 05 F 1/!2,,1982.

Авторское свидетельство СССР

¹ 1107111, кл. G 05 F 1/12, 1984. (54) СТАБ ИЛ ИЗАТОР ПЕРЕМЕННОГО

НАПРЯЖЕНИЯ (57) Изобретение относится к стабилизированным источникам питания переменного напряжения. Целью изобретения является повышение точности и быстродействия. Цель достигается путем реализации измерительноr0 органа стабилизатора в виде времяимпульсного устройства на базе интегратора 9 и аналоговых ключей 18, 19 и 20. При этом реализуется функция деления частотнозависимых напряжений. Эти напряжения получают с выходов двух предварительно обнуленных интеграторов 7 и 8 при одновременной подаче на их входы соответственно полупериода напряжения, пропорционального выходному, и постоянного эталонного напряжения с источника 17. Управляющее напряжение регулирующего органа I не зависит от длительности периода, так как частное от деления двух зависящих от одного и того же параметра величин не зависит от этого параметра и равно отношению этих величин. 2 ил, 1272316 колебаниях частоты напряжения питаю- tp щей сети.

Ма фиг. 1 представлена функциональ!

25 входу к выходу интегратора 9, а неинвертирующим — к общему проводу устройства, логические схемы 2И вЂ” HE 14 и

2ИЛИ вЂ” HE 15, причем выход первой соеди- 30 нен с одним из входов последней непосредственно, а с вторым ее входом через формирователь 16 импульсов перезаписи, источник 17 эталонного напряжения, подключенный своим отрицательным полюсом через управляемые ключи 18 и 19 к входам интеграто- 35 ров 7 и 8 соответственно, управляемый переИзобретение относится к электротехнике, ь частности к преобразовательной технике, и может быть использовано для построения точных быстродействующих стабилизаторов переменного напряжения, работающих при больших изменениях частоты стабилизируемого напряжения.

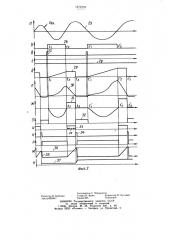

Цель и э обретен и я — повышение точности и быстродействия стабилизатора переменного напряжения при значительных ная схема стабилизатора; на фиг, 2 — эпюры напряжений в характерных точках схемы.

Устройство содержит регулирующий орган 1, узел 2 сравнения, к одному из входов которого подсоединен выход источника 3 опорного напряжения, а к второму входу — выход ячейки 4 памяти, выход уэла 2 сравнения подключен к управляющему входу регулирующего органа 1, синхронизатор-формирователь 5, подсоединенный входом к входу устройства, измерительный трансформатор 6, первичная обмотка которого соединена с выходом стабилизатора, три интегратора 7 — 9, выполненные на базе операционных усилителей с ключами 10 — 12 сброса соответственно, компаратор 13, подсоединенный инвертируюц!им ключающий ключ 20, имеющий два входа и один выход, подключенный к входу интегратора 9, причем первый из его входов соединен с одним иэ выводов вторичной обмотки измерительного трансформатора 6, второй вывод которой заземлен, а второй подсоединен к выходу интегратора 8. Первый выход синхронизатора-формирователя подключен к управляющему входу ключа 12 сброса интегратора 9, а второй его выход к одному из входов схемы 2И вЂ” HE 14 и управляющим входам ключей 19 и 20. Второй вход схемы 2И вЂ” ME !4 соединен с выходом компаратора 13, куда также подсоединен управляющий вход ключа 11 сброса интегратора 8. Управляющие входы ключа 10 сброса интегратора 7, ключа 18 и ячейки

4 памяти соединены соответственно с выходами схемы 2ИЛИ вЂ” HE 15, схемы 2И—

HE l4 и формирователя импульсов перезаписи, а выход интегратора 7 подключен к входу ячейки 4 памяти, состоящей иэ буферного усилителя 21, подсоединенного параллельно его входу, конденсатора 22 и уп-.

55 равляемого ключа 23, включенного между входом усилителя 21 и собственно входом ячейки 4 памяти. Причем ее управляющий вход является управляющим входом ключа 23. В интеграторе 9 параллельно ключу 12 включен диод 24, причем его катод присоединен к выходу интегратора 9.

Устройство работает следующим образом.

Напряжение 25 13- (фиг. 2а) поступает на вход регулирующего органа I, преобразуясь на его выходе в выходное напряжение стабилизатора. Синхронизатор-формирователь ежепериодно вырабатывает импульсы

26, совпадающие по фазе с переходом через нуль стабилизируемого напряжения, и импульсы 27, задний фронт которых также совпадает с моментом этого перехода (фиг. 2б, в). Импульсы 27 напряжения ежепериодно обнуляют интегратор 9 перед началом отрицательного полупериода напряжения, подготавливая интегратор к измерению. Измерительный трансформатор 6 приводит выходное напряжение, с учетом максимальных его отклонений, к величине, допустимой для входных цепей электронного ключа 20 и интегратора. Ключи 20 и 19 при поступлении на их управляющие входы импульса 27 напряжения разрешают прохождение отрицательной полуволны напряжения с вторичной обмотки трансформатора 6 на вход интегратора 9 и напряжения 28 (фиг. 2г) источника 17 эталонного напряжения на вход интегратора 8.

Интегрирование соответствующих напряжений на интеграторах 8 и 9 производятся с момента времени ti, совпадающего с передним фронтом импульса 26) до момента времени tz, совпадающего с задним фронтом того же импульса и окончанием отрицательного полупериода входного напряжения. В момент на выходах интеграторов 8 и 9 появляются напряжения 29 и 30.

С момента времени t> ключ 19 размыкается, а ключи 20 подключает вход интегратора 9 к выходу интегратора 8, который при этом переходит в режим хранения информации (фиг. 2д, интервал t2 — t3).

Полярность напряжения 31, поступающего на вход интегратора 9 в интервале времени tq — t, противоположна полярности напряжения, проинтегрированного в интервале t< — tz (фиг. 2ж). Напряжение на выходе интегратора 9 с момента t начинает линейно уменьшаться и после перехода через нуль ограничивается на уровне прямого падения напряжения на диоде 24 (фиг. 2е, интервал t> — t ). Переход напряжения 30 через нуль в момент времени ta фиксирует компаратор 13 (напряжение 32, фиг. 2з), который одновременно обнуляет интегратор

8 (фиг. 2д) .

Интервал времени At через постоянный" по величине коэффициент пропорциональности выражает величину среднего значения выходного напряжения стабилизатора, причем

127231G

Формула изобретения

45 длительность этого интервала не,зависит от длительности периода измеряемого напряжения. Интервал 33 времени At (фиг. 2и) выделяется логической схемой 14 совпадения

2И вЂ” НЕ и соответствует времени между задним фронтом импульса 26 и передним фронтом импульса 32. Для преобразования интервала времени At в пропорциональное ему напряжение на вход предварительно обнуленного интегратора 7 на время At c помощью ключа 18, управляемого схемой 14, подсоединяется источник 17 эталонного напряжения.

По абсолютной величине напряжение на выходе интегратора 7 в момент времени t3 равно среднему значению напряжения на вторичной обмотке измерительного трансформатора 6. По заднему фронту импульса

33 формирователь 16 формирует импульс 34 напряжения перезаписи (фиг. 2к), поступающий на управляющий вход ключа 23 ячейки

4 памяти, в которой происходит запоминание напряжения 35 на выходе интегратора

7 (фиг. 2м) конденсатором 22. Узел 2 сравнения выделяет разность опорного напр яжения источника 3 и измеренного напряжения

36, поступающего с выхода буферного усилителя 21. Сигнал 37 рассогласования (фиг. 2м) с выхода узла сравнения используется для соответствующего управления регулирующим органом. Схема 15 после выборки измеряемого напряжения формирует импульсы сброса интегратора 7 (фиг. 2л).

Перед началом следующего отрицательного полупериода входного напряжения снова происходит сброс интегратора 9 и в дальнейшем цикл измерения повторяется.

Таким образом, в один полупериод производится интегрирование измеряемого и эталонного напряжений, а время второго полупериода используется для деления напряжений, полученных после интегрирования. Результат деления двух напряжений в виде интервала времени в последующем преобразуется в пропорциональное напряжение. В итоге напряжение на выходе узла сравнения оказывается пропорциональным отклонению среднего значения выходного напряжения стабилизатора от номинальной величины, а не разности площадей приведенного выходного и эталонного напряжений за полупериод, чем и достигается улучшение качества стабилизации входного напряжения.

Стабилизатор переменного напряжения, содержащий регулирующий орган, вклк ченный между входными и выходными клеммами, первый интегратор с ключом сброса, выходом соединенный с входом ячейки памяти, измерительный трансформатор, подключенный первичной обмоткой к выходным клеммам, источник опорного напряжения, соединенный выходом с одним из входов узла сравнения, синхронизатор-формирователь, входом подключенный к входным клеммам, отличающийся тем, что, с целью повышения точности и быстродействия, в стабилизатор введены второй и третий интеграторы с ключами сброса, компаратор, источник эталонного напряжения, формирватель импульсов перезаписи, логические элементы

2И вЂ” НЕ и 2ИЛИ вЂ” НЕ, три управляемых ключа, причем источник эталонного напряжения соединен через первый и второй управляемые ключи с входами первого и второго интеграторов, а выход последнего через первый вход третьего управляемого ключа — с входом третьего интегратора, к второму входу третьего управляемого ключа подключен один из выводов вторичной обмотки измерительного трансформатора, второй вывод которой заземлен, выход третьего интегратора соединен с инвертирующим входом компаратора, второй вход которого заземлен, а выход соединен с управляющим входом ключа сброса второго интегратора и первым входом элемента 2И вЂ” НЕ, выход элемента

2И вЂ” НЕ подключен к первому входу элемента 2ИЛИ вЂ” НЕ непосредственно, к второму входу — через формирователь импульсов перезаписи, и к управляющему входу первого ключа — непосредственно, первый выход синхронизатора-формирователя подсоединен к управляющему входу ключа сброса третьего интегратора, а второй выход — к второму входу элемента 2И вЂ” НЕ и к управляющим входам второго и третьего ключей, выход элемента 2ИЛИ вЂ” HE соединен с управляющим входом ключа сброса первого интегратора, а выход формирователя импульсов перезаписи — с управляющим входом ячейки памяти, выход которой подключен к второму входу узла сравнения, выход которого соединен с управляющим входом регулирующего органа.

1272316 фиг.

Составитель С. Чернышева

Техред И. Верес Корректор О. Луговая

Тираж 836 Подписное

ВНИИ ПИ Государственного комитета СССР по делам изобретений и открытий

1 13035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Филиал ППП «Патент», г. Ужгород, ул. Проектная, 4

Редактор К. Бобкова

Заказ 6338/47