Селектор для импульсных асинхронных систем связи

Иллюстрации

Показать всеРеферат

Изобретение касается передачи сигналов. Цель изобретения - повышение помехоустойчивости устройства. Селектор содержит пороговый элемент 1, блок 3 задержки, элемент 4 совпадения , линию 6 з цержки, интегратор 5 и фантострон 7. Введение потен.циальной схемы 8 совпадения, пикового детектора 10 и образование новых связей между элементами устройства позволяет при заданной помехозащищенности принимаемого сигнала уменьшить мощность передатчика на 20%. 2 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (19) (И! (5!)4 Н 04 В 1 10

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCHOMV СВМДЕТЕПЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (61) 439929 (21) 3870836/24-21 (22) 12.03.85 (46) 23. 11.86. Бюл. Ф 43 (71) Ордена Трудового Красного Знамени институт кибернетики с вычислительным центром Научно-производственного объединения "Кибернетика"

АН УЗССР (72) P.Ë.Ïóëàòîâ (53) 621.396.49(088.8) (56) Авторское свидетельство СССР

Ф 439929, кл. Н 04 В 1/10, 1972. (54) СЕЛЕКТОР ДЛЯ ИМПУЛЬСН6!Х АСИНXP0HHbE СИСТЕМ СВЯЗИ (57) Изобретение касается передачи сигналов. Цель изобретения — повышение помехоустойчивости устройства.

Селектор содержит пороговый элемент

1, блок 3 задержки, элемент 4 совпадения, линию 6 задержки, интегратор 5 и фантострон 7/. Введение потен .циальной схемы 8 совпадения, пикового детектора 10 и образование новых связей между элементами устройства позволяет при заданной помехозащищенности принимаемого сигнала уменьшить мощность передатчика на 207.

2 ил.

1272511

Изобретение относится к области передачи сигналов, а именно к селекторам для импульсных асинхронных систем связи и является усовершенствованием изобретения по авт.св. 5

У 439929.

Цель изобретения — повышение помехоустойчивости.

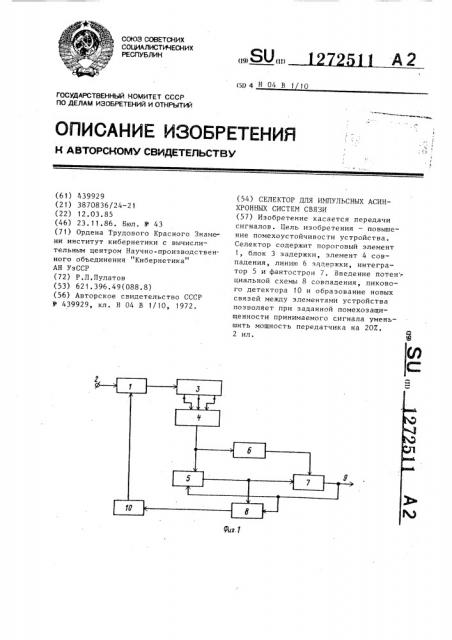

На фиг. 1 приведена функциональная структурная схема селектора; на фиг. 2 — временные диаграммы его работы.

Селектор для импульсных асинхронных систем связи содержит пороговый элемент 1, вход которого соединен с IS входной шиной 2 устройства, а выход— с входом блока 3 задержки, выводы которого расположены в соответствии с кодом адреса и соединены с соответствующими входами элемента 4 сов- 20 падения. Выход элемента совпадения соединен с первым входом интегратора

5 и через линию 6 задержки — с входом фантастрона .7. Выход фантастрона

7 .соединен с вторым входом интегратора 5, управляющим входом потенциального элемента 8 совпадения и выходной шиной 9 устройства. Выход интегратора 5 соединен с управляющим входом фантастрона 7 и входом потен- ЗО циального элемента 8 совпадения, выход которого соединен с входом. пикового детектора 10, выход которого соединен с управляющим входом порогового элемента 1.

Устройство работает следующим образом.

Поступающий на входную шину 2 импульс сравнивается в пороговом элементе 1 с текущим значением

40 порогового напряжения Б„(фиг ° 2 а), при этом на выходе порогового элемен- та 1 формируется нормированный по амплитуде импульс (фиг. 2 б), который, переходя через блок 3 задержки и элемент совпадения, преобразуется в импульс, представленный на фиг. 2 в, в соответствии с кодом адреса блока

3 задержки. Фронтом импульса с выхода элемента 4 совпадения запускается интегратор 5, на выходе которого формируется напряжение (фиг. 2 г), пропорциональное длительности этого импульса. Фронтом этого же импульса (фиг. 2 в), но прошедшего через линию 6 задержки (э ), производится запуск фантастрона 7, формирующего импульс, длительность которого (р) определяется напряжением на управляющем входе и равна половине длителЬности импульса на выходе элемента 4 совпадения, что обеспечивает постоянство временного интервала между срезом выходного импульса (фиг. 2 е) и импульсом, поступающим на входную шину 2 устройства, Импульс с выхода фантастрона 7 поступает на вход потенциального элемента 8 совпадения и на второй вход интегратора 5, разряжая его. С выхода потенциального элемента 8 совладения импульс с амплитудой, равной напряжению на выходе интегратора перед разрядом, поступает на пиковый детектор 10, в котором производится корректировка выхбдного напряжения, поступающего на управляющий вход порогового элемента 1 (фиг. 2 д). Пороговое напряжение, устанавливаемое при этом в пороговом элементе 1, пропорционально напряжению на управляющем входе.

Таким образом, с увеличением амплитуды входных импульсов растет пороговое напряжение элемента i и наоборот, что обеспечивает высокую помехозащищенность устройства.

Формула из обретения

Селектор для импульсных асинхронных систем связи по авт.св.

11- 439929, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены потенциальный элемент совпадения и пиковый детектор, выход которого соединен с управляющим входом порогового элемента, а вход — с выходом потенциального элемента совпадения, вход управления которого соединен с выходом фантастрона, а вход — с выходом интегратора.

1272511

Фиг.

Составитель А. Сазанов

Техред Н.Глущенко Корректор В. Синицкая

Редактор Л. Гратилло

Заказ 6350/57

Тираж 624

Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, о ктная 4