Устройство защиты от ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к технике связи. Цель изобретения - поддержание достоверности при ухудшении качества канала. Устройство содержит на передающей стороне: входной накопитель 1, переключатель 2, кодер 3, блок 4 памяти, датчик 5 сигналов обмена , датчик 6 служебных команд и счетчик 7 блокировки, а на приемной стороне: дешифратор 8 служебных команд , входной накопитель 9, декодер 10, счетчик 11 блокировки, выходной накопитель (ВН) 12, датчик 13 сигналов обмена, четыре элемента И 14, 22, 23 и 24, четыре элемента задержки

СОЮЗ СОВЕТСКИХ

COLlHAËÈCTÈ×ЕСКИХ

РЕСПУБЛИН (58 4 Н 04 L 1/12

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A BTOPCHOMV СВИДЕТЕЛЬСТВУ

Аюи

cm

ll!/ пр икр

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3676798/24-09 (22) 20.12.83 (46) 23. 11. 86. Бюл. 9 43 (72) С.В. Часовников, И. Е. Гришин, В.M.Ðåäîçóáîâ, В.И.Карпов и M.Ä.Рубанов (53) 621. 394. 14 (088. 8) (56) Шляпоберский В.И. Основы техники передачи сообщений. M.: Связь, 1973, с. 388-399.

Авторское свидетельство СССР

Ф 766029, кл. Н 04 L 1/12, 1978. (54) УстРОЙСтВО ЗАЩИТЫ От ОШИВок (57) Изобретение относится к технике связи. Цель изобретения — поддержание достоверности при ухудшении качества канала. Устройство содержит на передающей стороне: входной накопитель 1, переключатель 2, кодер 3, блок 4 памяти, датчик 5 сигналов обмена, датчик 6 служебных команд и счетчик 7 блокировки, а на приемной стороне: дешифратор 8 служебных команд, входной накопитель 9, декодер 10, счетчик 11 блокировки, выходной накопитель (ВН) 12, датчик

13 сигналов обмена, четыре элемента

И 14, 22, 23 и 24, четыре элемента задержки (ЭЗ) 15, 16, 21 и 25, два триггера (Т) 17 и 20 и два элемента

ИЛИ 18 и 19. Цель достигается введением элементов И 14, 22, 23 и 24, ЭЗ 15, 16, 21 и 25, Т 17 и 20 и элемента ИЛИ 19, с помощью которых при обнаружении ошибки в принимаемой информации запрещается прохождение сигнала ошибки и устройство переводится в поочередные циклы запроса, при которых проверяются на наличие ошибки знаки, предшествующие разблокировке ВН 12. 1 ил.

1272514

Изобретение относится к технике связи и может быть использовано в системах передачи данных с решающей обратной связью, Цель изобретения — поддержание . достоверности при ухудшении качества канала.

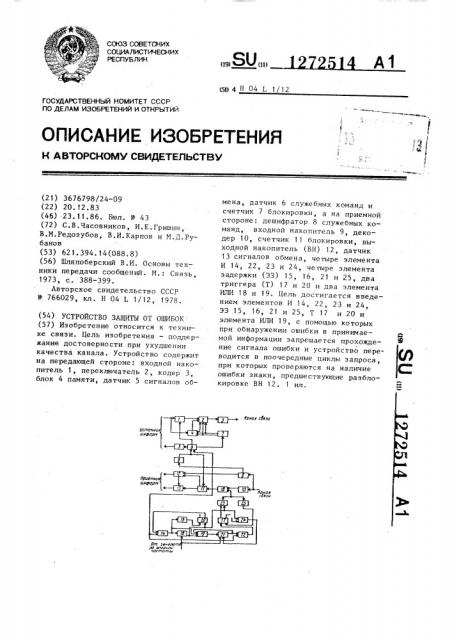

На чертеже представлена структурная электрическая схема предлагаемого устройства. 1О

Устройство защиты от ошибок содержит на передающей стороне входной накопитель 1, переключатель 2, кодер

3, блок 4 памяти, датчик 5 сигналов обмена, датчик 6 служебных команд, 15 счетчик 7 блокировки, а на приемной стороне — дешифратор 8 служебных команд, входной накопитель 9, декодер 10, счетчик 11 блокировки, выI ходной накопитель 12, датчик 13 сигналов обмена, первый элемент И 14, первый 15 и второй 16 элементы за-, держки, первый триггер 17, первый и второй элементы ИЛИ 18 и 19, второй триггер 20, третий элемент 21 задержки, второй, третий и четвертый элементы И 22 — 24 и четвертый элемент 25 задержки.

Устройство защиты от ошибок работает следующим образом.

При отсутствии искажений в принимаемой информации датчик 5 сигналов обмена посылает источнику информации сигнал о готовности принять от него очередную комбинацию, которая 35 записывается во входной накопитель

1 и в блок 4 памяти. Затем с помощью кодера 3 вводится необходимая избыточность и кодовая комбинация передается в канал связи. 4О

На приемной стороне данная комбинация поступает во второй входной. накопитель 9 и одновременно в декодер 10, где происходит обнаружение ошибки в комбинации. Если ошибка не 45 обнаружена, то комбинация переписывается в выходной накопитель 12 и датчик 13 сигналов обмена сообщает потребителю информации о готовности выдать ему информацию. Если прием- 5О ная станция обнаружит искаженный знак, то на выходе декодера 10 появится сигнал, который через первый элемент

ИЛИ 18 подается на счетчик 11 блокировки и на датчик 6 служебных команд, 55 а также через первый элемент И 14 на вход первого элемента 15 задержки.

Продвижение единицы по первому элементу 15 задержки осуществляется цикловой частотой f Сигнал с второго выхода счетчика 11 блокировки блокирует прием п комбинаций в выходной накопитель 12. Датчик 6 служебных я 11 команд записывает комбинацию Запрос во входной накопитель 1 и включает счетчик 7 блокировки, сигнал с первого выхода которого обеспечивает считывание и комбинаций из блока 4 памяти, через переключатель 2 вслед за комбинацией "Запрос".

При приеме комбииации иЗапрос" которая выделяется с помощью дешифратора 8 служебных команд, сигнал с последнего подается на счетчик 11 блокировки. В результате этого при приеме комбинации "Запрос" осуществляется блокировка выходного накопителя 12 и в канал связи посылается

"Запрос" и и комбинаций из блока 4 памяти.

При обнаружении ошибки сигнал из декодера 10 через первый элемент

ИЛИ IS и первый элемент И 14 поступа-! ет также на вход первого и второго элементов 15 и 16 задержки, а через i элемент ИЛИ 19 — на вход третьего элемента 21 задержки.

Второй элемент 16 задержки задерживает сигнал на и тактов цикловой частоты, а третий элемент 21 задержки — на и-1 такт цикловой частоты.

Через один такт после записи единицы на вход второго элемента 16 задержки и на вход первого элемента

15 задержки второй триггер 20 сигналом первого элемента 15 задержки переводится в положение, при котором с его выхода не поступает потенциал на первый вход первого элемента

И 14. В результате этого запрещается прохождение сигнала "Ошибкап с выхода первого элемента ИЛИ 18 через первый элемент И 14. За один цикл до снятия блокировки с выходного накопителя 12 на выходе третьего элемента 21 задержки появляется импульс.

Если в это время декодер 10 обнаружит ошибку в принимаемой информации, то сигнал "Ошибка с его выхода через первый элемент ИЛИ 18, второй элемент И 22 поступит на первый вход первого триггера 17, который разрешит прохождение сигнала с выхода второго элемента 16 задержки через третий элемент И 23 на вход первого элемента ИЛИ 18.

1272514

Если даже после разблокировки выходного накопителя 12 ошибка в принимаемой информации не обнаружена, прием информации снова заблокируется, аппаратура переведется в очередной 5 цикл запроса и на вход второго элемента 16 задержки запишется единица.

Поскольку выход третьего элемента 21 задержки замкнут через второй элемент ИЛИ 19 с его выходом, то в треть- о ем элементе 21 задержки во втором цикле запроса циркулируют друг за другом две следующие единицы и, следовательно, в этом цикле проверяются на наличие ошибки два знака, предшествующие разблокировке выход,ного накопителя 12. Эта проверка происходит аналогично описанному, т.е. при обнаружении ошибок в одном или обоих знаках, предшествующих 20 разблокировке, сигнал "Ошибка" из декодера 10 через первый элемент

ИЛИ 18 и второй элемент И 22 пере— ведет первый триггер 17 в состояние, разрешающее передачу сигнала с выхода второго элемента 16 задержки через третий элемент И 23 на вход первого элемента ИЛИ 18 и далее на вход счетчика 11 блокировки и на вход датчика 6. Аппаратура переве- 30 дется ц очередной цикл запроса и повторения, в третий элемент 21 зас держки записывается третья единица.

В следующем цикле запроса на наличие ошибки проверяется уже четыре комбинации, предшествующие разблокировке выходного накопителя 12. Число единиц в третьем элементе 21 задержки увеличивается с каждым цик— лом запроса, пока этот элемент задер-щ жки не заполнится полностью, после чего проверке подвергаются все знаР ки, поступающие на прием во время блокировки выходного накопителя 12.

Если в течение цикла запроса ошибки в принимаемой информации не обнаружены, то сигналы с выхода третьего элемента 21 задержки на вход первого триггера 17 через второй элемент

И 22 не поступают. Вследствие этого первый триггер 17 останется в состоянии, разрешающем прохождение сигнала с выхода второго элемента 16 задержки через четвертый элемент И 24 для стирания сигналов в третьем 55 элементе 21 задержки. В этом случае в момент поступления импульса с вы— хода второго элемента 16 задержки устройство переводится в исходное состояние, при котором запрос корреспонденту посылается при очередном обнаружении ошибки в принимаемой информации.

Ф о р м у л а и з о б р е т е н и я

Устройство защиты от ошибок, держащее на передающей стороне последовательно соединенные входной на-, копитель, переключатель и кодер, при этом информационный вход входного накопителя ° объединен с первым входом блока памяти, к второму входу которого подключен второй выход переключателя, а также датчик служебных команд, первый, второй и третий выходы которого подключены соответственно к входу датчика сигналов обмена, второму входу входного накопителя и к входу счетчика блокировки, первый и второй выходы которого подключены к соответствующим входам переключателя и блока памяти, на приемной стороне объединенные по входу декодер и входной накопителв, первый и второй выходы которого подключены соответственно к входу дешифратора служебных команд и к первому входу выходного накопителя, выход которого подключен к первому входу датчика сигналов обмена, к второму входу которого подключен первый выход счетчика блокировки, второй выход которого подключен к второму входу выходного накопителя, а также первый элемент

ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью поддержания достоверности при ухудшении качества канала, на приемной стороне введены второй элемент ИЛИ, первый, второй, третий и четвертый элементы И, первый и второй триггеры,первьп, второй, третий и четвертый элементы задержки, при этом выход декодера подключен к первому входу первого элемента ИЛИ, выход которого подключен к первому входу счетчика блокировки и первым входам первого и второго элементов

И, выход первого элемента И подключен к входам первого и второго элементов задержки и к первому входу второго элемента ИЛИ, выход которого подключен к первому входу третьего элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ и второму входу вто72514

Составитель С.Осмоловский

Техред Н.Глущенко Корректор JI.Ïàòàé

Редактор Л.Гратилло

Заказ 6350/57 Тираж 624 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

5 1Z рого элемента И, выход которого подключен к первому входу первого триггера, первый и второй выходы которого подключены соответственно к первым входам третьего и четвертого элементов И, выход третьего элемента И подключен к второму входу первого элемента ИЛИ и к входу четвертого элемента задержки, выход которого подключен к второму входу первого триггера выход первого элемента задержки подключен к первому входу второго триггера, к второму входу которого и к вторым входам третьего и четвертого элементов И подключен выход второго элемента задержки, выход четвертого элемента И подключен к второму входу третьего элемента задержки, а выход второго тригге5 ра подключен к второму входу первого элемента И,причем выход дешиф ратора служебных команд подключен к второму входу счетчика блокировки и к первому входу датчика служебных

10 команд, к второму входу которого подключен выход первого элемента ИЛИ, при этом вторые входы второго и треть его элементов частоты задержкй имеют объединенные входы опорной

15 частоты.