Устройство для определения области работоспособности электронных схем

Иллюстрации

Показать всеРеферат

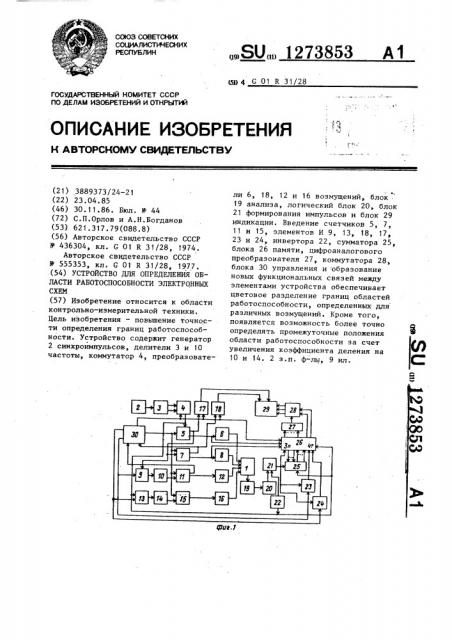

Изобретение относится к области контрольно-измерительной техники. Цель изобретения - повышение точности определения границ работоспособности . Устройство содержит генератор 2 синхроимпульсов, делители 3 и 10 частоты, коммутатор 4, преобразователи 6, 18, 12 и 16 возмущений, блок 19 анализа, логический блок 20, блок 21 формирования импульсов и блок 29 индикации. Введение счетчиков 5, 7, 11 и 15, элементов И 9, 13, 18, 17, 23 и 24, инвертора 22, сумматора 25, блока 26 памяти, цифроаналогового преобразователя 27, коммутатора 28, блока 30 управления и образование новых функциональных связей между злементами устройства обеспечивает цветовое разделение границ областей работоспособности, определенных для различных возмущений. Кроме того, появляется возможность более точно § (Л определять промежуточные положения области работоспособности за счет увеличения коэффициента деления на 10 и 14. 2 з,п. ф-лы, 9 кл.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ÄÄSUÄÄ 1273853 А1 (я) 4 G 01 R 31/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Со

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ4 (21) 3889373/24-21 (22) 23.04.85 (46) 30.11.86. Бюл. ll- 44 (72) С.П.Орлов и А.Н.Богданов (53) 621.317.79(088.8) (56) Авторское свидетельство СССР

У 436304, кл. G 01 R 31/28, 1974.

Авторское свидетельство СССР

У 555353, кл. G 01 R 31/28, 1977. (54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ОБЛАСТИ РАБОТОСПОСОБНОСТИ ЭЛЕКТРОННЫХ

CXEN (57) Изобретение относится к области контрольно-измерительной техники.

Цель изобретения — повышение точности определения границ работоспособности. Устройство содержит генератор

2 синхроимпульсов, делители 3 и 10 частоты, коммутатор 4, преобраэователи 6, 18, 12 и 16 возмущений, блок

19 анализа, логический блок 20, блок

21 формирования импульсов и блок 29 индикации. Введение счетчиков 5, 7, i1 и 15, элементов И 9, 13, 18, 17, 23 и 24, инвертора 22, сумматора 25, блока 26 памяти, цифроаналогового преобразователя 27, коммутатора 28, блока 30 управления и образование новых функциональных связей между элементами устройства обеспечивает цветовое разделение границ областей работоспособности, определенных для различных возмущений. Кроме того, появляется возможность более точно определять промежуточные положения области работоспособности за счет увеличения коэффициента деления на

10 и 14. 2 з.п. ф-лы, 9 ил.

1273853

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля области работоспособности электронных схем.

Цель изобретения — повышение точности определения границ области работоспособности путем цветового разделения границ областей работоспособности, определенных для различных возмущений.

На фиг.1 приведена схема устройства; на фиг.2 и 3 — временные диаграммы работы устройства; на фиг.4 схема блока памяти; на фиг.5 — cxeMa блока управления; на фиг.б — изображение на экране блока индикации; на фиг.7 — схема блока формирования импульсов; на фиг.8 — схема сумматора; на фиг.9 — формат ячейки памяти.

Устройство для определения области работоспособности электронной схемы 1 содержит генератор 2 синхроимпульсов, первый делитель 3 частоты, первый коммутатор 4, первый счетчик

5, второй преобразователь 6 возмущений, второй счетчик 7, третий преобразователь 8 возмущений, четвертый элемент И 9, второй делитель 10 частоты, третий счетчик, 11, четвертый преобразователь 12 возмущений, третий элемент И 13, третий делитель 14 частоты, четвертый счетчик 15, первый преобразователь 16 возмущений, первый 17 и второй 18 элементы И, блок

19 анализа, логический блок 20, блок

21 формирования импульсов, первый инвертор 22, пятый 23 и шестой 24 элементы И, сумматор 25, блок 26 памяти, цифроаналоговый преобразователь (ЦАП) 27, второй коммутатор 28, блок

29 индикации и блок 30 управления.

Блок 26 памяти образуют седьмой элемент И 31, первый 32 и второй 33 дешифраторы адреса, накопитель 34 и мультиплексор 35.

Блок 30 управления содержит первый 36, третий 37, и второй 38 триг— геры, восьмой 39 и девятый 40 элементы И и кнопку 41.

Блок 21 формирования импульсов состоит из второго инвертора 42 и формирователя 43 импульсов, например, типа К155АГ1. Сумматор 25 содержит счетчик, например типа К155ИЕ7.

Генератор 2 синхроимпульсов соединен выходом с входом первого делителя 3 частоты. Первый 16, второй 6-, третий 8 и четвертый 12 преобразова5

55 тели возмущений соединены выходами с соответствующими выходами устройства, входы которого соединены с соответствующими входами блока 19 анализа, соединенного выходами с соответствующими входами логического блока 20, выход которого соединен с первым входом блока 21 формирования импульсов. Первый и второй выходы первого делителя 3 частоты соединены с одноименными информационными входами первого коммутатора 4, соединенного управляющим входом с первым выходом блока 30 управления, первыми входами первого 17 и второго 18 элементов И и первым входом блока 26 памяти, выходом — с первым входом третьего элемента И 13, входом первого инвертора 22, вторым входом блока

26 памяти и счетным входом первого счетчика 5, соединенного установочным входом с установочными входами второго 7, третьего 11 и четвертого

15 счетчиков и вторым выходом блока

30 управления, выходом переноса — с вторым входом первого элемента И 17 с первым входом четвертого элемента

И 9 и счетным входом второго счетчика 7, соединенного выходом переноса с вторым входом второго элемента

И 18 и первым входом блока 30 управления, соединенного третьим выходом с вторым входом четвертого элемента

И 9, соединенного выходом через второй делитель 10 частоты со счетным входом третьего счетчика 11, соединенного выходом переноса с вторым входом блока 30 управления, соединенного третьим выходом с первым входом пятого элемента И 23, четвертым выходом — с первым входом шестого элемента И 24 и вторым входом третьего элемента И 13, соединенного выходом через третий делитель 14 частоты со счетным входом четвертого счетчика, соединенного информационными выходами с входами первого преобразователя 16 возмущений. Информационные выходы первого 5 и второго 7 счетчиков соединены соответственно с входами второго 6 и третьего 8 преобразователей возмущений. Информационные выходы третьего счетчика соединены с входами четвертого преобразователя 12 возмущений, выход первого инвертора 22 соединен с вторым входом блока 21 формирования импульсов, соединенного выходом с сумми1273853 рующим входом сумматора 25, вторыми входами пятого 23 и шестого 24 элементов И и третьим входом блока 26 памяти, соединенного четвертыми и пятыми входами соответственно с ин- . 5 формационными выходами первого 5 и второго 7 счетчиков, первыми выходами с информационными входами сумматора 25, соединенного выходами с шестыми входами блока 26 памяти, сое- 10 диненного седьмым и восьмым входами соответственно с выходами пятого 23 и шестого 24 элементов И, вторым входом — с синхровходом сумматора 25, вторым и третьим выходами — с соот- 15 ветствующими управляющими входами второго коммутатора 28,четвертыми выходами — с входами ЦАП 27, соединенного выходом с информационным входом второго коммутатора 28, соединенно- 20

ro тремя выходами с соответствующими сигналами входами блока 29 индикации, соединенного первым и вторым управляющими входами с выходами соответственно первого 17 и второго 18 элементов И.

В блоке 26 памяти первый дешифра-.îð 32 адреса соединен входами с четвертыми входами блока 26 памяти, выходами с первыми адресными входами 30 накопителя 34, соединенного входом записи с выходом седьмого элемента

И 31, соединенного первым входом с первым входом блока 26 памяти и с управляющим входом мультиплексора

35> вторым входом — с третьим входом блока 26 памяти, второй вход которого соединен с входом чтения накопителя 34, соединенного первыми, вторым и третьим информационными входа- 40 ми соответственно с шестыми, седьмым и восьмым входами блока 26 памяти, .вторыми адресными входами — с выходами дешифратора 33 адреса, соединенного входами с пятыми входами блока 4>

26 памяти, первые и четвертые выходы которого соединены соответственно с первыми и вторыми выходами мультиплексора, соединенного информационными входами с выходами младших раз- 50 рядов накопителя 34, выходы двух— старших разрядов которого соединены соответственно с вторым и третьим выходами блока 26 памяти.

В блоке 30 управления восьмсй зле мент -И 39 соединен выходом с S-входом первого триггера 36, первым входом — с вторым входом блока 30.управ-. ления, вторым входом — с инверсным выходом второго триггера 38 и первым входом девятого элемента И 40, соединенного вторым входом с первым входом блока 30 управления, выходом — с

Т входом третьего триггера 37, соединенного R-входом через замыкающие контакты кнопки 41 с шиной питания устройства, а непосредственно с К-входом второго триггера 38 и первым входом элемента ИЛИ 42, соединенного вторым входом с инверсным выходом третьего триггера 37 и S-входом второго триггера 38, выходом — с R-входом первого триггера 36, соединенного прямым выходом с третьим выходом блока 30 управления, четвертый, первый и второй выходы которого соединены соответственно с прямым выходом третьего триггера 37, прямым выходом второго триггера 38 и R — входом второго триггера 38.

Устройство работает следующим образом.

В первом режиме происходит генерация испытательных сигналов, поступающих на входные зажимы испытаемой электронной схемы 1, и определяется область работоспособности схемы, информация о которой записывается в блок 26 памяти.

Во втором режиме производится периодическое считывание этой информации из блока 26 памяти и вывод ее на блок 29 индикации, на экране которого формируется изображение области работоспособности испытуемой электронной схемы 1.

Режим генерации испытательных сигналов разделяется на три периода: а) воздействие на схему 1 двух (I и

II) возмущений; б) воздействие на схему l трех (I II и III) возмущений; в) воздействие на схему 1 четырех (I,II,III и IV) возмущений. Все указанные режимы реализуются по очереди автоматически.

Возмущения на испытуемую схему 1 поступают с выходов преобразователей

6,8, 12 и 16 возмущений. В качестве возмущающих воздействий могут использоваться напряжения питания,.активная и реактивная нагрузки по входам и выходам схемы 1 и т.п. Входными сигналами для преобразователей 6,8,12 и

16 возмущения являются параллельные цифровые коды с выходов счетчиков

5,7,11 и 15.

5 12738

Каждый из преобразователей 6,8,12 и 16 содержит последовательно включенные ЦАП и нормирующий усилитель, что позволяет преобразовать входной код в аналоговую величину возмуще- 5 ния (ток, напряжение и т.д.).

Режим генерации испытательных сигналов начинается с начальной установки в нуль счетчиков 5,7,11 и 15 по сигналу с выхода блока 30 управления. 1О

При этом на его первом и втором выходах устанавливаются нулевые уровни управляющих сигналов У, и У, запрещающие прохождение импульсов на входы делителей 10 и 14 частоты и посту- 15 пающие на входы элементов И 23 и 24.

Генератор 2 синхроимпульсов задает импульсы высокой частоты на вход делителя 3 частоты. На одном выходе делителя 3 частота импульсов соответ- 20 ствует частоте изменения величины первого возмущающего воздействия, на другом выходе †часто, соответствующей выводу иэображения на экран блока 29 индикации на ЭЛТ. В первом режиме нулевой уровень сигнала на выходе блока 30 управления поступает на коммутатор 4, который подключает на свой выход к первому выходу делителя 3 частоты нулевой уровень сигнала с блока 30 управления, запрещая прохождение сигналов через элементы

И 17 и 18 на входы синхронизации блока 29 индикации.

В результате синхроимпульсы гене- 35 ратора 2 через делитель 3 и коммутатор 4 проходят на вход счетчика 5 и код в нем ступенчато изменяется по линейно возрастающему закону (фиг. 2а и За). На фиг.2 изменение кода в 40 счетчике 5 показано непрерывной линией. При заполнении счетчика 5 на его выходе переноса появляется сигнал, который поступает на вход счетчика 7 и изменяет в нем код (фиг.2б). Вход- 45 ные коды счетчиков 5 и 7 управляют преобразователями 6 и 8 возмущений, в результате чего на электронную схему 1 в интервале времени (О, t,) действуют различные сочетания уровней 50 двух возмущающих воздействий.

Блок 19 анализа производит пороговый контроль правильности функционирования схемы 1, анализируя состояние по каждому из ее выходов в от- 55 дельности. При нахождении параметров схемы в поле допуска блок 19 анализа задает сигнал на вход логического

53 ь блока 20, реализующий функцию И, который формирует на своем выходе управляющий сигнал, принимающий единичное значение, когда электронная схема 1 по всем выходам находится в области работоспособности (фиг.Зв).

Этот сигнал поступает на один вход блока 21 формирования импульсов функционирования, на другой вход которого приходят синхросигналы, проинвертированные инвертором 22 (фиг.Зг).

В результате выходные импульсы блока

21 свидетельствуют о работоспособности схемы 1 при данных возмущениях (фиг.2ж).

Для запоминания условий работоспособности испытуемой схемы 1 используется блок 26 памяти матричного типа. Выход счетчика 5 подключен к первому адресному входу блока 26 и определяет строку матрицы, выход счетчика 7 соединен с вторым адресным входом и определяет столбец матрицы. В результате каждому значению кодов в счетчиках 5 и 7 соответствуют свои уровни возмущающих воздействий и свои ячейки памяти в накопителе 34 блока 26 памяти. Это позволяет одновременно с испытанием схемы 1 записывать оценку ее работоспособности в блок 26 памяти, причем адреса записи однозначно идентифицируют условия, при которых схема 1 работоспособна. Для этого в каждом такте по сигналу Чтение (фиг.3e), поступающему с выхода коммутатора 4 на вход чтения блока 26 памяти и синхровход сумматора 26, происходит считывание цифрового кода из выбранной ячейки. Этот код с выходов блока 26 поступает в сумматор 25, в котором запоминается. В начальный момент времени все ячейки накопителя 34 блока 26 содержат нулевой код. Выходной сигнал блока 21 передним фронтом до- бавляет единицу к считанному из блока

26 коду (фиг. Зд и Зж) в сумматоре

25. Сигнал с блока 21 поступает также на вход записи блока 26 памяти и разрешает запись кода из сумматора

25 в блок 26 после добавления единицы в сумматор 25. Если при данных уровнях возмущений происходит сбой испытуемой схемы 1, то логический блок 20 формирует сигнал, запрещающий выработку импульса на выходе блока 21. Таким образом, в первый период испытаний схема 1 оказывается под

1273853 воздействием двух возмущений и в блоке 26 памяти хранятся коды, принимающие значение единицы для тех уров-. ней возмущений, при которых сохраняется работоспособность схемы 1.

Для различения результатов испытаний при разном числе возмущений в два старших разряда ячеек накопителя 34 блока 26 памяти записывается код идентификации Y Y, поступающий 10 с выходов блока 30 управления (фиг.9) .

Нулевое значение кода соответствует первому периоду (О, t,1испытаний.

Запись кода идентификации Y Y произ1 водится одновременно с переписью кода из сумматора 25, в блок 26 значения Y u Y поступают с выходов элементов И 23 и 24 по выходному сигналу блока 21, стробирующему эти элементы.

Второй период испытаний (t з начинается в момент t, по сигналу переноса счетчика 7 (фиг.2б и 2д), который устанавливает единичный уровень сигнала У, в блоке 30 управления, открывающий элемент И 9. В результате синхроимпульсы проходят на делитель 10 частоты и в счетчике 11 код начинает изменяться с частотой в М раз меньшей, чем в счетчике 7 30 (на фиг.2в М = 2) . Выходной код счетчика 11 управляет преобразователем

12 (третьего возмущения).. Так как цифровые коды в счетчиках 5 и 7 повторяют свои значения, аналогично происходит считывание кодов из ячеек блока 26 памяти и увеличение этих кодов на единицу, если схема 1 функционирует правильно. Однако в старшие разряды ячеек теперь записывает- 40 ся код идентификации Y Y = 10 покаТ зывающий, что на схему 1 воздействуют три возмущения.

На фиг.2з показано сужение облас" ти работоспособности при воздействии 4$ третьего возмущения (в том случае, если значение кода в данной ячейке не увеличилось). Сигнал на выходе переноса счетчика 11 в момент t на"3 чинает третий период испытаний. При $0 этом на втором выходе блока 30 управления устанавливается Y = 1 и син2хроимпульсы через элемент И 13 и делитель 14 частоты поступают в счетчик 15. Частота изменения кода в $$ счетчике 15 в L раз меньше, чем в счетчике 5 (на фиг. 2r L = 2). Теперь на схему 1 воздействуют четыре возмущения, что еще больше сужает область работоспособности.

В момент по второму сигналу на выходе переноса счетчика 11 режим генерации испытательных сигналов заканчивается: управляющие сигналы Yq

1 и Y равны нулю и на выходе блока управления 30 появляется сигнал, переключающий выход коммутатора 4 на второй выход делителя 3 частоты и открывающий элементы И 17 .и 18.

В режиме считывания информации частота синхроимпульсов на втором выходе делителя 3 соответствует частоте вывода точек изображения на экран

ЭЛТ в блоке 29, частота сигналов на выходе переноса счетчика 5 — частоте строк, а частота сигналов на выходе переноса счетчика 7 — частоте кад-. ров блока 29 индикации.

Выходные коды счетчиков 5 и 7, как и в предыдущем режиме, используются для адресации ячеек в накопителе 34 блока памяти 26 (фиг.4). Это позволяет синхронизировать вывод изображения области работоспособности на экран. В режиме считывания управляющий сигнал с выхода блока.30 управления переключает в блоке 26 памяти вывод считываемой информации на выходы, подключенные к входам ЦАП 27. Процессом считывания управляет сигнал нЧтение" на входе считывания блока 26 памяти.- С выходов блока 26 в ЦАП 27 поступают параллельные цифровые коды, содержащие информацию о работоспособности электронной схемы 1. Выходное напряжение ЦАП 27, пропорциональное коду на его входе, поступает на коммутатор 28.

Три выхода коммутатора 28 подключены в блоке 29 индикации на ЭЛТ соответственно к модулирующим электро; дам пушек: красной, зеленой и синей.

На управляющие входы коммутатора 28 с выходов блока 26 поступает код идентификации У, У . В результате яркость точки иэображения, выводимой в данный момент, определяется суммар" ным числом срабатываний электронной схемы 1 в первом, втором и третьем режимах, координаты точки — уровнями первого и второго испытательных возмущений, а цвет точки зависит от количества действовавших возмущений (см. таблицу).

12738

Цвет области, работоспособности

Действующие возмущения

Значение кода идентификации

Красный 10

0 0

I u II

I II u III

1 0

Зеленый

I II,III u IV Синий

U максб

U = — — — — п

1 К 11

" макс.5

П накс и

U = — — — n

"максб

= — - n

U 12

= — 1 - n

U кс

M,1 Ф мФкс1% где U

Макс1 . мак.с .1 и п з

Запоминание информации происходит в накопителе 34. Для выбора строк накопителя 34 используется дешифратор 32 адреса, на вход которого поступает параллельный цифровой код из счетчика 5, а на выходе дешифратора

32 образуется унитарный код. Аналогично дешифратором 33 преобразуется 25 код адреса с выхода счетчика 7.

По сигналу "Чтение" содержимое выбранной ячейки памяти накопителя

34 поступает на выходы блока 26 памяти. Причем старшие разряды сразу по- ЗО ступают на управляющие входы коммутатора 28, младшие разряды поступают на мультиплексор 35, управляемый с выхода блока 30 управления.

В зависимости от значения этого сигнала информация проходит или на входы сумматора 25 или на входы ЦАП

27. Запись информации в блок 26 памяти происходит по сигналу "Запись11, поступающему с блока 21. При выводе 4р изображения на экран ЭЛТ элемент

И 31 запрещает запись в блок 26.

На фиг.5 приведена схема блока 30 управления. Работа начинается с подачи сигнала установка" от кнопки

4 1, при этом триггеры 36-38 устанавливаются в ноль и вырабатывается сигнал сброса на третьем выходе блока

30. В исходном состоянии в триггерах

36 и 37 записан код Y Y д = 00 и gp проводится первый период испытаний.

Затем сигнал переноса счетчика 7 устанавливает триггер 36 в единицу и начинается второй период (Y Y = 10) °

Сигнал переноса счетчика 11 устанав- ливает триггер 37 в единицу и начинается третий период испытаний: У, Y<=

11. Второй сигнал переноса перебра53 10 сывает триггер 37 в нолв и положительный фронт на его инверсном выходе устанавливает в единицу триггер

38. На соответствующем триггеру 38 выходе блока 30 появляется единичный сигнал и начинается режим вывода изображения. Элементы И 39 и 40 при этом не пропускают сигналы на входы триггеров 36 и 37.

В случае неработоспособности схемы 1 сигнал с логического блока 20 поступает на инвертор 42, который запрещает срабатывание формирователя

43 импульсов. При работоспособности схемы 1 формирователь 43 запускается сигналом с выхода инвертора 22 и формирует короткий импульс на выходе.

Сумматор 25 предназначен для подсчета числа работоспособных состояний испытываемой электронной схемы

1 при фиксированных значениях возмущающих воздействий.

Подсчет осуществляется следующим образом.

При фиксированных кодах и, в счетчике 5-и в счетчике 7 выбирается ячейка накопителя 34 блока 26 памяти с адресом (п1, и ). В это же время х на испытываемую электронную .схему 1 подаются возмущающие воздействия (U U,,Б, 0 ) с преобразователей

6,8,12 и 16: наибольшие значения возмущающих воздеиствии; максимальные коды в соответствующих счетчиках текущие значения кодов в счетчиках 11 и 15.

Содержимое информационного поля ячейки (с адресом n,: п ) считывается из блока 26 и поступает на входы записи сумматора 25. Запись параллельного входного кода в сумматор 25 осуществляется по управляющему сигналу, снимаемому с выхода коммутато1273853

12 ра 4 (фиг.За) логический блок 20 формирует единичный уровень сигнала в том случае, если при данных значениях U „ Ь, U u U схема 1 работоспоз собна. Этот сигнал управляет блоком

21 формирования импульсов. Его выходной сигнал (фиг. Зд) поступает на счетный вход "+ 1" сумматора 5. Содержимое сумматора 25 увеличивается на единицу. Если схема 1 не работо- 10 способна при данных значениях возмущений, код в сумматоре 25 не меняется, так как логический блок 20 нулевым уровнем выходного сигнала запрещает выработку импульса блоком 21 ° 15

Сигнал записи в блок 26 памяти формируется блоком 2 1 и подается одновременно на вход записи блока 26 и на счетный вход сумматора 25 . Это не приводит к неправильному резуль- Ю тату, так как выполняется условие

t )) t, (где t — длительность им3 см з пульса блока 21; à t, — время срабатывания сумматора 25).

При неработоспособности электрон- 25 ной схемы 1 запись в блок 26 не производится, так как отсутствует выходной сигнал блока 21 (фиг.Зд). Содержимое ячейки памяти сохраняется прежним. 30

На фиг.2з буквы "к", "з", "с"— красный, зеленый, синий — обозначают цвет соответствующей области изображения согласно таблице. На диаграмме 2з показана последовательность изменения содержимого ячеек памяти блока 26 с помощью сумматора 25 при последовательном действии .различных комбинаций возмущений. Буква "К показывает, какие ячейки соответствуют 4О работоспособности только при I и ЕЕ возмущении, "з" — при действии I II и III возмущений, а "с" — при одновременном действии всех четырех возмущений. 45

Сумматор 25 выполняется на стандартных интегральных микросхемах, например, на основе двоичного счет-.

;чика К155ИЕ7. На вход С подается сигнал "Чтение" (фиг.Зв), который разре-50 шает считывание кода из блока 26 памяти и запись его по входам Р1-D8 в сумматор 25. На вход "+1." поступает импульсный сигнал с входа блока 21.

Выходы схемы подключены к входу бло- $$ ка 2б.

На изображении (фиг.6) области работоспособности испытуемой электвонной схемы 1, выведенной на экран ЭЛТ блока 29, одновременно видна конфигурация области при воздействии двух, трех и четырех возмущений. На фиг.6 показан пример изображения области работоспособности, где "- — красный, "о" — зеленый, "+" — синий цвет.

Это позволяет более точно определять область работоспособности за счет следующих факторов: — результаты испытаний хранятся в памяти блока 26 и стабильное изображение на экране может фиксироваться сколь угодно долго; — увеличение коэффициента деления делителей 10 и 14 частоты не влияет на качество изображения, следовательно, есть возможность более точного определения промежуточных положений области работоспособности; — частота синхроимпульсов делителя 3 частоты, управляющая испытательными возмущениями, не привязана к диапазону частот строчной и кадровой развертки ЭЛТ; — цветовое различие отдельных участков области на изображение облегчает зрительное восприятие и позволяет более точно определить грани-. цы области, так как градации цвета различаются легче, чем градация яркости в устройстве изображаются три области работоспособности при различной комбинации возмущений. Это позволяет наблюдать процесс изменения области работоспособности при увеличении числа воздействий.

Таким образом, устройство позволяет более точно формировать многомерную область работоспособности электронных схем с учетом многообразия возмущающих воздействий при соответствии параметров выходного сигнала всем предъявленным требованиям.

Формула изобретения

1. Устройство для определения об.ласти работоспособности электронных схем, содержащее блок индикации, генератор синхроимпульсов, соединенный выходом с входом первого делителя частоты, второй делитель частоты, первый, второй, третий, четвертый преобразователи возмущений, соединенные выходами с соответствующими вы1ходами устройства, входы которого.

1273853 соединены с соответствующими входами блока анализа, соединенного выходами, с соответствующими входами логического блока, выход которого соединен с первым входом блока формирования 5 импульсов, о т л и ч а ю щ е е с я тем, что, с целью повышения точности определения области работоспособности путем цветового разделения границ областей работоспособности, определенных для различных возмущений, в него введены третий делитель частоты, шесть элементов И, два коммутатора, цифроаналоговый преобразователь, первый инвертор, сумматор, четыре счетчика, блок памяти и блок управления, причем первый и второй выходы первого делителя частоты соединены с одноименными информационными входами первого коммутатора, соединенного управляющим входом с первым выходом блока управления, первыми входами первого и второго элементов И и первым входом блока памяти, выходом— с первым входом третьего элемента И, входом первого инвертора, вторым входом блока памяти и счетным входом первого счетчика, соединенного установочным входом с установочными входами второго, третьего и четвертого 30 счетчиков и вторым выходом блока управления, выходом переноса — с вторым входом первого элемента И, первым входом четвертого элемента И и счетным входом второго счетчика, соединенного выходом переноса с вторым входом второго элемента И и первым входом блока управления,, соединеного третьим выходом с вторым входом четвертого элемента И, соединенного вы- 40 ходом через второй делитель частоты со счетным входом третьего счетчика, соединенного выходом переноса с вторым входом блока управления, соединенного третьим выходом с первым вхо-45 дом пятого элемента И, четвертым выходом — с первым входом шестого эле-. мента И и вторым входом третьего элемента И, соединенного выходом через ,третий делитель частоты со счетным входом четвертого счетчика, соединенного информационными выходами с входами первого преобразователя возмущений, информационные выходы первого и второго счетчиков соединены соответ- 55 ственно с входами второго и третьего преобразователей возмущений, информационные выходы третьего счетчика соединены с входами четвертого преобразователя возмущений, выход первого инвертора соединен с вторым входом формирования импульсов, соединенного выходом с суммирующим входом сумматора, с вторыми входами пятого и шестого элементов И и третьим входом блока памяти, соединенного четвертыми и пятыми входами соответственно с ин формационными выходами первого и второго счетчиков, первыми выходами — с информационными входами сумматора, соединенного выходами с шестыми входами блока памяти, соединенного седьмым и восьмым входами соответственно с выходами пятого и шестого элементов И, вторым входом — с синхровходом сумматора, вторым и третьим выходами — с соответствующими управляю- щими входами второго коммутатора, четвертыми выходами — с входами цифроаналогового преобразователя, соединенного выходом с информационным входом второго коммутатора, соединенного тремя выходами с сответствующими сигнальными входами блока индикации, соединенного первым и вторым управляющими входами с выходами соответственно первого и второго элементов И.

2. Устройство по п.1, о т л и ч аю щ е е с я тем, что блок памяти содержит первый дешифратор адреса, соединенный входами с четвертыми входами блока памяти, выходами с первыми адресными входами накопителя, соединенного входом записи с выходом седьмого элемента И, соединенного первым входом с первым входом блока памяти и управляющим входом мультиплексора, вторым входом — с третьим входом . блока памяти, второй вход которого соединен с входом чтения накопителя, соединенного первыми, вторым и третьим информационными входами соответственно с шестыми, седьмым и восьмым входами блока памяти, вторыми адресными входами — с выходами второго дешифратора адреса, соединенного входами с пятыми входами блока памяти, первые и четвертые выходы которого соединены соответственно с первыми и вторыми выходами мультиплексора, соединенного информационными входами с выходами младших разрядов накопителя, выходы двух старших разрядов которого соединены соответственно с вторым и третьим выходами блока памяти.

1273853

Еыхад

Atmo к

Выход

C48m0uкп 7

Зиад

CVemVuка11

С

Jr э 3

3. Устройство по п.1, о т л и ч а— ю щ е е с.я тем, что блок управления содержит восьмой элемент И, соединенный выходом с S-входом первого триггера, первым входом с вторым входом блока управления, вторым входом— с инверсным выходом второго триггера и первым входом девятого элемента И, соединенного вторым входом с первым входом блока управления, выходом — 1О с Т-входом третьего триггера, соединенного R-входом через замыкающие контакты кнопки с шиной питания устВыход тептмиО 15 г

Еыход

7 И

8bi og

Та Z7

Выход

6ЛОк621

Я ®д 5

QfHH9 Pe Л ройства и непосредственно с R-входом ,,второго триггера и первым входом элемента ИЛИ, соединенного вторым входом с инверсным выходом третьего триггера и S-входом второго триггера,, выходом — с R-входом первого триггера, соединенного прямым выходом с третьим выходом блока управления, четвертый, первый и второй выходы которого соединены соответственно с прямым выходом третьего триггера, прямым выходом второго триггера и К-входом второго триггера.

1273853 файф.

Й/

РЖЯ

1273853 фив. 7

1273853

Ho 600ЯБ

С Юлока Я

Сиючутатора 4

С ЮлпюР1

glue. 3

Инцпориацион- 9пра8ляащее

НОГ /7оМ б70ЛГ

И7 7 г

Составитель В.Дворкин

Редактор Л.Пчелинская Техред JI.CåðäþKoâà Корректор Т.Колб

Заказ 6472/43 Тираж 728 Подписное

BHPHIIH Государственного комитета СССР по делам изобретений и открытий

113035, москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4