Устройство для измерения суточного хода часов

Иллюстрации

Показать всеРеферат

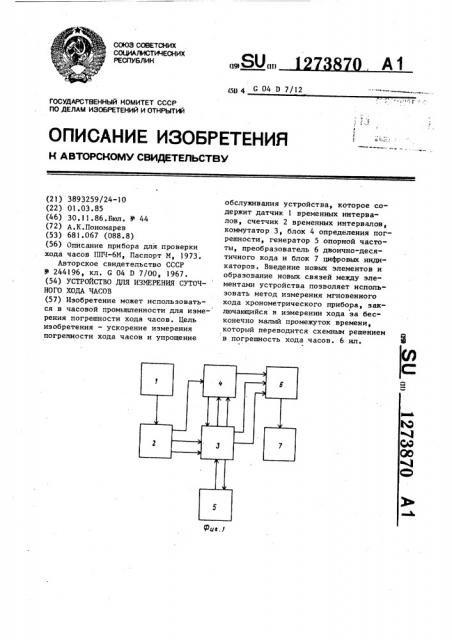

Изобретение может использоваться в часовой промьгошенности для измерения погрешности хода часов. Цель изобретения - ускорение измерения погрешности хода часов и упрощение обслуживания устройства, которое содержит датчик 1 временных интервалов , счетчик 2 временных интервалов, коммутатор 3, блок 4 определения погрешности , генератор 5 опорной частоты , преобразователь 6 двоично-десятичного кода и блок 7 цифровых индикаторов . Введение новых элементов и образование новых связей между элементами устройства позволяет использовать метод измерения мгновенного хода хронометрического прибора, заключающийся в измерении хода за бесконечно малый промежуток времени, который переводится схемным решением в погрешность хода часов. 6 ил. to О9 00

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (191 (11) (бц 4 G 04 D 7/12

OllHCAHHE ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3893259/24-10 (22) 01.03.85 (46) 30.11.86.Бюл. Р 44 (72) А.К.Пономарев (53) 681 ° 067 (088.8) (56) Описание прибора для проверки хода часов ППЧ-6М, Паспорт М, 1973.

Авторское свидетельство СССР

У 244196, кл. G 04 Р 7/00, 1967. (54) УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ СУТОЧНОГО ХОДА ЧАСОВ (57) Изобретение может использоваться в часовой промышленности для измерения погрешности хода часов. Цель изобретения — ускорение измерения погрешности хода часов и упрощение обслуживания устройства, которое содержит датчик 1 временных интервалов, счетчик 2 временных интервалов, коммутатор 3, блок 4 определения погрешности, генератор 5 опорной частоты, преобразователь 6 двоично-десятичного кода и блок 7 цифровых индикаторов. Введение новых элементов и образование новых связей между элементами устройства позволяет использовать метод измерения мгновенного хода хронометрического прибора, зак" лючаннцийся в измерении хода за бесконечно малый промежуток времени, который переводится схемным решением в погрешность хода часов. 6 ил.

273870 2 нератора 5 опорной частоты. Прямой

t0 венно, Устройство содержит датчик 1 временных интервалов, счетчик 2 временных интервалов с элементом 15, коммутатор 3, блок 4 определения погрешности, генератор 5 опорной частоты, преобразоватепь 6 двоично-десятичного кода в десятичный и блок 7 цифровых индикаторов.

Коммутатор состоит из SR-триггеров 8 и 9, элемента ЗИ-НЕ 10 элемента 2И-НЕ )il, элемента НЕ 12, элемента ЗИ-НЕ 13 и линии 14 задержки.

Вйход датчика I временных интервалов соединен с входом счетчика 2 временных интервалов. Первый выход счетчика 2 временных интервалов подключен к первому входу блока 4 определения погрешности, второй выход — к первому входу коммутатора 3, третий выход — к второму входу коммутатора 3, первый выход которого соединен с вторым входом блока 4 определения погрешности, второй выход — с третьим входом блока 4 определения погрешности, первым выходом подключенного к четвертому входу коммутатора 3.

Выход генератора 5 опорной частоты соединен с третьим входом коммутатора 3, а второй выход блока 4 опредеФ ления погрешности подключен к первому входу преобразователя 6 двоичнодесятичного кода в десятичный. Выход преобразователя 6 соединен с входом блока ? цифровых индикаторов. Третий выход коммутатора 3 подключен к второму входу преобразователя 6, четвертый выход коммутатора 3 — . третьему входу преобразователя 6, Пятый выход коммутатора 3 подключен к входу re40

1,1

Изобретение относится к приборостроению и может быть использовано в часовой промышленности и в ремонтных часовых мастерских для измерения погрешности хода часов.

Цель изобретения - ускорение измерения погрешности хода часов и упрощение обслуяшвания устройства.

На фиг. 1 представлена блок-схема устройства; на фиг.2 — принципиальная схема коммутатора; на фиг.

3 — схема счетчика временных интер" валов; на фиг. 4 — 6 — временные диаграммы, иллюстрирующие работу устройства при частоте колебаний баланса измеряемых часов, равной эталонной частоте, а также меньшей или большей эталонной частоты соответствыход SR-триггера 8 соединен с вторым входом элемента ЗИ-НЕ 10 и вторым входом элемента ЗИ-НЕ 13. Инверсный выход SR-триггера 8 соединен с входом линии !4 задержки, а прямой выход SR-триггера 9 подключен к первому входу элемента ЗИ-НЕ 10. Инверсный выход SR-триггера 9 соединен с третьим входом элемента

ЗИ-НЕ 13, а выход элемента 2И-НЕ ll подключен к R-входу SR-триггера 9.

Выход элемента НЕ 12 соединен с вторым входом элемента 2И-НЕ ll a

S-вход SR-триггера 8 подключен к

S-входу SR-триггера 9 и является первым входом коммутатора 3, R-вход

SR-триггера 8 является вторым входом коммутатора 3, а инверсный выход

SR-триггера 8 является пятым выходом коммутатора 3. Третий вход элемента

ЗИ-НЕ 10 соединен с-первым входом элемента ЗИ-НЕ 13 и входом элемента

НЕ 12 и является третьим входом коммутатора 3. Первый вход элемента

2И-НЕ 11 является четвертым входом коммутатора 3 выход элемента ЗИ-НЕ

10 — первым выходом коммутатора 3, выход элемента ЗИ-НЕ 13 — вторым выN ходом коммутатора 3, прямой выход

SR-триггера 9 — третьим выходом коммутатора 3, выход линии 14 задержки — четвертым выходом коммутатора 3.

Устройство работает следующим образом.

При частоте колебаний баланса, равной эталонной (фиг.4) первый выделенный импульс баланса часов с выхода датчика 1 временных интервалов (от часов, положенных на датчик 1) поступает на вход счетчика 2 временных интервалов (кривая 1, t О), а с первого выхода счетчика 2 временных интервалов напряжение 0" поступает на первый вход блока 4 определения погрешности (кривая 17, = О), записывая в него значения двоично-десятичного кода интервала эталонного времени. Этот код равен

86400 (1000 0110 0100 0000 0000) и представляет собой число секунд в сутках. Значение его по времени равно интервалу между вторым и седьмым импульсами баланса часов (фиг.4).

Второй выделенный импульс баланса часов, поступивший на вход счетчика 2 временных интервалов (кривая

16, t = 0,2 с) поступает с второго з 1273870 выхода счетч ка 2 ика 2 временных интер- с = 0,2 с о

4 валов в виде напряжения "0" с до t 1,2 с). В блоке 4 выи вход коммутатора 3 (к ия иа пер- определения погрешности начинается а (кривая 18, уменьшение в

0,2 с) и переключает SR-т (вычитание) з аписанного ры 8 и 9. При этом напряжение "1" чает -тригге- кода эталонного в ремени, которое с прямого выхода БК- триг 8 ряжение 1 стремится к н лю у . На выходе элеменриггера 8 пос- та ЗИ-НЕ 13 тупает на вторые вхо ды элементов "1" (21 присутствует напряжение

ЗИ-НЕ 10 и 13, а напряже "!" кривая 21),так как на первый прямого выхода SR-тригге а 9 яжение с вхо элем д мента ЗИ-НЕ 13 поступает "0"

С поступлением с пает на первый вход элемента ЗИм седьмого импульса бамента И-НЕ 1О ланса часов на в

10. С инверсного выхода SRа вход счетчика 2 врера 9 напряжение "0"

-тригге- менных и поступает на 1,2 с) нат нтервалов (кривая 16

1 третий вход элемента ЗИ-НЕ 13 с) на третьем выходе счетчиинверсного выхода RS-т а с ка 2 временных р ных интервалов появится

-триггера 8 напряжение "0" (пятый выход коммутато а 3) которое поступает ора ) на вход 1$ на второй вхо ко генератора 5 опорной час и частоты носту- вая 22 од коммутатора 3 (крипает напряжение "0" (к

1,2 с) и переключает кривая 26, SR»òðèããåð 8. С п а 0,2 с), включив гене ато 5 прямого выхода SRГенератор 5 опорной част нератор .. триггера 8 на пряжение 0 поступит стоты сос- на второй вхо тоит из задакицего генерато и вход элемента ЗИ-НЕ 10 и тота которого стабил ратора, час- 20 вто ой вх илизирована квар- Напряжение р " од элемента ЗИ-НЕ 13 цевым резонатором и делит еля часто- да SR-т и апряжение "!" с инверсного выхоты.

-триггера 8 поступает через

3 аданаии генератор генерирует пятый Выход Ко т мму атора 3 на вход импульсы с частотой повторения генератора 5 о порнои частоты и запре"

8640 кГц. Для того чтобы

2S щает пост пл тупление импульсов опорной

У ы на выходе частоты на т генератора 5 опорной частоть полу- 3 (й 12

ы на третий вход коммутатора чить частоту 86,4 кГц, т.е. 86400 (,2 с, кривые 26 и 19). Отколебаний за 1 с интервал рвала эталонно- ты п и ключение генератора 5 опорной ча частого времени импульсы с выхода задаю- щ блоке 4 оп е ты происходит в момент когда в щего генератора поступают на на вход ется ко н локе определения погрешности ост— тaделителя частоты, состояще я код нулевой погрешности. Нал

° апря» соединенных последовательно двоичжение с первого входа блока 4 но-десятичных счетчиков с общим коопределения погрешности поступает фф К = 100 П этом в выход старшего счетчика являетри вая 23, — I 2 с), это вызывает леся в ыходом генератора 5 опо ной а являет- реключение SR-триггера 9, так как в тоти. орно час- этот мо о но - мент времени на выходе элеЧ астота колебаний генератора 5 мента НЕ 12 присутствует напряжение .опорной частоты выбрана тако" а такои,,что 40 Напряжение " "0 " с цена деления младшего разряд ие с прямого выхода чиков с ена зряд р посту ет чер з рет и зряда счет- $К-тригге а 9 хо а решности выход комп т рети ода часов. Второй вход блок 4 а on- п еоб ммутатора 3 на второй вх ределения погрешност од и является вычи- 1,2 с). Ко + р разователя 6 (кривая 25

Э тающим входом счетчика, а третий с . Код + нулевой погрешности вхо бл д блока 4 определения пог е третин с второго выхо а .ода блока 4 определения ти - входом прямого сче погрешнос- погрешности о та. преобразователя 6 в поступает на первый

После я двоично-де сятичнооследовательнос HMIIjjJIbco тотой ьсов часа с четвертого поступает

400 выход линии 14 упает с выхода генератора 5 опо -5О ной частоты на т на т ет поступает

ЗИ-НЕ 10 а третий вход элемента ретии вход преобразов 6 и первый вход элемента (кривая 24, t = I 2 с) ет ателя 6

ЗИ-НЕ 13 (на т — с), занеся в опе(ка третий вход коммутаторативную память код + ра 3). Эт нулевой погти импульсы через тре решности. вхо и в третин т д и выход элемента ЗИ-НЕ 10 упают с первого выхода ко пос- SS Этот ко д, преобразованный в десяда коммутато тичное значе ра 3 на второй вход б 4 ние, поступает с выхолока 4 опреде- дапеоб а ления погрешности (кривая 20, от 7 Ф

4 рео разователя 6 на вход блок ока ци ровых индикаторов, Оператор про5 12 читывает на цифровых индикаторах блока 7 информацию, соответствующую нулевой погрешности хода часов.

В состав преобразователя 6 двоично-десятичного кода в десятичный входят дешифраторы и D -триггеры, При этом выходы З -триггеров соединены с входами дешифраторов, З -триггеры выполняют функцию оперативной памяти, что исключает мелькание показаний на индикаторах блока 7 во время измерения хода часов, Вторым входом преобразователя 6 является

Г-вход З -триггера, имеющего как прямой, так и инверсный выходы. Выходы

В-триггера подключены к входам высоковольтных ключей, Данный З -триггер яужит для запоминания и индицирования знака погрешности в конце цикл,". измерения. -входы остальных

3-триггеров объединены и являются третьим входом преобразователя 6 двоично-десятичного кода в десятичный. Код погрешности с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 6 (D-входы 7 -триггеров}.

При подаче на третий вход преобразователя 6 напряжения "1" (кривая 24, t = 1,2 с на фиг.4; t = 1,2 с на фиг,5; t. = =1,2 с на фиг. 6), код и знак погрепплости заносится в оперативную память, Преобразованный дешифраторами из двоично-десятичного кода и цесятичныи код и знак погрешности поступает с выхода преобразователя 6 на вход блока 7 цифровых индикаторов.

На фиг. 5 представлены временные диаграммы работы устройства, когда период колебания баланса часов меньше эталонного. С поступлением седьмого импульса баланса часов на вход счетчика 2 временных интервалов (кривая 16, t 1 2 с) на третьем выходе счетчика 2 временных интервалов появляется напряжение "0", которое поступает на второй вход коммутатора 3 (кривая 22, t « 1,2 с) и переключает SR-триггер 8. Это вызывает запрещение поступления импульсов через первый выход коммутатора 3 на второй вход блока 4.

Напряжение 1 1" с пятого выхода коммутатора 3 (кривая 26, t<1,2 с) ,вызывает запрещение поступления импульсов опорной частоты на третий вход комчутатора 3 (кривая 19, 73870 Ь

З5

5 !

О

t «1,2 с). В блоке 4 определения погрешности остается код погрешности, который с второго выхода блока 4 определения погрешности поступает на первый вход преобразователя 6 двоично-десятичного кода в десятичный.

На второй вход преобразователя 6 с третьего выхода коммутатора 3 поступает напряжение "1" (кривая 25, t « 1,2 с), определяющее знак погрешности.

С четвертого выхода коммутатора 3 напряжение "1" поступает на третий вход преобразователя 6 двоично-десятичного кода в десятичный (кривая

24, t « 1,2 с), записав в оперативную память код и знак "+" погрешности. С выхода преобразователя 6 десятичное значение и знак погрешности поступает на вход блока 7 цифровых индикаторов.

Оператор прочитывает на цифровых индикаторах блока 7 числовое значение погрешности хода часов со знаком "+".

На фиг. 6 приведены временные диаграммы работы устройства, когда период колебания баланса часов больше эталонного, В этом случае нулевой код в блоке 4 определения погрешности появляется раньше поступления седьмого импульса баланса часов.

В момент появления нулевого кода в блоке 4 определения погрешности на первом выходе блока 4 появляется напряжение "1" (кривая 23, t = 1,2 с), которое поступает через четвертый вход коммутатора 3 на первый вход элемента 2И-НЕ 1!. Импульс опорной частоты своим отрицательным перепадом (кривая 19, t = 1,2 с) переводит элемент НЕ 12 в состояние "1". !!а выходе элемента 2И-НЕ 11 появляется напряжение "0"> которое переключает SR-триггер 9, Напряжение "0" на прямом выходе SR-триггера 9 запрещает прохождение импульсов опорной частоты через элемент ЗИ-НЕ 10.

На первом выходе коммутатора 3 присутствует напряжение "1" (кривая

20, = 1,2 с}. Напряжение "1" на инверсном выходе SR-триггера 9 разрешает прохождение импульсов опорной частоты через логический элемент

ЗИ-НЕ 13, Эти импульсы опорной частоты с второго выхода коммутатора 3 (кривая 21, 1,2 с) поступают на

73870

15

25

7 12 третий вход блока 4 определения погрешности, записывая код погрешности.

С поступлением седьмого импульса баланса часов на входе счетчика 2 временных интервалов (кривая 16, ) 1,2 с) на третьем выходе счетчика 2 временных интервалов появляется напряжение "0", которое поступает на второй вход коммутатора 3 (кривая 22, t)1,2 с) и переключает

SR-триггер 8. Напряжение "0" с прямого выхода SR-триггера 8 поступает на вторые входы элементов 3И-HE 10 и 13. Это вызывает прекращение пос,тупления импульсов опорной частоты с второго выхода коммутатора 3 на третий вход блока 4 (кривая 21, t 7>I 2 с). С инверсного выхода SRтриггера 8 напряжение "1" поступает через пятый выход коммутатора 3 на вход генератора 5 опорной частоты (кривая 26, t > 1,2 с). Это вызывает прекращение поступления импульсов опорной частоты на третий вход коммутатора 3 (кривая 19, t l 2 с).

Записанный в блоке 4 определения погрешности код погрешности поступает с второго выхода блока 4 определения погрешности на первый вход преобразователя 6 двоично-десятичного кода в десятичный. На второй вход преобразователя 6 с третьего выхода коммутатора 3 поступает напряжение

"0" (кривая 25, t ) 1,2 с). С четвер-З5 того выхода коммутатора 3 напряжение

")" поступает на третий вход преобразователя 6 двоично-десятичного кода в десятичный (кривая 24, t l,2 с), записав в оперативную память код и знак "-" погрешности. Десятичное значение кода и знак погрешности с выхода преобразователя 6 поступают на вход блока 7 цифровых индикаторов.

Оператор прочитывает на цифровых 45 индикаторах блока 7 числовое значение погрешности хода часов со энаВосьмой импульс баланса часов со- 50 ,ответствует первому импульсу нового цикла измерения, Через каждый 1,4 с данные автоматически обновляются.

В предлагаемом устройстве используется метод измерения мгновенного хода хронометрического прибора, заключающийся в измерении хода за бесконечно малый промежуток времени, которое переводится схемным решением в погрешность хода часов. Этот бесконечно малый промежуток времени в предлагаемом устройстве равен 2,5 периода колебаний баланса часов,что составляет 1 с.

Формула изобретения

Устройство для измерения суточного хода часов, содержащее датчик временных интервалов, генератор опорной частоты и преобразователь двоично-десятичного кода в десятичный, соедиченный своим выходом с входом блока цифровых индикаторов, о т л и ч а ю щ е е с я тем, что, с целью ускорения измерения и упрощения обслуживания, в него введены счетчик временных интервалов, коммутатор и блок определения погрешностей, причем выход датчика временных интервалов соединен с входом счетчика временных интервалов, первый выход которого подключен к первому входу блока определения погрешности, соединенного своим первым выходом с четвертым входом коммутатора, второй и третий выходы счетчика временных интервалов подключены соответственно к первому и второму входам коммутатора, первый и второй выходы которого соединены соответственно с вторым и третьим входами блока определения погрешности, подключенного своим вторым выходом к первому входу преобразователя двоично-десятичного кода в десятичный, второй и третий входы соединены соответственно с третьим и четвертым входами коммутатора, пятый выход которого подключен к входу генератора опорной частоты, соединенного своим выходом с третьим входом коммутатора.

327ЭВ70.1273870 рир.в

Составитель С.Шакин

Техред Л.Олейник

Корректор М. Шароши

Редактор Л. Пчелинская

Заказ 6474/44

Тираж 398 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

uZ u4 аИ ОЮ rO 1Z М С абие 4 и

Л

У г

1В г