Преобразователь длительности импульса в код

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной и вычислительной технике и может быть использовано в кодирующих устройствах , в системах автоматического управления и других областях радиоэлектроники . Целью изобретения является уменьшение времени преобразования длительности импульса в код. Цель достигается введением п-1 цепей преобразования , в каждую из которых, кроме последней, введены элементы И 5, 6, устройство также содержит в каждой Цепи элемент ИЛИ 1, линию 2 задержки, элемент ИЗ, триггер 4. Устройство обладает временем преобразования ,- равным суммарному значению величин задержек линий задержек, и равно диапазону преобразования, что ПО сравнению с известным дает вьмг (Л рьнп в 128 раз. ШйТ

СОКИ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

OllHCAHHE ИЗОБРЕТЕНИЯ

Н А ВТОРСНОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3887563/24-21 (22) 22.04.85 (46) 30.11.86. Бюл. №- 44 (71) Объединенный институт ядерных исследований (72) Ю.Г.Будяшов (53) 681.325.3{088.8) (56) Карпов Н.P. Рециркулярный измерительный преобразователь коротких временных интервалов в код. — Приборы и техника эксперимента, 1980, И 2, с. 101

Авторское свидетельство СССР

¹ 708293, кл. С 04 F IO/04, 1977, (54) ПРЕОБРАЗОВАТЕЛЬ ДЛИТЕЛЬНОСТИ

ИМПУЛЬСА В КОД (57) Изобретение относится к импульсной и вычислительнойфтехнике и может

„„SU„„12738 2 А1 (gg 4 G 04 F 10/04, Н 03 М 1/00, 1, быть использовано в кодирующих устройствах, в системах автоматического управления и других областях радиоэлектроники. Целью изобретения является уменьшение времени преобразования длительности импульса в код. Цель достигается введением n-I цепей преобразования, в каждую из которых, кроме последней, введены элементы

И 5, 6, устройство также содержит в каждой цепи элемент ИЛИ 1, линию 2 задержки, элемент И 3, триггер 4.

Устройство обладает временем преобразования,равным суммарному значению величин задержек линий задержек, и равно диапазону преобразования, что ,по сравнению с известным дает выигрыш в 128 раз.

1273872

Изобретение относится к импульсной и вычислительной технике и может быть использовано в кодирующих устройствах, в системах автоматического управления, в измерительной технике и других областях радиоэлектроники.

Цель изобретения — уменьшение времени преобразования длительности импульса в код до величины диапазона преобразования преобразователя путем введения и цепей поразрядного взвешивания и соответствующими линиями задержки.

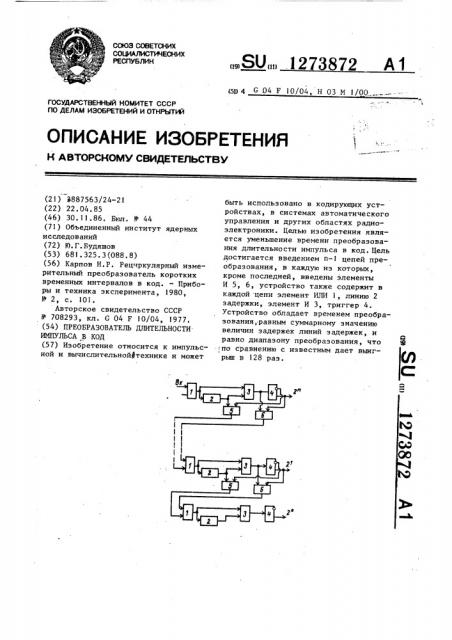

На чертеже показана функциональная схема преобразователя.

Преобразователь содержит и цепей преобразования, каждая из которых содержит двухвходовый элемент ИЛИ 1, элемент задержки (ЭЗ) 2, двухвходовый элемент И 3, триггер 4 и двухвходовые элементы И 5 и 6. Последняя и-я цепь преобразования элементов И

5 и 6 не содержит. Один из входов элемента ИЛИ подключен,к входной шине, а его выход — к первому входу элемента И и входу линии задержки, выход которой подключен к второму входу элемента И, при этом в каждой (n-1)-й цепочке выход элемента И подключен к входу триггера и первому входу второго элемента И, второй вход которого подключен к прямому выходу триггера, aего инверсный выход - к второму входу первого элемента И, первый вход которого соединен с выходом линии задержки, выходы первого и второго элементов И подключены, соответственно к первому и второму входам элемента ИЛИ каждой следующей цепочки, причем длительность задержки каждой из линий задержки уменьшается в два раза в порядке следования цепочек преобразования, прямые выходы триггеров и цепочек преобразования подключены к N выходным разрядным шинам.

Преобразователь работает следующим о бр аз ом.

Входной сигнал преобразуемой длительности „ подается на вход элемента ИЛИ 1. С выхода элемента ИЛИ 1 сигнал поступает на один вход элемента И 3 непосредственно, а на другой— через элемент 2. Величина задержки должна с6ответствовать временной цене разряда двоичного кода преобразования.

5

Если длительность входного импульса больше величины задержки элемента .

2, то на выходе элемента И 3 появляется импульс, длительность которого уменьшена на величину задержки элемента 2, т.е. t„ t . Срабатывает триггер 4. Таким образом, в этом разряде кода появляется "1", а выходной сигнал с прямого выхода триггера 4 открывает элемент И 6, с выхода которого импульс подается на вход следующей цепочки.

Если длительность входного импульса t меньше длительности задержки, то .на выходе элемента И 3 импульс отсутствует. Триггер 4 не срабатывает и в этом разряде кода фиксируется

"О". Импульс через открытый элемент

И 5 с выхода элемента 2 без укорачивания поступает на вход элемента

ИЛИ 1 следующей цепочки.

Импульсы аналогично проходят по следующей цепи и т.д. до последней.

В результате последовательного прохождения входным импульсом всех цепей триггеры каждой из цепочек находятся в состоянии "1" или "О" в зависимости от того, больше или меньше длительность импульса на входе цепи величины задержки этой цепи. Состояния триггеров каждой цепи соответствуют значениям разрядов полученного двоичного кода преобразования длительности входного импульса. Триггер первой цепочки соответствует старшему разряду кода.

Время преобразования равно суммарному значению величин задержек ЭЗ и равно диапазону преобразования преобразователя.

Формула изобретения

Преобразователь длительности импульса в код, включающий цепочку преобразования, содержащую элементы ИЛИ, И и линию задержки, выход которой подключен к второму входу элемента

И, а вход — к первому входу элемента

И и выходу элемента ИЛИ, один из входов которого подключен к входной шине, отличающийся тем, что, с целью уменьшения времени преобразования, в него введено со второй по и-ю цепочек преобразования, где и равно числу разрядов двоичного кода устройства, при этом в и-ю цепочку преобразования введен триггер, Составитель В.Герасимов

Техред Л.Олейник Корректор М.Шароши

Редактор Л.Пчелинская

Тираж 398 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

)13035, Москва, Ж-35, Pàóøñêàÿ наб., д. 4/5

Заказ б474/44

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

3 12738 соединенный с выходом элемента И, а в остальные (n-!) цепочки преобразования введены триггер и первый и второй элементы И, причем в каждой (и-!)-й цепочке выход элемента И под- ключен к входу триггера,и первому входу второго элемента И, второй вход которого подключен к прямому выходу триггера, а его инверсный выход подключен к второму входу первого эле- 10 мента И, первый вход которого подклю72 4 чен к выходу линии задержки, выходы первого и второго элементов И нодклю" чены соответственно к первому и вто" рому входам элемента ИЛИ каждой следующей цепочки, причем длительность задержки . каждой из линий задержки уменьшается в два раза в порядке следования цепочек преобразования, прямые выходы триггеров и цепочек преобразования подключены к N выходным разрядным шинам.