Устройство для анализа частоты использования блоков информации в вычислительных комплексах

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к устройствам для анализа информации, и может быть использовано при проектировании быстродействующих вычислительных комплексов. Целью изобретения является повышение быстродействия введения анализа частоты использования блоков памяти вычислительного комплекса. Устройство содержит генератор импульсов, с первого по третий блоки счетчиков, регистр, дешифратор, первый, второй триггеры, первый, второй блоки элементов И, элемент И, с первой по третью группы блоков элементов И, блок элементов ИЛИ, первый, второй элементы задержки. Устройство анализирует частоту использования блоков как оперативной, так и внешней пас мяти с целью их оптимального перераспределения для повышения произ (Л водительности вычислительного комплекса . 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) (51) 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTOPCH0MY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3917674/24-24 (22) 26.06.85 (46) 30.11.86. Бюл. И - 44 (72) Н.П.Бакров, В.В.Мазаник и М.С.Баранов (53) 681 . 3 (088. 8) (56) Авторское свидетельство СССР

В 881722, кл. G 06 F 3/04, 1981.

Авторское свидетельство СССР

)Ф 885987, кл. G 06 F 3/02, 1981. (54) УСТРОЙСТВО. ДЛЯ АНАЛИЗА ЧАСТОТЫ

ИСПОЛЬЗОВАНЙЯ БЛОКОВ ИНФОРМАЦИИ В

ВЫЧИСЛИТЕЛЬНЫХ КОМПЛЕКСАХ (57) Изобретение относится к области вычислительной техники, в частности к устройствам для анализа информации, и может быть использовано при проектировании быстродействующих вычислительных комплексов.

Целью изобретения является повышение быстродействия введения анализа частоты использования блоков памяти вычислительного комплекса. Устройство содержит генератор импульсов, с первого по третий блоки счетчиков, регистр, дешифратор, первый, второй триггеры, первый, второй блоки элементов И, элемент И, с первой по третью группы блоков элементов И, блок элементов ИЛИ, первый, второй элементы задержки. Устройство анализирует частоту использования блоков как оперативной, так и внешней памяти с целью их оптимального перераспределения для повышения производительности вычислительного комплекса. 1 ил.

1273937

Изобретение относится к вычислительной технике, в частности к устройствам для анализа информации, и может быть использовано при проектировании быстродействующих вычислительных комплексов.

Цель изобретения — повышение быстродействия ведения анализа частоты использования блоков памяти вычислительного комплекса.

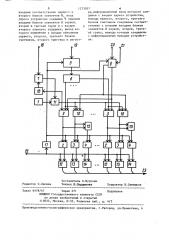

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит генератор 1 импульсов, первый, второй и третий блоки 2, 3, 4 счетчиков, регистр 5, дешифратор 6, первый и второй триггеры 7 и 8, первый и второй блоки элементов И 9, 10 элемент И ll первую, вторую и третью группы блоков элементов И 12 — 14, блок !5 элементов ИПИ, первый и второй элементы 16 и 17 задержки, вход 18 запуска устройства, вход 19 адреса блока памяти устройства, первый, второй входы 20 и 21 идентификации блока памяти устройства, вход 22 сброса устройства, информационный выход 23 устройства.

Устройство работает следующим образом.

В исходном состоянии регистр 5, счетчики 2 — 4, триггеры 7 и 8 обнулены. По входу !9 в регистр 5 заносится код А адреса блока информа" ции, по входу 18 триггер 7 устанавливается в единичное состояние, триггер 8 устанавливается по левому (по схеме) входу 20 в единичное состояние, если соответствующий блок информации хранится во внешней памяти, и по правому входу 20 в нулевое состояние, если соответствующий блок информации хранится в оперативной памяти.

Если триггер 8 установлен в единичное состояние, то импульс с генератора l проходит через элемент И l l, А-й элемент И 9и увеличивает содержимое А-х счетчиков 2 и 4 (А-.й счетчик 4 определяет общее количество обращений к А-му блоку информации, счетчик

2 — если А-й блок хранится во внешней памяти, счетчик 3 — соответственно в оперативной. памяти). Если триггер 8 установлен в нулевое состояние, то импульс с генератора 1 увеличивает содержимое А-х счетчиков 3 и 4. Импульс с выхода элемента И 11

10 через элемент 16 задержки обнуляет триггер 7. При очередном поступлении кода адреса блока информации в регистр 5 триггер 7 по входу 18 устанавливается в единичное состояние и указанный процесс повторяется. После анализа всех блоков информации по входу 21 поступает сигнал, который . разрешает выдачу содержимого счетчиков 2 — 4 на выход 22 устройства и через элемент 17 задержки обнуляет регистр 5 и триггер 8. На этом работа устройства заканчивается.

Формула изобретения

Устройство для анализа частоты использования блоков информации в вычислительных комплексах, содержащее

20 генератор импульсов, первый, второй и третий блоки счетчиков, дешифратор, первый, второй блоки элементов И, блок элементов ИЛИ, элемент И и регистр, причем выход генератора импульсов подключен к первому входу элемента И, выход регистра соединен с входом дешифратора, выход которого подключен к первым входам первого и второго блоков элементов И, выход первого блока элементов И соединен с

30 первым входом блока элементов ИЛИ, второй вход которого соединен с выходом второго блока элементов И, выходы первого и второго блоков элементов И соединены со счетными вхо35 дами соответственно первого и второго блоков счетчиков, выход блока элементов ИЛИ подключен к счетному входу третьего блока счетчиков, о т л и40 ч а ю щ е е с я тем, что, с целью повышения быстродействия, в него введены первый, второй триггеры, первая, вторая, третья группы блоков элементов И, первый, второй элементы задержки, причем вход запуска устрой45 ства соединен с единичным входом первого триггера, единичный выход и нулевой вход которого соединены соответственно с вторым входом элемента И и с выходом первого элемента задержки, выход элемента И соединен с вторыми входами первого и второго блоков элементов И и с входом первого элемента задержки, первый, второй входы идентификации блока памяти устройства соединены соответственно с единичным и нулевым входами второго триггера, единичный и нулевой выходы которого соединены с третьими

1273937 4 ра,информационный вход которого соединен с входом адреса устройства, выходы первого; второго, третьего блоков счетчиков соединены соответственно с вторыми входами блоков элементов И первой, второй, третьей групп, выходы которых соединены. с информационным выходом устройства. входами соответственно первого и второго блоков элементов И, вход сброса устройства соединен с первыми входами блоков элементов И первой, второй и третьей групп и с входом второго элемента задержки, выход которого подключен к входам обнуления первого, второго, третьего блоков счетчиков, второго триггера и регист20

Составитель С.Бурухин

Техред Л.Сердюкова

Редактор С.Лисина

Корректор В.Синицкая

Заказ 6478/47 Тираж 67) ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

1!3035, Москва, 7<-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г.ужгород, ул.Проектная, 4