Устройство для вычисления коэффициентов фурье

Иллюстрации

Показать всеРеферат

Изобретение относится к специализированным средствам вычислительной техники, ;предназначе1 о для определенйя козффициентов дискретного преобразования Фурье периодических сигналов при работе в реальном масштабе времени. Цель изобретения упрощение устройства. Поставленная цель достигается за счет того, что устройство для вьмисления козффици- . ентов Фурье содержит блок управления I, блоки 2., 2,j постоянной памяти, накапливающие сумматоры 3. - 3 и аналого-цифровой преобразователь 4, а блок управления - триггер 5, генератор 6 тактовых импульсов, элемент 7 И, злемент 8 задержки, счетчик 9, в регистр 10, сумматор 12 по модулю два, сумматор 11. 1 ил.. 10 СО со

СОЮЗ СОВЕТСНИХ

СОЩИАЛИСТИЧЕСНИХ

РЕСПУБЛИН ()9) (И) 44 А1 (51)4 G 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, В 1

1 е

К АВТОРСКОМ .Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ГО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITPM (21) 3884707/24-24 (22) 17.04.85 (46) 30.11.86. Бюл. У 44 (71) Ордена Ленина институт кибернетики им. В.М. Глушкова (72) В.П. Боюн и А.Н. Головин (53) 681.32 (088.8) (56) Авторское свидетельство СССР

Ф 537349, кл. G 06 F )5/332, 1976.

Смирнов Ю.М. и др. Проектирование специализированных информационно-вычислительных систем. М.: Высшая школа, )984, с. 96, рис. 3.1.2. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОЭФФИЦИЕНТОВ ФУРЬЕ (57) Изобретение относится к специализированным средствам вычислительной техники, предназначено для опреLделенИя коэффициентов дискретного преобразования Фурье периодических сигналов при работе в реальном масш- табе времени. Цель изобретения— упрощение устройства. Поставленная цель достигается за счет того, что устройство для вычисления коэффициентов Фурье содержит блок управления

1, блоки 2., 2 постоянной памяти, накапливающие сумматоры 31 — 3 и аналого-цифровой преобразователь 4, а блок управления — триггер 5, генератор 6 тактовых импульсов, элемент

7 И, элемент 8 задержки, счетчик 9, регистр 10, сумматор 12 по модулю два, сумматор 11. I ил.

1273944

Изобретение относится к специализированным средствам вычислительной техники, предназначено для определения коэффициентов дискретного преобразования Фурье периодических сигналов при работе в реальном масштабе времени.

Цель изобретения — упрощение устройства.

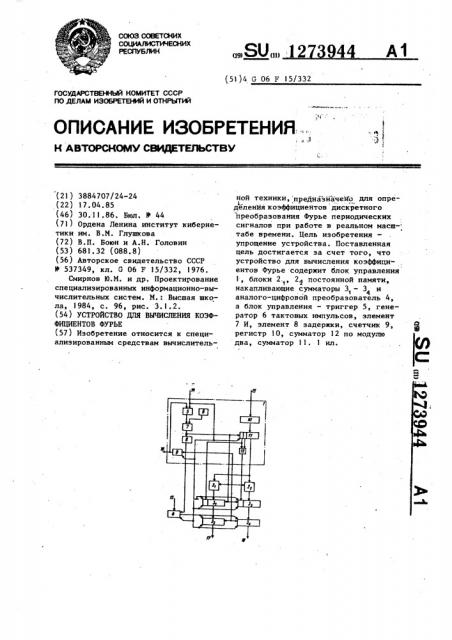

На чертеже приведена схема предлагаемого устройства °

Устройство содержит блок 1 управления, первый 21 и второй 2. блоки постоянной памяти, первый 3, второй, 3, третий 3> и четвертый 3, накапливающие сумматоры и аналого-цифровой преобразователь 4.

Блок управления содержит триггер

5, генератор 6 тактовых импульсов, элемент И 7, элемент 8 задержки (триггер типа D) счетчик 9, регистр

10, сумматор ll, сумматор !2 по модулю два, информационный вход 13 устройства, вход 14 запуска, вход 15 задания гармоник, выход 16 готовности результата, выходы 17 и 18 мнимой ,и действительной частей результата соответственно.

Устройство работает. следующим обр àçом.

По сигналу, поступающему. на вход

14 запуска устройства, происходит установка в единичное состояние триггера 5 и в начальное состояние счетчика 9, сумматора ll блока управления аналого-цифрового преобразователя 4 следящего типа и накапливающих сумматоров 3 -34, причем начальное состояние первого 3 и второго 3

"накапливающих сумматоров равно соответственно значению (-зЫО) О, (-соз 0)=-1 в дополнительном коде.

На вход 15 задания гармоник блока управления поступает двоичный код номера гармоники, который записывается в регистр 10. Разрядность регистра 10 должна быть не меньше log K где К вЂ” максимальный номер гармоники.

Аналоговый сигнал х (t) поступает на вход 13 аналого-цифрового преобразователя 4. Импульсы с выхода генератора 6 тактовых импульсов через элемент И 7 поступают на тактовые входы сумматора 11 блока 1 управления, первого 3 и второго 3 накапливающих сумматоров и на вход элемента 8 задержки. По этому сигналу содержимое регистра 10 прибавляется

5

25 к содержимому сумматора 11 и содержимое из первого 2, и второго 2 блоков памяти поступает на входы накапливающих сумматоров Э, и 3 за исключением первого такта работы устройства, когда содержимое накапливающих сумматоров 3< и Э не изменяется. Спустя один такт по сигналу с выхода элемента 8 задержки осуществляется наращивание счетчика 9., преобразование входного сигнала х (t) из аналоговой формы в дискретную аналого-цифровым преобразователем 4 и прием информации из накапливающих сумматоров 3 и 3 в накапливающие сумматоры 3 и 3 соответственно.

Разрядность сумматора ll и счетчика 9 блока управления равна Log N.

Если на выходе приращения аналогоцифрового преобразователя 4 значение сигнала равно "1" (Величина приращения входного сигнала положительная), содержимое накапливающих сумматоров 3, и 3 прибавляется к содержимому накайливающих сумматоров

3 и 34.

Если на выходе приращений аналого" цифрового преобразователя значение сигнала равно "0" (величина приращения входного сигнала отрицательная), содержимое накапливающих сумматоров

3 и 3 вычи л ется иэ содержимого накапливающих сумматоров,35 »< . Выходы накапливающих сумматоров 3, и

3 подключены к входам накапливающих сумматоров 3 и 3» со сдвигом на

r разрядов в сторону младших разрядов. В первом блоке 2 памяти записаны значения i = sirl(1 ° Au)), а во втором блоке 2 памяти — значения

Ф Ф

=сов(14ч>) в интервале аргумента этих функций lO- /43, где 10,1, 2,..., ((Н-1)/4)- номера отсчетов, =Т/N — интервал дискретизацйи по времени; д- частота основной гармоники.

Определение знаков з п(хвое) и соз(ЫЙ), где i=0,1,2,..., Б-! номера отсчетов, осуществляется с помощью сумматора 12 по модулю два и двух старших разрядов сумматора Il блока 1 управления, которые определяют номер квадранта аргумента функций sin(ia>) и соз(Ы ). Остальные разряды сумматора ll блока управле" ния определяют адрес значения

sin(i а1) ипи cos(i au3 ) в соответствующем блоке памяти.

1273944

N-1 где $ = ъ| (| | |„б u3 ), 1 у 0 N j

tn =К б

n eM S„S„, -sin(m, и) ), S =0.

-$$

По достижении заданного числа отсчетов, равного N, на выходе переполнения счетчика 9 появляется сигнал, свидетельствующий о том, что в накапливающих сумматорах 3 и .3 на3 4 коплено истинное Значение коэффициентов дискретного преобразования

Фурье. С выхода переполнения счетчика 9 сигнал поступает на нулевой вход триггера 5 и выход 16 готовнос- о ти результата устройства. Частота дискретизации входного сигнала x (t), поступающего на вход 13 устройства, равна частоте генератора 6 тактовых импульсов.

Алгоритм работы предлагаемого устройства своцится к следующему.

Приращения д х входного сигнала в каждом такте работы устройства оп.ределяются .соотношением, 2О дх "х.,-х. Sign jx(t)-х„).2 где х.,х. — отсчеты входного сигнаJ1 б ла x(t) в (g- 1)-ом и ,)-ом тактах работы уст|$ ройства;

-| — -единица младшего разряда; — раз рядно с ть аналого-цифрового преобразователя 4. 30

Коэффициенты ДПФ равны:

N-1

4(к>)= х, cps(.ь к), .|=0

Ь(к|)) = x.i з|и(1. к, 3$

i-0, где К -номер гармоники.

Представив значение А(к|1)и В(к1) для к 1 в виде A()=x,.cos(0. а «))+

+ ... + х„,cos ((И-1) а 1), B ) х а

".sin(0 д) )+... + x„„sin f (б1-1) a ), и учитывая что Х ь Х получа1 б

t. =0 ют А Ь Н1= ь х, . С о +... + а х „, ° С м- |

С =, ) соз(||„. ь. з-), k

m =к к причем С„. =С„., -cos(m; .б| сд ) и Со =o °

Проведя аналогичные преобразования и для B(u3), получают

В(|«1= 4хо Sý+ +1 х

В устройстве вычисления Я„ и С где ) =О,N-I, выполняются на накайливающих сумматорах 3, и Зд соответственно.

Вычисление д х-,S. и ь.х..С, вы Ц б б полняется на накапливающих сумматорах 3 и 3 соответственно

zX C =з|р(x(t) — Х;,) г "(,;

ЬХ- |.= sigl1(х(1)-х. 1 Я Я.

Значением Sign (x(t) -х „)осуществляется задание операции "Сложение" или

"Вычитание" на накапливающих сумматорах 3 и 34 . Операция 2 .С„ и

2 . S выполнена путем подключения

J выходов накапливающих сумматоров 3 и 3 к входам накапливающих суммато1 ров 3 и Зз соответственно со сдвигом на г разрядов в сторону младших разрядов.

Управляющие входы первого 3, и второго 3 накапливающих сумматоров подключены к нулевому потенциалу кор" пуса устройства, что обеспечивает задание ими режима "Вычитание".

<Формула изобретения

Устройство для вычисления коэффициентов Фурье, содержащее триггер, выход которого подключен к первому входу элемента И, выход которого подключен к входу элемента задержки и тактовым входам первого и второго накапливающих сумматоров, информационные выходы которых подключены к информационным входам соответственно третьего и четвертого накапливающих сумматоров, выходы которых являют я

Р соответственно выходами реальной и мнимой частей устройства, выход элемента задержки подключен к тактовым входам третьего и четвертого накапливающих сумматоров и счетному входу счетчика, выход переполнения которого является выходом готовности устройства и подключен к входу установки в "0" триггера, вход установки в "1" которого объединен с входами обнуления счетчика первого, второго, третьего и четвертого накапливающих сумматоров и является входом запуска устройства, а второй вход элемента И подключен к выходу генератора тактовых импульсов, о т л и ч а ю— щ е е с я тем, что, с целью упро, щения, оно содержит регистр, пятый накапливающий сумматор, сумматор по

73944

Составитель А. Баранов

ТехРед B.Кадар

Редактор С. Лысина

Корректор Л. Патай

Заказ 6479/48 Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/S

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

12

5 модулю два, первый и второй блоки йостоянйой памяти и аналого-цифровой преобразователь, выход которого подключен к входам раэрещения приема информации третьего и четвертого накапливающих сумматоров, выход элемента задержки и вход запуска устройства подключены соответственно к тактовому входу и входу обнуления аналого-qH4posoro преобразователя, информационный вход которого является информационным входом устройства, вход задания гармоник устрой.ства подключен к информационному входу регистра, выход которого подключен к информационному входу пятого накапливающего сумматора, выход и-го разряда (n-разрядность) которого подключен к знаковому входу первого накапливающего сумматора и первому входу сумматора по модулю два, второй вход которого подключен к выходу (n-1)-го разряда пятого накапльрдюп его сумматора, выход i-ro (i

1, и-2) разряда которого подключен к входам tj-х разрядов адреса первого и второго блоков постоянной памяти, выходы которых подключены к информационным входам соответственно

10 первого и второго накапливающих сумматоров, знаковый вход второго накапливающего сумматора подключен к выходу сумматора по модулю два, тактовый вход пятого накапливающего

15 сумматора обьединен с входами считы" вания первого и второго блоков пос1 тоянной памяти и подключен к выходу элемента И, а вход обнуления пятого накапливающего сумматора - к входу

20 запуска устройства.