Устройство для контроля ошибок магнитной записи- воспроизведения цифровой информации

Иллюстрации

Показать всеРеферат

Изобретение относится к цифровой магнитной записи и позволяет повысить точность контроля. Ошибки в воспроизводимом испытательном сигнале вьоделяются в устройстве путем поэлементного сравнения на сумматоре 3 воспроизводимой псевдослучайной последовательности символов с эталонной последовательностью. При отсутствии синхронизма на выходе сумматора 3 формируется псевдослучайная последовательность ошибок, на которую реагирует детектор 10, на выходе которого при этом формируется сигнал, который переключает триггер 9. Регистр 16 сдвига и сумматоры 17 и 18 образуют детектор 10, работающей по принципу проверки входного сигнала псевдослучайной последовательности на соответствие правилу ее кодообразования. Выходной сигнал триггера 9 поступает на управляющий вход коммутатора, который подключает информационный вход регистра 5 сдвига к входной шине 1 сигнала воспроизведения псевдослучайной последовательности . Элемент 11 стробирования преобразует сигнал опгабок в последовательность импульсов опшбок, подсчитываемых счетчиком 12. 1 ил. ю ч1 ОР со

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (5ll 4 С ll В 27/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР по ДелАм изОБРетен1 1Й и oTHPblTHA (21) 3891756/24-10 (22) 29.04.85 (46) 30.11.86.Бюл. 9 44 (72) И.А.Чехлай и И.В.Чумаков (53) 681.84.001 2 (088.8) (56) Авторское свидетельство СССР

В 1001171, кл. G 11 В 27/36,1981.

Авторское свидетельство СССР

Р 1137533, кл. G 11 В 27/36, 1983, (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОШИБОК

МАГНИТНОЙ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ

ЦИФРОВОЙ ИНФОРМАЦИИ (57) Изобретение относится к цифровой магнитной записи и позволяет повысить точность контроля. Ошибки в воспроизводимом испытательном сигнале выделяются в устройстве путем поэлементного сравнения на сумматоре

3 воспроизводимой псевдослучайной последовательности символов с эталонной последовательностью. При от„.SUÄÄ 1273994 А1 сутствии синхрониэма на выходе сумматора 3 формируется псевдослучайная последовательность ошибок, на которую реагирует детектор 10, на выходе которого при этом формируется сигнал, который переключает триггер 9. Регистр 16 сдвига и сумматоры 17 и 18 образуют детектор IO, работающий.по принципу проверки входного сигнала псевдослучайной последовательности на соответствие правилу ее кодообраэования. Выходной сигнал триггера 9 поступает на управляющий вход коммутатора, который подключает информационный вход регистра

5 сдвига к входной шине 1 сигнала воспроизведения псевдослучайной последовательности. Элемент ll стробирования преобразует сигнал ошибок в последовательность импульсов ошибок, подсчитываемых счетчиком 12. 1 ил.

1273994

10

ЗО ходом сумматора 4, Изобретение относится к приборостроению, а именно к технике цифровой магнитной записи, и может быть использовано в средствах контроля аппаратуры магнитной записи для измерения количества ошибок передачи цифровых данных каналами магнитной записи-Boспроизведения.

Целью изобретения является повышение точности контроля °

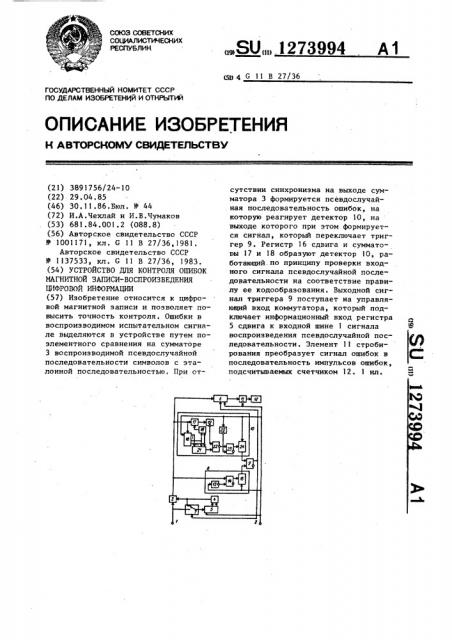

На чертеже изображена функциональная схема устройства.

Устройство содержит входную шину

1 сигнала воспроизведения псевдослучайной последовательности (символов), входную шину 2 тактового синхросигнала воспроизведения, первый и второй сумматоры 3 и 4 по модулю два, первый и второй регистры 5 и 6 сдвига, коммутатор 7, детектор 8 отсутствия ошибок, триггер 9, детектор 10 псевдослучайной последовательности ошибок, элемент 11 стробирования и счетчик 12 ошибок.

Детектор 8 содержит инвертор 13, D-триггер 14 и счетчик 15.

Детектор 10 содержит регистр 16 сцвига, первый и второй сумматоры

17 и 18 по модулю два, первый и второй инверторы 19 и 20, многовходовый элемент ИЛИ 21, элемент И-НЕ 22, D-триггер 23 и счетчик 24.

Входная шина 1 соединена с первым сигнальным входом коммутатора 7 и с первым входом сумматора 3, выход которого соединен с первым информацион- ным входом детектора 8, с первым информационным входом детектора 10 и с информационным входом регистра 6 сдвига. Выход коммутатора 7 соединен с информационным входом регистра 5 сдвига, выходы двух разрядов которого соединены с первым и вторым входами сумматора 4, выход которого соединен с вторым сигнальным входом коммутатора 7 и со вторым входом сумматора 3. Выход детектора 10 соединен с первым входом триггера 9, второй вход которого соединен с выходом детектора 8. Выход триггера 9 соединен с управляющим входом коммутатора 7 и с установочным входом регистра 6, выход которого соединен с первым сигнальным входом элемента 11 стробирования, выход которого соединен с входом счетчика 12 ошибок. Входная шина

2 соединена с тактовым входом регистра 5 сдвига, с вторым тактовым входом детектора 8, с вторым тактовым входом детектора 10, с тактовым входом регистра 6 сдвига и с вторым стробирующим входом элемента ll стробирования.

Первый вход детектора 8 соединен с D-входом D-триггера 14, прямой выход которого соединен с установочным входом счетчика 15, выход которого соединен с выходом детектора 8. Второй вход детектора 8 соединен со счетным входом счетчика 15 и с входом инвертора 13, выход которого соединен с С-входом D-триггера 14.

Первый вход детектора 10 соединен с первым входом сумматора 17 и с информационным входом регистра 16 сдвига, выходы всех разрядов которого соединены с входами многовходового элемента ИЛИ 21, выход которого соединен с первым входом элемента И-НЕ

22. Выходы двух разрядов регистра

16 сдвига соединены с первым и вторым входами сумматора 18 выход которого соединен с вторым входом сумматора 17, выход которого соединен с входом инвертора 19 ° Выход инвертора

l9 соединен с вторым входом элемента

И-НЕ 22, выход которого соединен с

D-входом D-триггера 23, выход которого соединен с установочным входом счетчика 24. Второй вход детектора

10 соединен со счетным входом счетчика 24, с тактовым входом регистра сдвига 16 и с входом инвертора 20, выход которого соединен с С-входом

D-триггера 23. Выход счетчика 24 соединен с выходом детектора 10.

Конкретное исполнение отдельных элементов и узлов следующее.

Регистры 5 и 16 сдвига — семиразрядные. С входами сумматоров по модулю два 4 и 18 соединены выходы шестого и седьмого разрядов регистров сдвига 5 и 16. Коммутатор 7 соединяет информационный вход регистра

6 сдвига с входной шиной 1 при наличии на управляющем входе коммутатора выходного сигнала триггера 9.При отсутствии выходного сигнала триггера 9 коммутатор 7 соединяет информационный вход регистра 5 с вы11одуль счета счетчиков 15 и 24 равен 16, т.е. сигнал на выходе этих счетчиков появится через 16 тактов синхросигнала воспроизведения при

1273994 отсутствии за это время сигнала на установочньх входах счетчиков.

Число разрядов регистра сдвига 6 равно 24.

Второй вход элемента ll стробирования — инверсный, т.е. стробирование выходного сигнала регистра 6 сдвига производится второй отрицательной полуволной тактового синхросигнала воспроизведения ° 10

Устройство работает следующим образом.

Регистр 5 и сумматор 4 образуют в случае, когда информационный вход регистра 5 сдвига подключен посредст- 15 вом коммутатора 7 к выходу сумматора 4, генера*op эталонной псевдослучайной последовательности символов, идейтичный генератору (не показан), который формирует записываемую на магнитный носитель (не показан) испытательную псевдослучайную последовательность символов.

Ошибки в воспроизводимом испыта-" тельном сигнале выделяются в предла- 25 гаемом устройстве путем поэлементного сравнения на сумматоре 3 воспроизводимой псевдослучайной последовательности символов с эталонной последовательностью. При этом эталон- 30 ная псевдослучайная последовательность должна формироваться поэлементно синхронно с воспроизводимой последовательностью.

В синхрониэм с воспроизводимой 35 псевдослучайной последовательностью генератор эталонной псевдослучайной последовательности вводится путем подключения посредством коммутатора 7 информационного входа регист- 40 ра 5 к входной шине 1.

При отсутствии синхронизма между эталонной псевдослучайной последовательностью на выходе сумматора 3 формируется псевдослучайная последова- 45 тельность ошибок.

На эту последовательно реагирует детектор 10, на выходе которого при этом формируется сигнал, который переключает триггер 9. 50

Детектор 10 работает следующим образом.

Псевдослучайная последовательность ошибок поступает на информационный вход регистра l6 сдвига и на первый вход сумматора !7. На второй вход этого сумматора поступает сигнал с выхода сумматора 18, подключенного к выходам двух разрядов регистра 16 сдвига, соответствующих двум разрядам регистра 5 сдвига, к выходам которых подключен сумматор 4.

В результате регистр 16 сдвига и сумматоры 17 и 18 образуют известный детектор ошибок, работающий по принципу проверки входного сигнала (в данном случае выходного сигнала ошибок сумматора 3) псевдослучайной последовательности на соответствие правилу ее кодообразования.

В результате, при поступлении на первый вход детектора 10 "безошибочной" псевдослучайной последовательности ошибок на выходе сумматора 17 формируется постоянный низкий уро", вень логического "0 (отсутствие

"ошибок" ), а на выходе инвертора 19— соответственно высокий уровень логической "1". В это же время высокий уровень постоянно формИруется и на выходе многовходового элемента И 21, поскольку хотя бы в одном из разрядов регистра 16 обязательно будет присутствовать логическая "I"". .При этом на выходе элемента И-НЕ 22 устанавливается низкий уровень, который следующим перепадом тактового синхросигнала воспроизведения записывается в 0-триггер 23. В результате на выходе этого триггера постоянно формируется низкий уровень, благодаря чему снимается блокировка по установочному входу счетчика

24, который начинает подсчитывать тактовые синхроимпульсы. Через 1á (для данного примера) тактов нв вы" ходе счетчика 24 и, следовательио, на выходе детектора 10 формируется сигнал. Наличие D-триггера 2Э связано с необходимостью исключения поступления на установочный вход счетчика 24 ложных коротких по длительноности импульсов, формируемых на выходе сумматора 17 в начале тактовых позиций из-за неодновременного поступления сигналов на его выходы. Элемент ИЛИ 2l предотвращает возможность формирования выходного сигнала детектором 10 в случае поступления на его первый вход последовательности нулей.

Выходной сигнал триггера 9 поступает на управляющий вход коммутатора

7, который при этом подключает информационный вход регистра 5 сдвига к входной шине 1 сигнала воспроиэведе994

S > 2.73 ния псевдослучайной последовательно- сти.

Через семь (для данного примера разрядности регистра 5) тактов, т.е. после заполнения регистра 5 сдвига воспроизводимой псевдослучайной последовательностью, перестает формироваться сигнал ошибок на выходе сумматора 3, на что реагирует детектор

8 отсутствия ошибок.

Через шестнадцать (для данного примера модуля счета счетчика 15) тактов формируется сигнал на выходе детектора 8, который сбрасывает триггер 9 в исходное состояние. 35

D-триггер 14 в детекторе 8 защищает счетчик 15 от поступления на его установочный вход ложных корот-. ких по длительности импульсов, формируемых на выходе сумматора 3 в на- 20 чале тактовых позиций из-за неодновременного поступления сигналов на

его входы.. Поэтому запись выходного сигнала сумматора 3 в D-триггер

14 производится в середине тактового импульса.

После переключения триггера 9 в исходное состояние снимается сигнал с управляющего входа коммутатора 7, который при этом подключает инфор- З0 мационный вход регистра 5 сдвига к выходу сумматора 4 ° Далее регистр 5 и сумматор 4 начинают сами генерировать эталонную псевдослучайную последовательность символов, но уже син- хронно с воспроизводимой последовательностью.

Ошибка на выходе сумматора 3 формируется в случае несоответствия очередного символа воспроизводимой псев-40 дослучайной последовательности соответствующему символу эталонной последовательности. Сигнал ошйбок формируется в потенциальном коде БВН ("без возвращения к нулю") и посту- 45 пает через регистр 6 на первый вход элемента 11 стробирования.

Элемент 11 осуществляет преобразование сигнала ошибок в коде БВН (ошибкам в этом коде соответствует 0 высокий уровень логической "1") в последовательность импульсов ошибок, которая подсчитывается счетчиком 12 ошибок. Протяженность пачки ошибок, безошибочно выделяемой устройством. 55 йе ограничена.

После возможного в канале магнитной записи сбоя тактового синхросигнала воспроизведения нарушается синхронизм между эталонной и воспроизводимой псевдослучайной последовательностью. При этом автоматический ввод устройства в синхронизм с воспроизводимой последовательностью с помощью детектора 10, триггера 9, коммутатора 7 и детектора 8 происходит аналогично.

Во время захвата псевдослучайной последовательности ошибок детектором 1О, который длится для данного примера 23 такта, формируемое на выходе сумматора 3 некоторое количество ошибок является следствием нарушения синхронизма, а не является ошибками воспроизводимого сигнала.

Для устранения поступления этого количества ложных ошибок на вход счетчика 12 предназначен буферный регистр 6, разрядность которого соответственно равна 24. После переключения.триггера 9 его выходной сиг-. нал поступает на установочный вход регистра сдвига 6 и обнуляет все его разряды, в которых было записано к этому моменту искомое количество ложнык ошибок. Ложные ошибки, формируемые на выходе сумматора 3 во время ввода устройства в синхронизм, которое включает в себя заполнение регистра 5 и захват выходного нулевого сигнала сумматора 3 детектором 8, также не поступают на вход счетчика

12 ошибок, поскольку в этом время регистр 6 сдвига будет заперт в нулевом состоянии выходным сигналом триггера 9.

Формула изобретения

Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации, содержащее первый сумматор,по модулю два, одним входом соединенный с входной шиной сигнала воспроизведения псевдослучайной последовательности, первый регистр сдвига, выходами подключенный через второй сумматор по модулю два и первый сумматор по модулю два к первому входу детектора отсутствия ошибок и последовательно соединенные второй регистр сдвига, элемент стробирования и счетчик ошибок, причем тактовые входы регистров сдвига и вторые входы детектора отсутствия ошибок и элемента стробирования подключены к

Составитель А. Лисицын

Техред И.Попович Корректор Л.Пилипенко

Редактор A.Äîëèíè÷

Заказ 6482/50 Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий !

13035, Москва, Ж-35, Раушская наб., д.4/5! роизводственно-полиграфическое предприятие,г.ужгород,ул.Проектная,4

1273994

L входной шине тактового синхросигнала входу триггера, выход которого соевоспроизведения, о т л и ч а ю щ е- динен с управляющим входом коммутае с я тем, что, с целью повышения тора и с установочным входом второго точности контроля, в него введены регистра сдвига, входная шина сигнакоммутатор, детектор псевдослучай- 5 ла воспроизведения псевдослучайной ной последовательности ошибок и триг- последовательности и выход второго гер, причем выход первого сумматора сумматора по модулю два подключены по модулю два и входная шина такто- соответственно к первому и второму вого синхросигнала воспроизведения сигнальным входам коммутатора, выход соединены соответственно с первым и о которого соединен с информационным вторым входами детектора псевдослу- входом первого регистра сдвига, вычайной последовательности ошибок, ход первого сумматора по модувыход которого подключен к первому лю дв а подключен к информаци.Входу триггера, выход детектора от- онному входу второго регистра сутствия ошибок подключен к второму сдвига.