Запоминающее устройство с обнаружением и исправлением ошибок

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с обнаружением двукратных опшбок и исправлением однократных. Цель изобретения - повышение надежности устройства. Устройство содержит йснопной и два дополнительных накопителя , два блока контроля, один из которых осуществляет формирование контрольных битов и битов синдрома по Хэммннгу, а другой - контроль по четности, счетчик и регистр, служацие соответственно для подсчета и хранения ошибок, дешифратор, распределитель импульсов, элемент ИЛИ-НЕ, переключатель, содержащий механические перемычки. Цель изобретения достигается за счет того, что уменьшается , сложность и длительность проi цесса настройки устройства, при этом уменьшается в 4 раза объем памяти W контрольных разрядов. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (51) 4G11 С2900

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АBTOPCHOMY СВИДЕТЕЛЬСТВУ

4ь

С0

Ю

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3855383/24-24 (22) 11.02.85 (46) 30.11.86. Бюл. 11 44 (72) В,К, Скубко (53) 681.327 (088.8) (56) Путинцев tf,Ä. Аппаратный конт-. роль управляющих цифровых вычислительных машин. М.: Советское радио, 1966, с. 87-98.

Электроника, 1981, Р 9, с.33-39. (54) ЗЛПОМ11НАЮЦЕЕ УСТРОЙСТВО С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК (57) Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах с обнаружением двукратных ошибок и исправлением однократных. Цель

„.SU„„1274006 А1 изобретения - повышение надежности устройства, Устройство содержит dc- новной и два дополнительных накопителя, два блока контроля, один из которых осуществляет формирование контрольных битов и битов синдрома по

Хэммингу, а другой — контроль по четности, счетчик и регистр, служащие соответственно для подсчета и хранения ошибок, дешифратор, распределитель импульсов, элемент ИЛИ-HE переключатель, содержащий механические перемычки. Цель изобретения достигается за счет того, что уменьшается. сложность и длительность процесса настройки устройства, при этом уменьшается в 4 раза объем памяти контрольных разрядов. 4 ип.

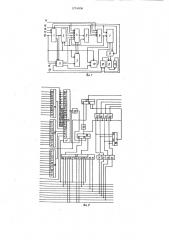

Изобретение относится к вычислительной технике и может быть исполь. зовано в запоминающих устройствах с обнаружением и исправлением ошибок, Цель изобретения " уменьшение объема памяти контрольных разрядов ,устройства, На фиг ° 1 изображена структурная схема запоминающего устройства с обнаружением и исправлением ошибок; на фиг. 2 — электрическая прин ципиальная схема распределителя импульсов для основного накопителя емкостью 16х4 Кбит, на фиг, 3 — функциональная схема первого блока контроля для восьмиразрядного слова;, на фиг, 4 — функциональная схема переключателя.

Запоминающее устройство с обнаружением и исправлением ошибок (см„ фиг. 1) содержит блок 1 управления, основной накопитель 2, первый дополнительный накопитель 3, первый блок

4 контроля, осуцествляющий формирование контрольных битов и битов синдрома по Хэммингу, дешифратор 5, блок 6 двунаправленной передачи данных, второй блок 7 контроля, осуществляющий контроль по четкости, счетчик 8, служащий для подсчета ошибок, регистр 9, элемент ИЛИ-НЕ

10, распределитель ll импульсов, второй дополнительный накопитель 12, являющийся одноразрядным накопителем, переключатель 13., содержащий механические перемычки. На фиг. I обозначены информационная шина 14 устройства, дополнительный контрольный вход 15 устройства, вход 16 записи, вход 17 чтения, адресный вход 18, основной контрольный вход

i19 и вход 20 загрузки устройства. °

Распределитель ll импульсов (см.фиг.2) содержит мультиплексоры

21-25, элементы 2Н-ИЛИ-НЕ 26, 27,, элемент 2И-ИЛИ 28, элементы HE

29-34, И-НЕ 35-38.

Первый блок 4 контроля (см,фиг,3) содержит группы 39 и 40 сумматоров .по модулю два, первую 41 и вторую

42 выходных информационных шин, шины записи 43 и чтения 44, шину 45 "Кор- рекция", выходные 46 и входные 47 шины контрольных разрядов по Хэммингу, выходные шины 48 синдромов ошибки, входные шины 49 "Имитация ошибки", ограничительные элементы в виде резисторов 50. Переключатель

74006 з

13 (см,фиг. 4)содержит четыре грУп пы контактных штырей 51-54, входные

55 и выходные 56 шины, шину 57 лог.

"0", шину 58 лог, "1", перемычки 59.

Запоминающее устройство работает следующим образом, С выходов блока 1 сигналы о выборе памяти поступают в накопитель

2 и распределитель 11, причем в ре10 жиме "Регенерация" они на всех и н выход ах равны пот енциалу лог, а в режиме "Запись" или "Чтение" только на одном выходе сигнал равен потенциалу лог.О", С одного из выходов блока 1 импульс адреса строк поступает на распределитель 11. Ад-. ресные сигналы со входа 18 поступают на блок 1, накопители 2,3 и 12 и распределитель 11. При наличии по2О тенциала "лог„0" на входе 19 распределитель 11 обеспечивает 28 вариант тов распределения контрольных бит по основному объему памяти. Информация с регистра 9 проходит через переклю25 чатель 59 в среднее положение, Мультиплексоры 21-23 формируют 512 наборов переменных. Каждый набор формирует 16 бит информации на выходе мультиплексора 24. Другая половина массива N двоичных знаков (N=16 Кбит) формируется при изменении состояния адреса на входе А3 мультиплексора 24, Мультиплексор 25 управляется старшими разрядами адреса и формирует

35 сигналЫ благодаря которым на выхо9 де элемента 2И-ИЛИ-НЕ 26 формируется N нулей и 3 N единиц при обработке информаци™. емкостью 16х4 Кбит, независимо от варианта распределения двоичных знаков в массиве.

Вариант распределения (при среднем положении перемычек 59) определяется информацией регистра 9, которая при управляющем сигнале на соответствуюцем входе 20 и по синхрони45

tt t1 зирующей команде Запись на соответствующем выходе блока 1 заносится в регистр 9 со счетчика 8, который считает однобитовые ошибки по

S0 синхронизирующей команде "Чтение" на соответствующем выходе блока 1.

При снятии потенциала "лог.0" с входа 19 на выходе элемента 2 ИИЛИ-НЕ 26 будет потенциал "лог.l", контроль битов информации будет осуществляться только на четность нако55 пителем 12. Управляющий потенциал

Коррекция на соотве fcTBóþùåì выходе распределителя 11 и соответствен7.4006 4

<5

При регулировке устройства в эг стремальньгх условиях перемычки 59 пе- 25 реключателя 13 устанавливаются в среднее положение, соединяя входные и выходные шины 55, 56 поразрядно.

В результате самонастраивания устройства устанавливается вариант рас- 30 пределения контрольных бит, при которой сбои отсутствуют. Данные регистра 9 фиксируют перемычками 59, подключая их к контактным штырям 53 или 54 (шины "лог.0" или "лог.1"), 35

Запоминающее устройство с обнаружением и исправлением ошибок, содержащее основной накопитель и первый дополнительный накопитель, блок управления, первый блок контроля, дешифратор, блок двунаправленной передачи данных, причем выход основного накопителя подключен к первым входам первого блока контроля и дешифратора, второй вход которого подключен к первому выходу первого блока контроля, подключенного вторым входом и вторым выходом соответственно к выходу и первому входу первого дополнительного накопителя, второй вход которого, первый вход блока управления и второй вход основного накопителя являются адресным входом устройства, а его входами чтения и записи являются второй и третий входы блока управления, первый, второй з 12 но на входе одноименной шины 45 бло. ка 4 появится только при наличии пбтенциала "лог.1" на выходе элемента НЕ 30. Счетчик 8 и регистр 9 целесообразно выполнить восьми разрядными для увеличения до 28 вариантов распределения контрольных бит по основному объему памяти.

Первая группа 39 сумматоров блока

4 формирует при записи контрольные разряды по методу Хэмминга. По шинам

49 имеется возможность ввести ошибку в один или несколько контрольных разрядов, что позволяет проверить .цепи и элементы дешифрации и элемен ты формирования сигналов однобитовых и двухбитовых ошибок дешифратора 5, а также проверить соответствие выходной и%формации устройства входной, . обнаружить неисправный контрольный разряд при последовательно ложных контрольных разрядах.

Формулаизобретения и третий выходы которого подключены соответственно к первому входу основного накопителя, первому входу блока двунаправленной передачи данных, третьему входу первого блока контроля и второму входу блока двунаправленной передачи данных, третий вход которого соединен с выходом дешифратора, а первый выход — с третьим входом основного накопителя и четвертым входом первого блока контроля, вход-выход блока двунаправленной передачи данных соединен с информационной шиной устройства,о т л и ч а ю щ е е с я тем, что, с целью уменьшения объема памяти контрольных разрядов устройства, в него введены счетчик, регистр, второй блок контроля, распределитель импульсов, второй дополнительный накопитель, элемент ИЛИ-НЕ и переключатель, выход которого соединен с первым входом распределителя импульсов, второй, третий и четвертый входы которого соединены соответственно с первым и четвертым выходами и первым входом блока управления, а пятый вход распределителя импульсов является основным контрольным вхо-. дом устройства, вьгходы распределителя импульсов подключены соответственно к пятому входу первого блока контроля, третьему входу первого дополнительного накопителя и первому входу второго дополнительного накопителя, второй и третий входы и выход которого соединены соответственно с адресным входом устройства и первыми выходом и входом второго блока контроля, второй и третий входы которого подключены соответственно к первому выходу блока двунаправленной передачи данных и третьему выходу блока управления, второй выход второго блока контроля соединен с первым входом счетчика, второй вход которого подключен к третьему выходу блока управления, а выход соединен с первым входом регистра, второй вход которого подключен к выходу элемента ИЛИ-НЕ, первый вход которого является входом загрузки устройства, а второй вход соединен с вторым выходом блока управления, вход переключателя соединен с выходом регистра, шестой вход первого блока контроля .соединен с вторым выходом блока управления, а седьмой вход является дополнительным контрольным входом устройства.

127ч006

1274006

18

Составитель В, Рудаков

Редактор А. Долинич Техред M.Õoäàíè÷ Корректор А. Обручар

Заказ б483/51 Тираж . 54 3 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4