Устройство для управления и стабилизации параметров выходного напряжения преобразователя

Иллюстрации

Показать всеРеферат

Изобретение относится к электротехнике и может быть использовано для управления преобразователями. Целью изобретения является улучшение энергетических и динамических характеристик вентильного преобразователя. Выходной сигнал преобразователя поступает на блок анализатора спектра щ Уолша (БАСУ) 3, на выходе которого появляются коэффициенты спектрального разложения кривой выходного напряжения усилителя мощности 12 в ряд Уолша в виде двоичного кода. Эти коэффициенты подаются на входы первого блока сумматоров 8, где сравниваются с эталонными кодами коэффициентов функций Уолша. Значения отклонения подаются на входы второго блока сумматоров 9, где в зависимости от их знака происходит либо суммирование , либо вычитание с эталонными значениями кодов. Эти сигналы через блок цифроаналоговых преобразователей 10 подаются на коммутационные входы блока ключей 6. Подача § этих напряжений на входы блока широтно-импульсных преобразователей (Л 4 происходит при поступлении на управляющие входы блока ключей 6 напряжения, соответствующего той или иной функции Уолша. В блоке широтноимпульсньпс преобразователей 4 происходит сравнение синтезированных сигналов с напряжением пшлообразной формы и результаты сравнения распределяются по вентилям преобразователя . 3 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕОКИХ

РЕСПУБЛИК

А1 (19) SU (11) (59 4 Н 02 7 48

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ У СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21 ) 3 731 325/24-07 (22) 19.04.84 (46) 30. 11.86. Бюл. 9 44 (7 1) Северо-Кавказский ордена Дружбы народов горно-металлургический институт (72) А.И. Денисов, В.К. Райфшнайдер и В.М. Бушуев (53) 621.316.727(088.8) (56) Авторское свидетельство СССР и 611285, кл. Н 02 Р 13/16, 1978.

Авторское свидетельство СССР

У 752746, кл. Н 02 P 13/16, 1980. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ И СТАБИЛИЗАЦИИ ПАРАМЕТРОВ ВЫХОДНОГО НАПРЯЖЕНИЯ ПРЕОБРАЗОВАТЕЛЯ (57) Изобретение относится к электротехнике и может быть использовано для управления преобразователями.

Целью изобретения является улучшение энергетических и динамических характеристик вентильного преобразователя, Выходной сигнал преобразователя поступает на блок анализатора спектра (Уолша (БАСУ) 3, на выходе которого появляются коэффициенты спектрального разложения кривой выходного напряжения усилителя мощности l2 в ряд Уолша в виде двоичного кода. Эти коэффициенты подаются на входы первого блока сумматоров 8, где сравниваются с эталонными кодами коэффициентов функций Уолша. Значения отклонения подаются на входы второго блока сумматоров 9, где в зависимости от их знака происходит либо суммирование, либо вычитание с эталонными значениями кодов. Эти сигналы через блок цифроаналоговых преобразователей 10 подаются на коммутационные входы блока ключей 6. Подача этих напряжений на входы блока широтно-импульсных преобразователей

4 происходит при поступлении на управляющие входы блока ключей 6 напряжения, соответствующего той или иной функции Уолша. В блоке широтноимпульсных преобразователей 4 происходит сравнение синтезированных сигналов с напряжением шилообразной формы и результаты сравнения распределяются по вентилям преобразователя, 3 ил.

1274094

Изобретение относится к электротехнике, а именно к системам управления вентильными электроприводами ,промышленных установок и транспортных средств.

Целью изобретения является улучшение энергетических и динамических характеристик вентильного преобразователя и расширение его функциональных вазможностей.

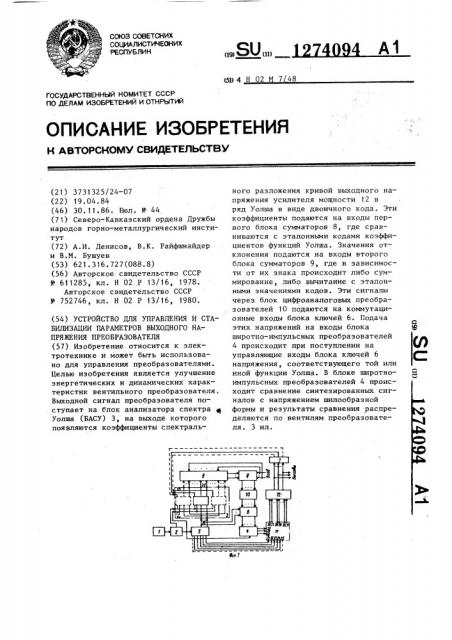

На фиг. t показана структурная схема устройства; на фиг. 2 — схема комбинационно-логического блока; на фиг. 3 — .схема анализатора спектра Уолша.

Устройство (фиг. 1) состоит из генератора тактовых импульсов 1, выход которого подключен к входу делителя частоты 2, высокочастотный выход которого соединен с входом считывания блока анализатора спектра

Уолша 3, а его низкочастотный выход подключен к входу синхронизации блока широтно-импульсных преобразователей 4, входу синхронизации блока анализатора спектра Уолша 3 и к входу генератора функций Уолша 5, основные выходы которого соединены с соответствующими управляющими входами флака ключей 6 и базисными входами блока анализатора спектра

Уолша 3, входы сигнала спектрального разложения которого пофаэно соединены с выходами блока фильтров низкой частоты 7, входы которого подключены к выходу устройства, причем выходы блока анализатора спектра Уолша 3 соединены с соответствующими первыми входами первого блока сумматоров 8, вторые входы которого соединены с соответствующими первыми входами второго блока сумматоров

9, которые одновременно являются и входами устройства, причем вторые входы второго блока сумматоров 9 соединены с соответствующими выходами первого блока сумматоров 8, а выходы второго блока сумматоров 9 подключены к соответствующим входам блока цифроаналоговых преобразователей 10, выходы которого соединены с коммутационными входами блока ключей 6, а выходы последнего — с входами суммирования блока широтноимпульсных преобразователей 4, выходы которого подключены к информационным входам комбинационно-логического блока 11, базисные входы которого

1О

45 соединены с соответствующими выходами генератора функций Уолша 5, а его; выходы — с соответствующими входами усилителя мощности 12, выходы которого являются выходами устройства.

При этом вход считывания блока анализатора спектра Уолша обозначен позицией 13, его вход синхронизации14, а входы сигнала спектрального разложения — 15. Базисные входы блока анализатора спектра Уолша обо1 значены позицией 16, а его выходы—

17. Информационные входы комбинационно-логического блока обозначены позициями 18, 19 и 20, а его базисные входы 2 1-25, а выходы генератора функций Уолша 26-31.

Комбинационно-логический блок 11 (фиг. 2) содержит первый элемент

2И-ИЛИ-НЕ 32, первый и второй входы которого соединены с первым и четвертым входами второго элемента

2И-ИЛИ-НЕ 33 и первым базисным входом 23 комбинационно-логического блока 11, третий вход которого соединен с третьим входом второго элемента 2И-ИЛИ-НЕ 33 и вторым базисным входом 24 комбинационно-логического блока 11, а четвертый вход— с вторым входом второго элемента

2И-ИЛИ-НЕ 33 и третьим базисным входом 25 комбинационно-логического блока 11, причем выход первого элемента 2И-ИЛИ-НЕ 32 подключен к входу первого логического инвертора 34 и второму входу первого элемента

И 35, первый вход которого соединен с первым информационным входом 18 комбинационно-логического блока 11 и вторым входом второго элемента

И 36, первый вход которого подключен к выходу первого логического инвертора 34, а выход - к второму входу третьего элемента 2И-ИЛИ-HE 37 и второму входу четвертого элемента 2И-ИЛИ-НЕ 38, третий вход которого соединен с выходом первого элемента И 35 и третьим входом третьего элемента 2И-ИЛИ-НЕ 37, первый вход которого соединен с четвертым базисным входом 22 комбинационно-логического блока 11 и четвертым входом четвертого элемента 2И-ИЛИ-НЕ 38, первый вход которого соединен с четвертым входом третьего элемента

2И-ИЛИ-НЕ 37, пятым базисным входом

21 комбинационно-логического блока

11. первым входом третьего элемента

1274094

И 39, второй вход которого подключен к второму информационному входу 19 комбинационно-логического блока 11 и к первому входу четвертого элемента И 40, вход пятого элемента И 41 5 и выход логического инвертора 42 подключены к входам шестого элемента И 43, второй вход четвертого элемента И 40 подключен к четвертому

10 базисному входу 22 комбинационнологического блока 11, к четвертому входу пятого элемента 2И-ИЛИ-НЕ 44 и к первому входу шестого элемента

2И-ИЛИ-НЕ 45, третий вход которого

15 подключен к выходу пятого элемента

И 41 и к третьему входу пятого элемента 2И-ИЛИ-НЕ 44, первый вход которого соединен с четвертым входом шестого элемента 2И-ИЛИ-НЕ 45 и пя20 тым базисным входом 21 комбинационно-логического блока 11, а второй вход — с вторым входом шестого элемента 2И-ИЛИ-НЕ 45 и выходом шестого элемента И 43, второй вход которого соединен с выходом второго логического инвертора 42, вход которого подключен к выходу второго элемента

2И-ИЛИ-НЕ 33 и к первому входу пятого элемента И 41, второй вход которого соединен с первым входом шестого элемента И 43 и третьим информационным входом 20 комбинационно-логического блока 11, причем выходами первым 26 и вторым 27 комбинационно-логического блока 11 являются 35 соответственно выходы третьего 37 и четвертого 38 элементов 2И-ИЛИ вЂ , выходами третьим 28 и четвертым 29— соответственно выходы пятого 44 и шестого 45 элементов 2И-ИЛИ-НЕ и вы- 40 ходами пятым 30 и шестым 31 — соответственно выходы третьего 39 и четвертого 40 элементов И.

Блок анализатора спектра Уолша 3 (фиг. 3) включает в себя несколько цифровых анализаторов спектра. Количество анализаторов может быть произвольным, в частности оно может быть определено числом фаз преобразователя. Цифровой анализатор спект- 50 ра Уолша содержит ячейку запоминания

46, элемент РАВНОЗНАЧНОСТЬ 47, регистрирующий прибор, выполненный на основе реверсивных счетчиков 48-51, информационные входы которых соеди- И иены с выходами элемента РАВНОЗНАЧНОСТЬ, последовательно-соединенные масштабирующий усилитель 52, аналоговый ключ 53, ячейку запоминания

54 и усилитель 55 и параллельно соединенные с ним последовательно связанные два ключа 56, 57 и два усилителя 58, 59, выходы которых связаны с соответствующими управляющими входами ключей 56, 57. Точка соединения усилителей 58, 59 соединена с первым входом элемента РАВНОЗНАЧНОСТЬ 47, вторые входы которого являются базисными входами 16 блока анализатора спектра Уолша 3, вход элемента 46 является входом 14 синхронизации блока анализатора спектра

Уолша, причем выход элемента 46 соединен с вторым входом аналогового ключа 53 и первым входом преобразователя 60 напряжение — длительность, второй вход которого соединен со средней точкой двух ключей 56 и 57, а выход элемента И 61 — со счетными входами реверсивных счетчиков 48 — 51, второй вход элемента И 61 является входом считывания 13 блока анализатора спектра Уолша 3, а вход масштабирующего усилителя 52 является входом сигнала спектрального разложения 15 блока анализатора спектра Уолша 3.

Выходами цифрового анализатора спектра Уолша являются выходы реверсивных счетчиков 48-51.

Устройство работает следующим образом.

Импульсы с генератора тактовых импульсов 1 поступают на вход делителя частоты 2, сигналы с выходов которого обеспечивают работу блоков 3, 4 и 5. Сигналы с высокочастотного выхода делителя частоты 2 управляют работой блока анализатора спектра

Уолша 3, а сигналы с низкочастотного выхода синхронизируют работу генератора функции Уолша 5, блока широтноимпульсных преобразователей 4 и блока анализатора спектра Уолша 3. Выходной сигнал преобразователя, пройдя через блок фильтра низкой частоты 7, поступает на блок 3, где он анализируется при помощи базиса функций Уолша, т.е. на выходе блока

3 появляются коэффициенты спектрального разложения кривой выходного напряжения усилителя мощности 12 в ряд Уолша в виде двоичного кода.

Коэффициенты разложения подаются на первые входы первого блока сумматоров 8, где сравниваются с эталонными кодами коэффициентов функций

1274094

Уолша, которые могут быть заданы, например, ЭВМ, Операция вычитания здесь сведена к операции сложения путем сложения двоичных чисел в дополнительном коде. Отклонения реальных значений кодов от эталонных подаются на вторые входы второго блока сумматоров 9, где в зависимости от их знака происходит либо суммирование последних с эталонными значениями кодов, в случае если реальный коэффициент больше эталонного, либо их вычитание, если коэффициент меньше эталонного. Поступающие на входы блока цифроаналоговых преобразователей 10 коды скорректированных коэффициентов преобразуются в напряжения, которые подаются на коммутационные входы блока ключей 6.

Подача этих напряжений на входы суммирования блока широтно-импульсных преобразователей 4 происходит при поступлении на управляющие входы блока ключей 6 напряжения, соответствующего той или иной функции Уолша °

В блоке 4 происходит сравнение синтезированных по скорректированным коэффициентам Уолша сигналов с напряжением пилообразной формы. Суммированные таким образом широтно-модулированные сигналы поступают на информационные входы 18-20 комбинационнологического блока 11, где происходит распределение их по заданным фазам преобразователя. Управление блоком

11 осуществляет генератор функций

Уолша 5. При изменении по каким-либо причинам спектрального состава выходного напряжения преобразователя происходит изменение коэффициентов функций Уолша, снимаемых с блока 3, и после блока 10 выделяется напряжение ошибки, которое, воздействуя на блок 4, изменяет ширину импульсов управления усилителем мощности 12, приводя тем самым спектральный состав выходного напряжения в состояние до его изменения. Таким образом осуществляется стабилизация спектрального состава выходного напряжения преобразователя.

Формула изобретения

Устройство для управления и стабилизации параметров выходного напряжения преобразователя, содержащее генератор тактовых импульсов, усили!

О

4а

45 тель мощности, генератор функций

Уолша, блок широтно-импульсных преобразователей, комбинационно-логический блок, включающий первый элемент

2И-ИЛИ-НЕ, первый и второй входы которого соединены с первым и четвертым входами второго элемента 2И-ИЛИНЕ и являются первым базисным входом комбинационно-логического блока, третий вход которого соединен с третьим входом второго элемента

2И-ИЛИ-HE и является вторым базисным входом комбинационно-логического блока, а четвертый вход — с вторым входом второго элемента 2И-ИЛИ-НЕ и является третьим базисным входом комбинационно-логического блока, выход первого элемента 2И-ИЛИ-HE подключен к входу первого логического инвертора -и второму входу первого элемента И, первый вход которого является первым информационным входом комбинационно-логического блока и соединен с вторым входом второго элемента И, первый вход которого подключен к выходу первого логического инвертора, а выход — к второму входу третьего элемента 2И-ИЛИ-HE u второму входу четвертого элемента

2И-ИЛИ-НЕ, третий вход которого соединен с выходом первого элемента И и третьим входом третьего элемента

2И-ИЛИ-НЕ, первый вход которого является четвертым базисным входом комбинационно-логического блока и соединен с четвертым входом четвертого элемента 2И-ИЛИ-НЕ, первый вход которого соединен с четвертым входом третьего элемента 2И-ИЛИ-НЕ и является пятым базисным входом комбинационно-логического блока и сЬединен с первым входом третьего элемента И, второй вход которого подключен к второму информационному входу комбинационно-логического блока и первому входу четвертого элемента И, второй вход которого подключен к четвертому базисному входу комбинационно-логического блока, 50 четвертому входу пятого элемента

2И-ИЛИ-НЕ и к первому входу шестого элемента 2И-НЕ-ИЛИ, третий вход которого подключен к выходу пятого элемента И и к третьему входу пято55 го элемента 2И-ИЛИ-НЕ, первый вход которого соединен с четвертым входом шестого элемента 2И-ИЛИ-НЕ и пятья базисным входом комбинационно12740 логического блока, а второй вход— с вторым входом шестого элемента

2И-ИЛИ-НЕ и выходом шестого элемента

И, второй вход которого соединен с выходом второго логического инвертора, вход которого подключен к выходу второго элемента 2И-ИЛИ-НЕ и к первому входу пятого элемента И, второй вход которого соединен с первым входом шестого элемента И и 10 третьим информационным входом комбинационно-логического блока, причем первым и вторым выходами комбинационно-логического блока являются соо ответственно выходы третьего и чет- 15 вертого элементов 2И-ИЛИ-НЕ, третьим и четвертым выходами — соответственно выходы пятого и шестого элементов

2И-ИЛИ-НЕ, а пятым и шестым выходами — соответственно выходы третьего .20 и четвертого элементов И, вход синхронизации блока широтно-импульсных преобразователей подключен к низкочастотному выходу делителя частоты и входу генератора функций Уолша, 25 выходы которого соединены с соответствующими информационными входами комбинационно-логического блока, базисные входы которого подключены .к соответствующим выходам генератора З0 функций Уолша, выходы комбинационнологического блока подключены к соответствующим управляющим входам усилителя мощности, выходы которого являются выходами устройства, о т л ичающее с я тем, что, с целью улучшения энергетических и динамических характеристик преобразователя и расширения его функциональных возможностей, в него введены делитель

94 8 частоты, блок анализатора спектра

Уолша, первый и второй блок сумматоров, блок цифроаналоговых преобразователей, блок фильтра низкой частоты и блок ключей, причем вход делителя частоты соединен с выходом генератора тактовых импульсов, его высокочастотный выход — с входами считывания блока анализатора спектра Уолша, а его низкочастотный выход — входом синхронизации блока анализатора спектра Уолша и входом генератора функций Уолша, основные выходы которого соединены с соответствующими управляющими входами блока ключей и базисными входами блока анализатора спектра Уолша, вход спектрального разложения сигнала которого соединен с выходом блока фильтров низкой частоты, входы которого подключены к выходам устройства, выходы блока анализатора спектра

Уолша соединены с соответствующими первыми входами первого блока сумматоров, вторые входы первого блока сумматоров подключены к соответствующим первым входам второго блока сумматоров, которые являются входа— ми устройства, причем вторые входы второго блока сумматоров соединены с соответствующими выходами первого блока сумматоров, а выходы второго блока сумматоров подключены к соответствующим входам блока цифроаналоговых преобразователей, выходы которого соединены с соответствующими коммутационными входами блока ключей, выходы которого подключены к соответствующим входам суммирования блока широтно-импульсных преобразователей.

Фиг.2

1274094

РигЗ

Составитель Е.Калинкин

Редактор М.Бандура . Техред В.Кадар Корректор А.Обручар

Тираж 631 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6487/55

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4