Многофункциональный логический модуль

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной , технике и микроэлектронике и предназначено для построения устройств цифровой обработки. Цель изобретения - повышение быстродействия . Устройство содержит элементы И-НЕ 3 и 4, транзисторы 5-7, элементы 8-10 РАВНОЗНАЧНОСТЬ. Реализация элементов И-НЕ 3 и 4 и элементов 8-10 РАВНОЗНАЧНОСТЬ на МОП-транзисторах позволяет увеличить быстродействие модуля в 1,5 раза. I табл., 1 ил.

СОЮЗ СОВ ЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (19) ЯО (и! др 4 Н 03 K 19/017

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3864527/24-21 (22} 12,03,85 (46) 30,11.86. Бил. Р 44 (72} В. И. Бенкевич, Л. Б, Авгуль, В. А. Мищенко и М, M ° Татур (53) 681.325.65(088.8} (56) Авторское свидетельство СССР

Я- 718928, кл. Н 03 К 19/00, 1980, Авторское свидетельство СССР, Ф 1213537, кл. Н 03 К 19/00, 1984. (54) МНОГОФУНКЦИОНАЛЬНЫЙ ЛОГИЧЕСКИЙ

МОДУЛЬ (57) Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения устройств цифровой обработки. Цель изобретения — повышение быстродействия. Устройство содержит элементы

И-НЕ Э и 4, транзисторы 5-7, элементы 8-10 РАВНОЗНАЧНОСТЬ. Реализация элементов И-HE 3 и 4 и элементов 8-10 РАВНОЗНАЧНОСТЬ на МОЛ-транзисторах позволяет увеличить быстро- действие модуля в 1,5 раза, 1 табл., 1 ил.

1274148

Изобретение относится к вычислительной технике и микроэлектронике и предназначено для построения устройств цифровой обработки.

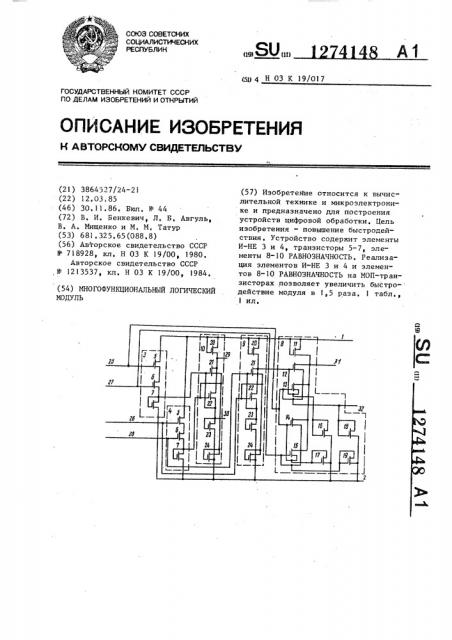

Целью изобретения является повы" шение быстродействия, На чертеже показана структурная схема многофункционального логического модуля, Между шинами питания 1 и 2 включены цепочки МОП-транзисторов, образующие первый 3 и второй 4 элементы

И-НЕ на два входа (транзисторы 5-7), первый 8, второй 9 и третий 10 элементы РАВНОЗНАЧНОСТЬ (транзисторы

11- 19 и 20-24 соответственно). Каждый элемент И-НЕ выполнен на двух переключательных 5 и 6 и одном нагрузочном 7 транзисторах, Второй и третий элементы РАВНОЗНАЧНОСТЬ на два входа состоят из последовательно включенного нагрузочного транзистора 20 и двух параллельно включенных ветвей, каждая из которых состоит из последовательно включенных переключательного 21 и второго нагрузочного 24 транзисторов соответственно для одной ветви, и 22 и 23— для другой ветви. Первый элемент

РАВНОЗНАЧНОСТЬ на трн входа состоит из четырех переключательных 12-15 и пяти нагрузочных 11, 16 — 19 транзисторов. Прямые и инверсные выходы первого и третьего элементов равнозначность являются выходами модуля.

Модуль работает следующим образом, На информационные входы 25 и 26 поступают входные переменные Х 1 и

Х 2 соответственно, Одновременно на настроечные входы 27 и 28 подактся сигналы настройки И 1 и И 2 соответственно, При этом на выходах устройства 29 — 32 реализуются логические функции в соответствии с приведенной таблицей, Формула изобретения

Многофункциональный логический модуль на NOII-транзисторах, реализующий все логические функции двух переменных, содержащий два элемента

И-НЕ и три элемента РАВНОЗНАЧНОСТЬ и имеющий два информационных и два настроечных входа, первый информационный вход соединен с первым входом первого элемента И-НЕ и с первым

1 входом первого элемента РАВНОЗНАЧНОСТЬ, второй информационный вход соединен с первым входом второго .элемента И-НЕ и с первым входом вто5 рого элемента РАВНОЗНАЧНОСТЬ, первый настроечный вход соединен с вторым входом первого элемента И-НЕ и с вторым входом первого элемента

РАВНОЗНАЧНОСТЬ, второй настроечный вход соединен с вторым входом второго элемента И-НЕ и с вторым входом второго элемента РАВНОЗНАЧНОСТЬ, отличающийся тем, что, с целью повышения быстродействия, l5 выходы элементов И-НЕ соединены с соответствующими входами третьего элемента. РАВНОЗНАЧНОСТЬ, а прямой выход второго элемента РАВНОЗНАЧНОСТЬ соединен с третьим входом

20 первого элемента РАВНОЗНАЧНОСТЬ, прямые и инверсные выходы первого и третьего элемента РАВНОЗНАЧНОСТЬ являются выходами модуля, первый и второй элемент И"НЕ реализованы на

25 МОП-транзисторах включением цепочки из первого и второго переключательных и первого нагрузочного транзисторов между шинами питания, затворы первого и второго переключатель30 ных транзисторов являются входами логического элемента, а затвор нагрузочного транзистора соединен со стоком и является выходом логического элемента, второй и третий элементы РАВНОЗНАЧНОСТЬ реализованы на

МОП-транзисторах и состоят из последовательно включенного второго нагрузочного транзистора и двух ветвей, которые соединены параллельно, 40 каждая из которых состоит из третьего переключательного и третьего нагруэочного транзисторов, которые соединены последовательно, затвор третьего переключательного транзистора первой ветви соединен с истоком третьего переключательного транзис- тора второй ветви и является первым входом логического элемента, затвор третьего переключательного транзистора второй ветви соединен с истоком третьего переключательного транзистора первой ветви и является вторым входом логического элемента, затзатвор третьего нагрузочного транзистора первой ветви соединен со стоком, затвор третьего нагрузочного транзистора второй ветви соединен со стоком и является инверсным выходом логического элемента, а ис1274148

Функции, реализуемые на выходах

Сигналы на входах настройки

2 J 4

l6 17 28 33

Х1Х2 Х1ЧХ2

Х2 Х1Х2 Х1ЧК2

Х! XlX2 X1VX2

Хl.О+ Х2 Х1Х2 Х1ЧХ2

Хl

X20+ Х2

Составитель О. Скворцов

Редактор 3, Слиган Техред И.Попович

Корректор В. Бутяга

Заказ 6490 /5 8 Тираж 816

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д. 4/5 .

Подписное

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная, 4 ток второго нагрузочного транзистора является прямым выходом логического элемента, а первый элемент

РАВНОЗНАЧНОСТЬ на три входа реализован на МОП-транзисторах, образован путем последовательного включения между шинами питания четвертого нагруэочного транзистора и четырех ветвей, которые включены параллельно, каждая состоит из четвертого переключательного и пятого нагруэочного транзисторов, которые соединены последовательно, затвор четвертого переключательного транзистора первой ветви соединен с истоком четвертого переключательного транзистора второй ветви и является первым входом логического элемента, затвор переключательного транзистора второй ветви соединен с затвором четвертого переключательного транзистора четвертой ветви и с истоками четвертых переключательных транзисторов первой и тре тьей ветви и является вторым входом логического элемента, затвор четвертого переключательного транзистора третьей ветви соединен с исtO током четвертого переключательного транзистора четвертой ветви и является третьим входом логического элемента, затворы четвертого и пятых нагрузочных транзисторов соединещю с их стоками, исток четвертого нагрузочного транзистора является прямым, а сток пятого нагрузочного транзистора первой ветви— инверсным выходами логическогоэлемента.