Преобразователь параллельного кода в последовательный

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике. Его использование в системах передачи и преобразования цифровых данных обеспечивает упрощение и повышение быстродействия. Преобразователь параллельного кода в последовательный содержит генератор импульсов, регистр, элемент задержки , элемент ИЛИ и группу из п элементов И. Введение группы из п-1 элементов ИЛИ позволяет начинать преобразование сразу после записи входного кода без определения положения лидирующего бита. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУбЛИК (1% (ll) А1 (бц 4 Н 03 M 9/00

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3913868/24" 24 (22) 19.06,85 (46) 30.11 ° 86. Бюл. В 44 (72) О, П. Орлов,. 10. Ф. Иостак и Б, И, Чванов (53) 681, 325(088. 8) (56) Авторское свидетельство СССР

У 1 1 19002, кл. G Об F 5/04, 15. 04, 83.

Авторское свидетельство СССР

У 898419, кл. G 06 Р 5/04, 03.03.80. (57) Изобретение относится к вычислительной технике. Его использование в системах передачи и преобразования цифровых данных обеспечивает упрощение и повыщение быстродействия.

Преобразователь параллельного кода в последовательный содержит генератор импульсов, регистр, элемент задержки, элемент ИЛИ и группу из и элементов И, Введение группы из п-1 элементов ИЛИ позволяет начинать преобразование сразу после записи входного кода беэ определения положения лидирующего бита, 1 ил. (54) ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО

КОДА В ПОСЛЕДОВАТЕЛЬНЫИ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

1274159

10 !

Изобретение относится к вычислительной технике и может быть использовано в системах передачи и обработки цифровых данных.

Цель изобретения — упрощение и повышение быстродействия.

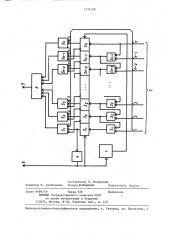

На чертеже приведена функциональная схема устройства, Преобразователь параллельного кода в последовательный содержит генератор 1 импульсов, группу из (n-1)-го элемента ИЛИ 2, регистр 3, содержащий и разрядов, элемент 4 за" держки, группу из и элементов И 5, элемент ИЛИ 6, информационные входы

7, управляющий выход 8 и информационный выход 9, Преобразователь работает следующим образом.

В исходный момент времени регистр

3 находится в нулевом состоянии и на выходе элемента 4 задержки присутствует нулевой потенциал, разрешающий запись преобразуемого кода с информационных входов 7 через группу элементов ИЛИ 2 в регистр 3, Разряды преобразуемого кода и разряды регистра 3 совмещаются по первому (младшему) разряду, Момент завершения записи в регистр 3 определяется наличием высокого потенциала на выходе элемента 4 задержки, величина задержки которого определяется временем распространения сигнала с входа (n-1)-го элемента ИЛИ 2 группы на выход первого элемента ИЛИ 2 группы, Высокий уровень сигнала с выхода элемента 4 подается на управляющий вход (вход блокировки записи) регистра 3, на управляющий вход 8 и вход запуска генератора 2 импульсов. На информационном выходе 9 присутствует уровень сигнала, соответствующий значению лидирующаго быта преобразуемого кода, Положительный период напряжения па управляющем выходе 8 характеризует начало преобразования, а отрицательный — конец, Генератор 1 импульсов, воздействуя на вход сдвига регистра 3, производит в нем серию последовательных одноразрядных (до полного обнуления регистра 3) сдвигов, в результате которых на информационном выходе 9 последовательно появляются уровни потенциалов, соответствующие значениям следующих эа старшим битом преобразуемого кода, После последнего сдвига регистр

3 обнуляется и отрицательный перепад напряжения на выходе элемента 4 задержки обозначит конец преобразования и остановит генератор 1 импульсов. В итоге преобразователь окажется в состоянии готовности к обработке следующего кода без предварительной подготовки.

Данный преобразователь не требует предварительного знания формата преобразуемого кода, что позволяет проводить преобразование к-разрядного кода за к тактов без предварительного определения места лидирующей единицы в коде. формула изобретения

Преобразователь параллельного кода в последовательный, содержащий генератор импульсов, элемент задержки, элемент ИЛИ, группу из и элементов И, где п - разрядность входного кода„ и регистр, прямые выходы разрядов которого подключены к первым входам соответствующих элементов И группы, выходы которых соединены с входами элемента ИЛИ, выход которого является информационным выходом устройства, отличающийся тем, что, с целью упрощения и повышения быстродействия, в него введена группа из п-1 элементов ИЛИ, первые входы которых объединены с вторыми входами соответствующих элементов И группы и являются соответствующими информационными входами устройства, выход i-ro элемента ИЛИ группы подключен к информационному входу соответствующего разряда регистра и к второму входу (i-1)-го элемента

ИЛИ группы, информационный вход и-го разряда регистра объединен с вторыми входами (n-1)-го элемента ИЛИ группы и п-го элемента И группы и является и-м информационным входом устройства, инверсный выход 1-го разряда регистра, кроме первого, подключен к третьему входу (i-1)-го элемента И группы, прямой выход первого разряда регистра соединен с входом элемента задержки, выход которого подключен к управляющему входу регистра и входу запуска генератора импульсов и является управляющим выходом устройства, выход генератора импульсов соединен с входом сдвига регистра, 1274159

Составитель О. Ревинский

Редактор Н, Слободяник Техред И. Попович Корректор В. Бутя га

Заказ 6490/58 Тираж 816

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4