Устройство для контроля интегральных микросхем оперативной памяти

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислиtejibHofl технике и может быть исполь .зовано для функционального контроля интегральных микросхем оперативной памяти. Целью изобретения является повышение достоверности контроля. Устройство содержит генератор импульсов , цифровой компаратор, регистратор брака, счетчик-делитель, коммутатор, счетчик адреса, мультиплексор , элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент развязки. В устройстве обеспечивается формирование тестовой последовательности , использукицей в качестве данных для проверки прямые и инверсные значения всех разрядов адреса контролируемой микрдсхё йГ па-; мяти. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (!1) (5!) 4 С 11 С 29 00

-»

1

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, "

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К ABTOPCHOMY СВИДЕТЕЛЬСТВУ (21) 3599808/24-24 (22) 02.06.83 (46) 07.12.86, Бюл. Ф 45 (72) А,Н.Бучнев, Н.П.Васильев и Е.И.Карпунин (53) 681.326.7(088.8) (56) Авторское свидетельство СССР

В 947913, кл. С 11 С 29/00, 1980, Авторское свидетельство СССР

1(530287, кл. G 01 R 31/28, 1978. (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ИНТЕГРАЛЬНЫХ МИКРОСХЕМ ОПЕРАТИВНОЙ ПАМЯТИ (57) Изобретение относится к вычислитедьной технике и может быть исполь;.зовано для функционального контроля интегральных микросхем оперативной памяти. Целью изобретения является повышение достоверности контроля.

Устройство содержит генератор импульсов, цифровой компаратор, регистратор брака, счетчик-делитель, коммутатор, счетчик адреса, мультиплексор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент развязки. В устройстве обеспечивается формирование тестовой последовательности, использующей в качестве данных для проверки прямые и инверсные значения всех разрядов адреса контролируемой микросхемЫ па-, мяти. 1 ил.

1275548 2, цу, т.е, в памяти пропишется инфор мация

Изобретение относится к вычислительной технике и может быть использовано для.фуйкционального контроля интегральных микросхем оперативной памяти.

Целью изобретения является повы-: шение достоверности контроля.

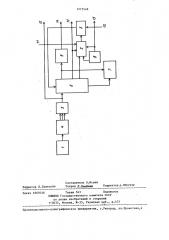

На чертеже представлена функциональная схема устройства.

Устройство содержит генератор 1 19 импульсов, цифровой компаратор 2,регистратор 3 брака, счетчик-делитель

4, коммутатор 5, счетчик 6 адреса, мультиплексор 7, элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ 8, элемент 9 развязки, управляющий вход 10, информационный вход 11, первый t2 и второй 13 управляющие выходы, а также адресный 1.4 и информационный 15 выходы.

Устройство работает следующим об- ZO разом.

В исходном состоянии регистратор

3 брака находится в состоянии "Не годен" и низким уровнем напряжейия с выхода блокирует по установочному входу счетчик 6 адреса, выходы которого находятся. в нулевом состоянии.

При подаче сигнала "Пуск" на управля,ющий вход 10 устройства регистратор

3 брака переходит в режим "Годен" и разрешает счет счетчику 6 адреса,на, вход которого поступает одна из частот c выхода счетчика-делителя 4.

Частота устанавливается коммутатором 5 в зависимости от быстродействия испытуемой микросхемы оперативной памяти. Все выходы счетчика 6 адреса находятся в нулевом состоянии, поэтому (п + 1)-й выход. задает режим "Запись" для испытуемой микро Щ . схемы памяти по первому управляющему выходу, а также запрещает работу цйфрового компаратора 2. На адресный выход 14 устройства поступают все нули, 4$

01010101 ... 01, 10101010 ... 10, зз после чего произойдет сравнение, запись инверсной информации

t 10011001100 ... 1100

В

Мультиплексор 7 коммутирует информацию с младшего разряда счетчика

6 адреса, так как íà его управляющие входы поступают нулевые сигналы.Информация с мультиплексора 7, не инвертируясь на схеме ИСКЛЮЧАЮЩЕЕ ИЛИ

8, поступает на информационный вход

15 устройства. Таким образом, первым тактовым импульсом ло нулевому адресу в испытуемую микросхему запишется лргический нуль. Следующий тактовый импульс добавит единицу к адресу и по этому адресу запишет единиКогда пропишется вся память,(п +

+ 1)-й разряд счетчика 6 адреса установится в состояние единицы, что разрешит работу цифрового компара- . тора 2 и переведет режим работы испытуемой микросхемы памяти в режим

"Чтение", а п младших адресных разрядов двоичного управляющего счетчика обнуляется. Теперь в каждом тактовом импульсе происходит сравнение записанной в испытуемую микросхему памяти информации с младшим адресным разрядом, поступающим через мультиплексор 7 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ Я.на вторую группу входов цифрового компаратора 2. Если хотя бы по одному адресу произойдет несравнение, то регистратор брака

3 перейдет в состояние "Не годен" и заблокирует счет счетчика 6 адреса.

Если несравнения не произошло, то счетчик досчитает до (n + 2)-х на (и + 2)-м выходе появится единица,. а младшие (п + 1) разряды счетчика обнулятся. В этом случае цикл записи начинается снова, аналогично описанному способу, с той лишь разницей,что элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

8 начинает инвертировать информа" цню с младшего адресного разряда, а в испытуемую микросхему памяти пропишется инверсная информация после чего произойдет сравнение запйсанной информации с эталонной

Если не произошло несравнение,то (n + 3)-й разряд счетчика 6 адреса установится в единицу, а (n + 2) младших разрядов счетчика 6 адреса обнулятся.В этом случае через муль типлексор 7, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ

8 на информационный выход устройства поступает информация со следующего адресного разряда и в память пропишется информация 001 1001 1001 1 ... 0011, 12 и опять сравнение. Точно таким же образом происходят циклы записи чтения для всех остальных адресных выходов счетчика 6 адреса. Две последние комбинации, когда память прописывается старшим адресным кодом, выгля,дят следующим образом:

000 ... 000111 ... 111

111 ... 111000 ... 000, где нули и единицы занимают ровно половину объема испытуемой микросхемы.

Если в течение определенного времени (характерного для каждого типа испытуемой микросхемы) не произошло несравнения, микросхема признается годной. формула изобретения

Устройство для контроля интегральных микросхем оперативной памяти,содержащее генератор импульсов, цифровой компаратор и регистратор брака, первый вход которого является управляющим входом устройства, о т л и— ч а ю щ е е с я тем, что, с целью повышения достоверности контроля, в него введены счетчик-делитель, коммутатор, счетчик адреса, мультиплек75548 4 сор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ и элемент развязки, причем вход счетчикаделителя подключен к выходу генератора импульсов, а выходы соединены с входами коммутатора, выход которого подключен к синхровходу счетчика адреса и является первым управляющим выходом устройства, выходы первой группы счетчика адреса соединены с

1а входами элементов развязки и информационными входами мультиплексора, управляющие входы которого подключены к входам второй группы счетчика адреса, а выход соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому информационному входу цифрового компа-. ратора и является информационнйм выходом устройства, один выход счет щ чика адреса соединен с управляющим входом цифрового компаратора и является вторым управляющим выходом устройства, а другой в яход подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ

ИЛИ, второй информационный вход цифрового компаратора является информационным входом устройства, в выход подключен к второму входу регистратора брака, выход которого соединен с установочным входом счетчика адреса, выходы элементов развязки являются адресными выходами устройства.

1275548

Составитель О,Исаев

Техред Д.Олейник Корректор А.Обручар

Редактор Л.Гратилло

Заказ 6569/46

Тираж 543 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г,Ужгород, ул.Проектная,4