Логический элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в цифровых логических схемах. Цель изобретения - повышение быстродействия и уменьшение потребляемой мощности. Устройство содержит фазоразделительный транзистор 1, много змиттерный транзистор 2, формирователь 17 опорного напряжения, -транзисторы 6, 9, 11, 14, резисторы 4, 15, 16, 19. Для достижения поставленной цели в устройство введены транзистор 12, транзисторный шунт 8, резисторы 7, 13, 18. 1 з. п.ф-лы ,1 ил. (Л 01 сл оо

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1275758 А 1 ао 4 Н Q3 К 19/088

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ! !

Н А BTOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3950566/24-21 (22) 30.08.85 (46) 07.12.86. Бюл. У 45 (72) В.Н. Синеокий, В.А. Липко, А.П. Трещун и Ю.Н. Еремин (53) 621.374(088.8) (56) Авторское свидетельство СССР

У 1058061, кл. Н 03 К 19/00, 1982.

Авторское свидетельство СССР

Р 1228260,кл. Н 03 К 19/088, 1984. (54) ЛОГИЧЕСКИЙ 3JIEMEHT (57) Изобретение относится к импульсной технике и может быть использовано в цифровых логических схемах.

Цель изобретения — повышение быстродействия и уменьшение потребляемой мощности. Устройство содержит фазоразделительный транзистор 1, много" эмиттерный транзистор 2, формирователь 17 опорного напряжения, .транзисторы 6, 9, 11, 14, резисторы 4, 15, 16, 19. Для достижения поставленной цели в устройство введены транзистор 12, транзисторный шунт 8, резисторы 7, 13, 18. 1 з. п.— ф-лы, 1 ил. Х

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 3

1275758

ЗО

4О

Изобретение относится к импульсной технике и может быть использовано в цифровых логических схемах., Цель изобретения — увеличение быстродействия и уменьшение потребляемой мощности.

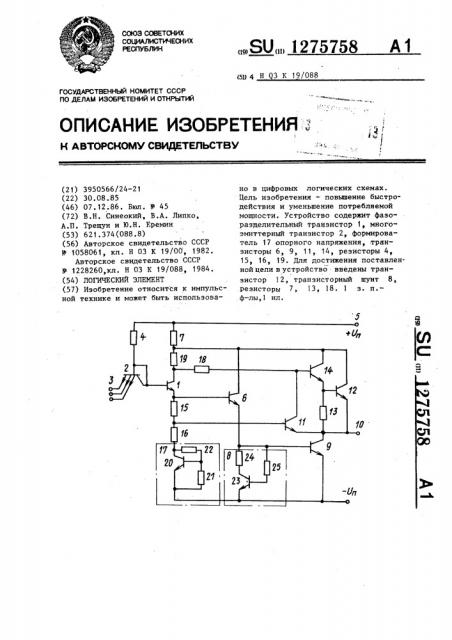

На чертеже представлена принципиальная электрическая схема логического элемента. Логический элемент содержит фазоразделнтельный транзистор 1, база которого через входной многоэмиттерный транзистор 2 подключена к входам 3, при этом эмиттеры транзистора 2 подключены к входам 3, база через резистор 4 соединена с шиной 5 питания и подключена к его коллектору и базе транзистора 1, эмиттер которого соединен с базой первого транзистора 6, коллектор которого через первый резистор 7 соединен с шиной 5 питания, а эмиттер через транзисторный шунт

8 соединен с общей шиной и подключен к базе второго транзистора 9. Эмиттер транзистора 9 соединен с общей шиной, а коллектор подключен к выходу 10 и эмиттерам третьего 11 и четвертого 12 транзисторов 11 и 12 и через второй резистор 13 соединен с базой четвертого 12 и эмиттером пятого 14 транзисторов, коллекторы которых соединены. База пятого транзистора 14 соединена с коллектором третьего транзистора 11, база которого .подключена через третий резистор 15 к эмиттеру транзистора 1 и через последовательно соединенные четвертый резистор 16 и формирователь 17 опорного напряжения к общей шине. Коллектор транзистора 1 через пятый резистор 18 соединен с базой пятого транзистора 14 и через шестой резистор 19 подключен к коллекторам первого 6 и четвертого 12 транзисторов.

Формирователь 17 опорного напряжения выполнен на опорном транзисторе 20, база которого через соответствуюшие резисторы 21 и 22 соединена с его эмиттером и коллектором. Транзисторный шунт 8 выполнен на шунтирующем транзисторе 23, змиттер которого подключен к общей шине, а коллектор и база через соответствующие резисторы 24 и 25 соединена с эмиттером транзистора 1.

Логический элемент работает следующим образом.

При подаче высокого уровня напряжения логической "1 на все входы логического элемента эмиттерные переходы транзистора 2 закрыты. Ток через резистор 4, закоротку между переходом база — коллектор транзистора

2.поступает в базу фаэораспределительного транзистора 1 и открывает его. Эмиттериый ток транзистора 1 течет в цепь из резисторов 15 и 16: и формирователь 17 опорного напряжения, а также в базу транзистора 6, Быстрое включение транзистора 6, а следовательно, транзистора 9 обеспечивается высоким уровнем базовых токов транзисторов 9 и 6, уровень которых определяется резисторами 19 и 7. Увеличению быстродействия логического элемента способствует транзисторный шунт 8, включающийся и выключающийся с замедлением, определяемым соотношением резисторов 24 и

25, по сравнению с включением и выключением выходного тразистора 9.

При достижении на выходе 10 напряжения! 21 R1C

U U + вы х Б э1о В.

Еээ R + Р

15 где U, U — падение напряжения на Э2 переходах база — эмиттер транзисторов 20 и 9; кл к а кг„к22 — сопротивления ре»сто ров 15, 16,21 и 22, открывается транзистор 11 и нэбыточ" ная часть базового тока транзистора

6, задаваемого резисторами 19 и 7, отводится через резистор 18 в коллектор транзистора 1. При этом внутренняя помехозащищенность логического элемента улучшается за счет падения напряжения на резисторах 18 и 7, так как более эффективно блокируется переход база. — эмнттер транзистора

14 и уменьшается уровень сквозного тока через транзистор 12.

Так как резистор 7 является общим резистором в коллекторных цепях (элементом обратной связи) транзисторов

1,14,6,11 и 12, наличие тока через один из транзисторов способствует уменьшению тока через другой. При этом исключается возможность насыщения и потери быстродействия транзистора 6, а .также возможность протекания значительных сквозных токов через транзисторы 14 и 12 при открытых транзисторах 6 и 11. В результате

1275758

Формула изобретения

1 1

41; — — — — — — с(1.

RZ, К(+ К4

Когда хотя бы на один вход 3 логического элемента подано напряжение логического "0", фаэоразделительный транзистор 1 закрывается, следовательно„ закрываются транзисторы, так

Составитель А. Янов

Техред Л. Олейник

Корректор Т. Колб

Редактор В. Петраш

Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6581/57

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная,. 4 этого повьппается быстродействие, эко номичность и надежность логического элемента. Уменьшение базового тока транзистора 9 за счет обратной связи через резистор 18 и транзистор 11 5 обеспечивает снижение тока в базу транзистора 9 и таким образом ограничивает степень его насыщения.

Иэ приведенного выражения для

U,, логического элемента видно, t0

Ьыя что выходное напряжение логического

"0" элемента связано с падением напряжения на переходах база — эмиттер транзисторов 9 и 20 и зависит от резисторов 21,22 15 и 16, величина ко- >5 торых выбирается так, чтобы

Причем первая составляющая выходного 20 напряжения эмиттера не зависит от уровня базового тока транзистора 9, вторая составляющая обеспечивает прирост выходного напряжения логического "0" элемента, обусловленный ростом напряжения US с увеличением базового тока. Таким образом, обеспечивается активный режим работы транзистора 9 и быстродействие элемента при минимально необходимом изменении ÇO напряжения U обусловленном снижевы нием коэффициента усиления транзисторов или ростом тока нагрузки на выходе 10. Это позволяет сочетать быстродействие элемента с высокой помехо-З защищенностью по выходу. В то же время незначительный рост выходного

1 напряжения U b» при больших базовых токах транзистора 9 обеспечивает более эффективную отсечку сквозного то-40 ка и компенсирует уменьшение напряжения на резисторе 18. как в цепях их баз отсутствует ток, и на выходе 10 логического элемента формируется напряжение логической 1 через резисторы 18, 19,7 и ycab» коряющую цепь, выполненную на транзисторах 14 и 12.

1. Логический элемент, содержащий шесть резисторов, фазоразделительный транзистор, база которого подключена к входу, а эмиттер соединен с базой первого транзистора, коллектор которого через первый резистор соединен с шиной питания, а эмиттер через транзисторный шунт подключен к общей шине и соединен с базой второго транзистора, эмиттер которого соединен с общей шиной, а коллектор подключен к выходу и эмиттерам третьего и четвертого транзисторов и через второй резистор соединен с базой четвертого и эмиттером пятого транзисторов, коллекторы которых соединены, база пятого транзистора соединена с коллектором третьего транзистора, база которого через третий резистор подключена к эмиттеру фазоразделительного транзистора и через последовательно соединенные четвертый резистор и формирователь опорного напряжения подключена к общей шине, о т л и ч а ю— шийся тем, что, с целью увеличения быстродействия и уменьшения потребляемой мощности, коллектор фаэоразделительного транзистора через пятый резистор соединен с базой пятого транзистора и через шестой резистор подключен к коллекторам первого и четвертого транзисторов.

2. Элемент по п. 1, о т л и ч а юшийся тем, что формирователь опорного напряжения выполнен на опор- ном транзисторе, база которого через соответствующие резисторы соединена с его эмиттером и коллектором.