Одноразрядный сумматор на инжекционных элементах

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и предназначено для суммирования операндов в многоуровневой логике. Делью изобретения является расширение области применения за счет суммирования операндов , представленных в прямом коде. Это достигается введением в состав одноразрядного сумматора дополнительно токового отражателя и порогового детектора. Это позволяет исключить необходимость подачи на входы сумматора одновременно прямых и инверсных значений входных аргументов. 1 ил. со О)

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (И) цр 4 G 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К А ВТОРСКОМУ СВИДЕТЕВЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3883833/24-24 (22) 15, 04. 85 (46) 15.12.86, Вюл. Р 46 (71) Ленинградский ордена Ленина и ордена Октябрьской Революции институт инженеров железнодорожного транспорта им.акад.В.Н.Образцова (72) В.А.Журкин (53) 681.325.5(088.8), (56) Авторское свидетельство СССР

У 1095174, кл. G 06 F 7/50, 1982.

Авторское свидетельство СССР

Р 1213476, кл. G 06 F 7/50, !984. (54) ОДНОРАЗРЯДНЫЙ СУММАТОР НА ИНЖЕКЦИОННЫХ ЭЛЕМЕНТАХ (57) Изобретение относится к области вычислительной техники и предназначено для суммирования операндов в многоуровневой логике. Целью изобретения является расширение области применения за счет суммирования операндов, представленных в прямом коде.

Это достигается введением в состав одноразрядного сумматора дополнительно токового отражателя и порогового детектора. Это позволяет исключить необходимость подачи на входы сумматора одновременно прямых и инверсных значений входных аргументов. 1 ил.

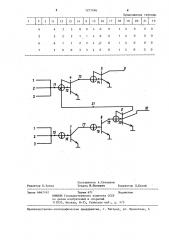

2 3 ii 12 I 13 14 9 15 16 17 18 f9 20 21 10

0 3 3 О О О 4 1 О О 4 4 4

1 2 2 1 1 1 3 1 О 0 4 4 4

2 1 i 2 2 2 2 1 0 О 4 4 4

3 О 0 3 3 3 1 1 0 О 4 4 4

1 12770

Изобретение относи ся к вычиспительной технике и может быть иснользовано при построении интегральных микросхем обработки цифровой информации в многозначной логике.

Цель изобретения — расширение области применения одноразрядного сумматора за счет суммирования операндов, представленных в прямом коде.

На чертеже изображена принципи- 1О альная схема одноразрядного сумматора на инжекционных элементах.

Одноразрядный сумматор содержит входы 1,2 и 3 многозначных аргумен.тов (k-значных),причем вхоц 3 предназначен для подачи двухзначного входного переноса, таковые отражатели

4-6, пороговые детекторы 7 и 8, выход 9 суммы, выход 10 инверсного значения переноса. Контрольные точки обозначены позициями 11-21, Пороговые детекторы и токовые отражатели выполнены в виде и-р-и-транзисторов с инжекционным питанием н цепь базы.

При k=4 в базы транзисторов„ образующих токовые отражатели 4-6 и пороговые детекторы 7 и 8, инжектируются токи, соответствующие 7, 3, .4. 4

И 1 epHHHIJBMе

При произвольном к в базы транзисторов должны инжектироваться токи, соответствующие 2k-f, k-1, k, k H единицам.

Для насыщения соответствующего транзистора необходим вхс>днои ток

35 в одну единицу. При этом токовый отражатель своим выходом мажет отводигь- инжекционныи ток с входа последующего элемента, равный току, поступающему на его вход, а открытый

>» пороговый детектор может отводить весь инжекционный ток с входа поI сл едующе r а эл ем ен т а .

Одноразрядный сумматор для k-4 работает следующим образом.

На входах 1 и 2 операнцы принимают все возможные значения из множестваЕ=10, 1, 2, 3J, анавходе 3ь

96 2 из множества Е =1,0,, 1), следовательно„ входной вектор может быть представлен набором значений -О, 1, 2, 3, 4, 5, 6, 7 ) .

Тогда работу одноразрядного сумматора можно проиллюстрировать с помощью таблицы, где каждому значению входного тока поставлена в соответствие значение тоха в соответствующей точке.

При этом на выходе 10 переноса формируется инверсное значение переноса, где "О" сос>тветствует открытое состояние токового отражателя б (протекает ток в 4 единицы), а "1" закрытое.

Формула из обретения

Одноразрядный сумматор на инжекцианных элементах, содержащий первый порогавь.й детектор, первый и второй токовые отражатели, причем вход первого порогового детектора соединен с первой группой входов операндов одноразрядного сумматора, вход первого токового отражателя является выходом суммы, а первый выход второго такового отражателя является выходом переноса одноразрядного сумматора, о т л и ч а юшийся тем, ч..о, с целью расширения области применения а счет суммирования операндов, представленных в прямом коде, он дополнительно содержит второй пороговый детектор и третий токовый отражатель, причем выход первого порогового детектора соединен с входом второго порогового детектора, выход которого подключен к входу второго токового отражателя,, втарсй выход которого соединен с входам третьего токового отражателя и с второй группой входов аперандсв одноразрядного сумматора, выход третье о токового отражателя соединен с входом первого токового отражателя.

1277096

Продолжение таблицы

4 4 3 3 0 0 4 0 0 1 4 0 0 0

0 0

Составитель А.Степанов

Техред И.Попович

Редактор Е.Копча

Корректор Л.Патай

Заказ 6667/42

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

2 (5 2 2 1 1 4 0 0 1 4 0 0 0 г

6 1 1 2 2 4,0 0 1 4 0 0 0

7 0 0 3 3 4 О. 0 1 4 0

Тираж 671

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5