Устройство для вычитания

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано , например, в устройствах нормализации изображений. Цель изобретения - расширение функциональных возможностей за счет передачи операндов на выход устройства в дополнительном коде.Устройство для вычитания содержит п-разрядный сумматор 1, п-ра.зрядный компаратор 2, группу 3 из п элементов РАВНОЗНАЧНОСТЬ, группу 4 из п элементов И, группу 5 из п элементов И-НЕ, первый 6 и второй 7 элементы ИЛИ, первый 8, второй 9 и третий 10 элементы ИЛИ-НЕ, первый 11, второй 12 и третий 13 элементы И, первый 14 и второй 15 элементы НЕ, элемент РАВНОЗНАЧНОСТЬ 16, входную шину 17 первого операнда, входную шину 18 второго операнда, шину 19 задания режима работы устройства , шину 20 разрешения вьщачи результата в обратном коде, шину 21 разрешения выдачи результата в дополнительном коде, выход 22 устройства, выход 23 знака разности, выход 24 признака равенства, соединенные функционально . 1 ил. О)

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51) 4 С 06 F 7/50

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К A ВТОРСКОМЪ(СВИДЕТЕЛЬСТВУ

> . ь.

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3900870/24-24 (22) 23.05.85 (46) 15.12.86. Бюл. ¹ 46 (72) С.В.Галкин, В.Э.Голубицкий, Е.А.) аев, Б.Н.Иванов и В.М.Лискин (53) 681.325.5(088.8) (56) Титце У., Шенк К. Полупроводниковая схемотехника. M., Мир, 1983, с. 337, рис ° 19.35.

Авторское свидетельство СССР № 1133592, кл. G 06 F 7/50, 1983. (54) УСТРойство 1РИ ВЫЧИТАния (57) Изобретение относится к вычислительной технике и может быть использовано, например, в устройствах нормализации изображений. Цель изобретения — расширение функциональных возможностей за счет передачи операндов на выход устройства в дополнительном коде. Устройство для вычитания. SU„„12?7097 A 1 содержит и-разрядный сумматор 1, и-разрядный компаратор 2, группу 3 из и элементов РАВНОЗНАЧНОСТЬ, группу 4 из и элементов И, группу 5 из и элементов И-НЕ, первый 6 и второй 7 элементы ИЛИ, первый 8, второй 9 и третий 10 элементы KIH-HE, первый

11, второй 12 и третий 13 элементы И, первый 14 и второй 15 элементы НЕ, элемент РАВНОЗНАЧНОСТЬ 16, входную шину 17 первого операнда, входную шину 18 второго операнда, шину 19 задания режима работы устройства, шину 20 разрешения выдачи результата в обратном коде, шину 21 разрешения выдачи результата в дополнительном коде, выход 22 устройства, выход 23 знака разности, выход 24 признака равенства, соединенные функционально. 1 ил.

1277097

Изобретение относится к вычислительной технике и предназначено для вычисления разности двух операндов в прямом коде, определения равенства операндов и передачи операндов на выход устройства в прямом или дополнительном коде и может быть использовано, например, в устройствах нормализации изображений.

1О

Цель изобретения — расширение функциональных возможностей ус".гроиства за счет передачи операндов на выход устройства в дополнительном коде.

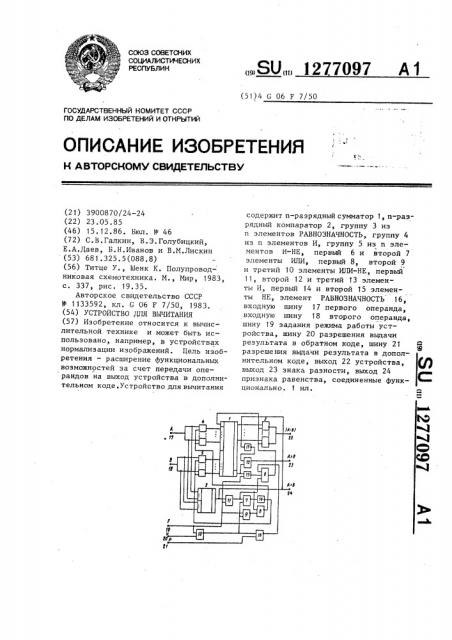

На чертеже изображена структурная схема устройства.

Устройство для вычитания содержит и-разрядный сумматор 1, и-разрядный компаратор 2, группу 3 из и элементов РАВНОЗНАЧНОСТЬ, группу 4 из и 2О элементов И, группу 5 из и элементов И-НЕ. первый 6 и второй 7 элементы КМ, первый 8, второй 9 и третий 10 элементы ИЛИ-НЕ, первый 11, второй 12 и третий 13 элементы И, первый 14 д и второй 15 элементы НЕ, элемент

РАВНОЗНАЧНОСТЬ 16, входную шину 17 первого операнда, входную шину 18 второго операнда, вход 19 задания режима работы устройства, вход 20 разрешения выдачи результата в обратном коде устройства, вход 21 разрешения выдачи результата в дополнительном коде, выход 22 устройства, выход 23 знака разности, выход 24 признака равенства.

Устройство для вычитания работает следуюшим образом.

Если на шине 19 задания режима работы устройства и на шине 21 разре4О шения выдачи результата в дополнительном коде присутствуют сигналы в виде логической единицы, то .устрой-. стов работает в режиме определения разности двух операндов в прямом коЯ де ° В этом случае сигнал логической единицы разрешает работу первого 11 и третьего 13 элементов И.

На вь!ходах второго 9 и третьего 10 элементов ИЛИ-НЕ образуются сигналы в виде логического нуля, которые разрешают работу второго элемента

ИЛИ 7 и первого элемента KIB1-НЕ 8.

На выходе элемента РАВНОЗНАЧНОСТЬ 16 получается сигнал в виде ло .аческого нуля.

Я

Если первый и второй операнды не равны по величине, то на выходе компаратора 2, а следовательно, и на выходе 24 признака равенства будет присутствовать сигнал в виде логического нуля. На выходе первого элемента И 11, следовательно, будет сигнал в виде логического нуля, а на выходе второго элемента HE 15 — в виде логической единицы. На вторых входах элементов И группы 4 и первых входах элементов И-НЕ группы 5 будут присутствовать сигналы в виде логической единицы. Таким образом, первый операнд поступает на первую группу входов сумматора 1 в прямом коде, а второй операнд — на вторую группу входов сумматора 1 в инверсном коде.

Если первый операнд по величине больше, чем второй операнд, то.на выходе переноса сумматора 1 будет присутствовать сигнал в виде логической единицы, который через третий элемент И 13 и первый элемент ИЛИ 6 поступает на вход переноса сумматора 1 и вторые входы элементов РАВНО13НАЧНОСТЬ группы 1, а через второй элемент И 12 — на выход 23 знака разности. kla выходах разрядов сумматора 1 получается разность операндов в прямом коде. Так как на вторых входах элементов РАВНОЗНАЧНОСТЬ группы 3 присутствует сигнал в виде логической единицы, то на выходе 22 разрядов устройства получается разность операндов в прямом кодеЕсли первый операнд по величине меньше, чем вторсй операнд, то на выходе переноса сумматора 1 будет сигнал в виде логического нуля, который через второй элемент И 12 поступает на выход 23 знака разности, а через третий элемент И 13 — на третий, вход первого элемента ИЛИ 6.

Так как на всех входах первого элемента ИЛИ 6 присутствуют сигналы в виде логического нуля, то на его выходе будет также сигнал в виде логического нуля,, который поступает на вторые входы .)лементов РАВНОЗНАЧНОСТЬ группы 3 и вход переноса сумматора 1. На выхздах разрядов сумматора 1 получается разность операндов в инверсном коде, а на выходе 22 разрядов устройсгва — в прямом коде.

Если первый операнд равен по величине второму операнду, то на выходе компаратора 2, а следовательно, и на выходе 24 признака равенства бу1277097

Если на шине 20 разрешения выдачи результата в обратном коде устройства присутствует сигнал в виде логической единицы, та ка выход 22 устройства поступает второй операнд.

В этом случае на выходах третьего элемента ИЛИ-НЕ 10 и элемента РАВIIОЗНАЧНОСТЬ 16 получаются сигналы в виде логического нуля. На выходе первого элемента ИЛИ-HI: 8 образуется также сигнал в виде лагическага нуля, который поступает на вторые входы элементов И группы 4 и обеспечивает поступление на первую группу входов сумматора 1 нулевого числа. На выходе первого элемента НЕ 14 образуется сигнал в виде логической единицы, дет сигнал в виде логической единицы. На выходе второго элемента НЕ 15, следовательно, будет сигнал в виде логического нуля, а на выходе первого элемента И 11 — в виде логической единицы. Сигнал в виде логического нуля с выхода второго элемента НЕ 15 блокирует второй элемент И 12. На выходе 23 знака разности получается сигнал в виде логического нуля. На вы1О ходах первого б и второго 7 элементов ИЛИ будут сигналы в виде логической единицы. На выходах первого элемента HJIH-НЕ 8 и первого элемента НЕ 14 присутствуют сигналы в виде логического нуля. Следовательно, на первую группу входов сумматора I поступает нулевой код, а на вторую группу — инверсный код числа нуль.

На выходах разрядов сумматора 1 образуется нулевой код, который проходит на выходы 22 разрядов устройства.

Если на шине 19 задания режима работы устройства присутствует сигнал в ниде логической .единицы, а на шине 21 разрешения выдачи результата в дополнительном коде — в виде логиЗО ческого нуля, то устройство работает в режиме определения алгебраической разности двух чисел. В этом случае на выходе элемента РАВНОЗНАЧНОСТЬ 16 получается сигнал в виде логической единицы, который через первый элемент ИЛИ 6 поступает на вторые вхо-. ды элементов РАВНОЗНАЧНОСТЬ группы 3 и вход переноса сумматора 1. На первую группу входов сумматора 1 операнд поступает в прямом коде, а на вторую 40 группу входов сумматора 1 — в инверс ном коде. На выходах разрядов сумматора 1 и выходах 22 разрядов устройства положительная разность образуется в прямом коде, а отрицательная — в дополнительном коде, а на выходе 23 знака разности фиксируется знак положительной разности в виде логической единицы, а отрицательнойв виде логического нуля.

Если на шине 19 задания режима ра боты устройства присутствует сигнал в виде логического нуля, а на шине

21 разрешения выдачи результата в дополнительном коде — в виде логической единицы, то устройство работает в режиме передачи операндов на выход 22 устройства в прямом коде.

В этом случае сигнал лагическсга нуля с шины 19 задания режима рабаты устройства блокирует работу первого 11 и третьего 13 элементов И и разблокирует второй элемент Юь1-НЕ 9.

Если на шине 20 разрешения выдачи результата в обратном коде устройства присутствует сигнал в виде логического нуля, то на выход 22 устройства наступает первый операнд.

На выходе третьего эл=-мента ИЛ11-НЕ 10 получается в этом случае сигнал в виде логической единицы, к; зрьп через элемент РАВНОЗНАЧНОСТ,6 и первый элемент ИЛИ 6 проходит па вторые входы элементов РАЬНОЗНАЧНОСТЬ группы 3, которые в этом случае не инвертируют сигнал с выходов раз рядов сумматора 1, и вход переноса самматора 1,. На выходе второго элемента ИЛИ-HE 9 образуется сигнал в виде логического куля, а на вы:.оде первого элемента HJBi-НЕ 8 — в виде логической единицы, котарьпЪ поступает на вторые входы элементов И группы 4, обеспечивая прохождение первого операнда на первую группу входов сумматора 1. На выходе второго элемента ИЛИ 7 получается сигнал в вчде логической единицы, а следовательно, на выходе первого элемента

НЕ 14. — в виде логического нуля, который поступает на первые входы элементов И-НЕ группы 5, обеспечивая поступление на вторую группу входов сумматора 1 инверсного када числа нуль. На выходах разрядов сумматора 1, а следовательно, и на выходах 22 разрядов устройства будет присутствовать первый операнд в прямом коде.

1277097

Фор мул а и з о б р е т е и и я

3 который разрешает прохождение инверс ного кода второго операнда на вторую группу входов сумматора 1. На выходе первого элемента ИЛИ 6 получается сигнал в виде логического нуля. Таким образом, на выходах разрядов сумматора 1 получается инверсный код второго операнда, а на выходе 22 разрядов устройства — прямой код второго операнда. 10

Если на шине 19 задания режима работы устройства и на шине 21 разрешения выдачи результата в дополнительном коде присутствуют сигналы в виде логического нуля, то устройство работает в режиме передачи дополнительного кода операндов на выход 22 устройства. В этом случае сигнал в виде логического нуля с шины 21 поступает на второй вход элемента РАВНОЗНАЧНОСТЬ 16. При передаче первого операнда на выходе третьего элемента ИЛИ-НЕ 10 получается сигнал в виде логической единицы, а на вы25 ходе элемента РАВНОЗНАЧНОСТЬ 16 в виде логического нуля. Следовательно, на выходе первого элемента

ИЛИ 6 будет сигнал в виде логического нуля, который поступает на вход переноса сумматора 1 и вторые входы элементов РАВНОЗНАЧНОСТЬ группы 3. На выходах элементов И-Hl"." группы 5 будут сигналы в виде логической единицы, а на выходах элемен- 35 тов И группы 4 будет присутствовать прямой код первого операнда. На выходах разрядов сумматора 1 получается прямой код числа, равного разности между первым операндом и едини- 40 цей. Следовательно, на выходах 22 разрядов устройства будет присутствовать дополнительный код первого операнда.

11ри передаче второго Операнда на выходе третьего элемента ИЛИ-НЕ 10 будет сигнал в виде логического. нуля, а на выходе элемента РАВНОЗНАЧНОСТЬ 16 — в виде логической едини50 цы. На выходе первого элемента ИЛИ 6 будет сигнал в ниде логической единицы. На выходах разрядов сумматора 1 получается число, равное сумме инверсного кода второго операнда и единицы, т.е. дополнительный код второго операнда, который проходит на выход 22 разрядов устройства.

Устройство для вычитания, содержащее и-разрядный сумматор (где п-разрядность операндов), и-разрядный компаратор, группу из и элементов РАВНОЗНАЧНОСТЬ, группу из и элементов И, первый и второй элементы HJIH первый, второй и третий элементы ИЛИ-НЕ, первый элемент И, причем первые входы элементов И группы поцключены к входам соответствующих разрядов первого операнда устройства и к соответствующим входам первой группы входов компаратора, вторые входы элементов И группы подключены к выходу первого элемента ИЛИ-НE, входы второй группы компаратора поцключены к соответствующим разрядам второго операнда устройства, выходы элементов И группы подключены соответственно к информационным входам первой группы и-разрядного сумматора, выходы соответствующих разрядов суммы которого соединены соответственно с первыми входами элементов РАВНОЗНАЧНОСТЬ группы, вторые входы которых подключены к выходу первого элемента ИЛИ, а выходы соединены соответственно с выходами разрядов модуля результата устроиства, выход компаратора соединен с первым входом первого элемента И и выходом признака равенства устройства, второй вход первого элемента И подключен к входу задания режима работы устройства и к первым входам второго и третьего элементов ИЛИ-НЕ, выход первого элемен-,à И соединен с первыми входами первого и второго элементов ИЛИ и первого элеме:.-ra ИЛИ-НЕ, второй вход которого соединен с выходом второго элемента ИЛИ-НЕ, втоpof» вход которого соединен с вторым входом второго элемента ИЛИ и выходом третьего элемента ИЛИ-IIE, второй вход которого соединен с входом разрешения выдачи результата в обратном коде устройства„ о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет передачи операндов на его выхоц в дополнительном коде, в него введены второй и третий элементы И, группа из и элементов И-HE элемент РАВНОЗНАЧНОСТЬ, первый и второй элементы НЕ, причем выход

1277097 с

Составитель И.Есенина

Техред И.Попович Корректор Л.Патай

Редактор Е.Копча

Заказ .6667/42

Тираж 671 Подписное

BHHHIIH Государственного комитета СССР по делам изобретений и открытий

113035, Иосква, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7 второго элемента ИЛИ соединен с входом первого элемента НЕ, выход которого соединен с первыми входами элементов И-НЕ группы, вторые входы которых соединены соответственно с входами разрядов второго операнда устройства, выходы элементов И-HE группы соединены соответственно с информационными входами второй группы и-разрядного сумматора, выход переноса которого подключен к первым входам второго и третьего элементов И, вход второго элемента НЕ подключен к выходу признака равенства устройства, а его выход соединен с вторым входом второго элемента И, выход которого соединен с выходом .знака разности устройства, первый вход элемента РАВНОЗНАЧНОСТЬ подключен к выходу третьего элемента

ИЛИ-НЕ, а второй его вход — к входу разрешения выдачи результата в дополнительном коде устройства, выход элемента РАВНОЗНАЧНОСТЬ соединеы с вторым входом первого элеменt0 та ИЛИ, третий вход которого соединен с выходом третьего элемента И, второй вход которого соединен с входом задания режима работы устройства, щ од переноса п-разрядного сум15 матора соединен с вторыми входами элементов РАВНОЗНАЧНОСТЬ группы.