Устройство для фиксации неустойчивых сбоев

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники. Цель изобретения - повьшение достоверности фиксации неустойчивых сбоев путей одновременной проверки большего числа тактов в каждом цикле. Устройство содержит два элемента И, четьфе счетчика , два блока сравнения, элемент ИЛИ- НЕ, два регистра, элемент ИЛИ, блок индикации, коммутатор и триггер. 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

-SU,, 127711

А1

m4 С 06 F 11/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABT0PCHOIVIY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И OTHPbITPM (21) 3896411/24-24 (22) 16.05.85 (46) 15. 12.86. Бюл. № 46 (72) В.С. Волощук, В.В. Лебедь, А.В. Дрозд, А.Г, Шипита и В.А. Соколов (53) 681.3(088.8) (56) Авторское свидетельство СССР

¹ 920732, кл. G 06 F 1 i/22, 1979.

Авторское свидетельство СССР № 1126965, кл. С 06 F 11/22, 1983. (54) УСТРОЙСТВО ДЛЯ ФИКСАЦИИ НЕУСТОЙЧИВЫХ СБОЕВ (57) Изобретение относится к области вычислительной техники. Цель изобретения — повышение достоверности фиксации неустойчивых сбоев путем одновременной проверки большего числа тактов в каждом цикле. Устройство содержит два элемента И, четыре счетчика, два блока сравнения, элемент ИЛИНЕ, два регистра, элемент ИЛИ, блок индикации, коммутатор и триггер.

1 ил.

1277117

Изобретение относится к вычислительной технике.

Цель изобретения — повышение достоверности фиксации неустойчивых сбо1 ев путем одновременной проверки большего числа тактов в каждом цикле.

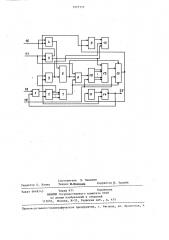

На чертеже изображена структурная схема устройства.

Устройство содержит первый элемент И 1, первый 2, второй 3, третий

4, четвертый 5 счетчики, первый блок

6 сравнения, элемент ИЛИ-НЕ 7, второй элемент И 8, второй 9 и первый

10 регистры, элемент ИЛИ 11, блок 12 индикации, коммутатор 13, триггер 14, второй блок 15 сравнения, вход 16 начальной установки устройства, тактовый вход 17 устройства, вход 18 запуска цикла контроля устройства, вход 19 контролируемой информационной последовательности и выход 20 . фиксации сбоя устройства.

Устройство работает следующим образом.

На вход 16 начальной установки устройства поступает сигнал, устанавливающий счетчики 2-5, регистр 9 и триггер 14 в нулевые состояния.

На вход 18 запуска цикла контроля поступает сигнал а, указывающий на начало очередного цикла контроля. В каждом цикле контроля на контролируемый информационный вход 19 устройст,ва поступает контролируемая последо-. вательность Ш -разрядных элементов I информации, воспроизводимая контролируемым объектом по одному и тому же алгоритму. Контролируемая информация поступает на входы сдвигового регистра 10 и блока 15 сравнения. Разрядность сдвигового регистра 10 определяется по формуле ш S где S — число одновременно контролируемых элементов информации, называемых группой.

Длительность цикла контроля определяется суммарной разрядностью третьего 4 и четвертого 5 счетчиков. На счетный вход четвертого 5 счетчика поступают синхросигналы, по которым осуществляется поступление элементов контролируемой информации. При этом на информационных входах третьего счетчика 4 определяется номер очередной контролируемой группы . (старшие разряды номера контролируемого элемента), а на информационных выходах четвертого счетчика 5 — номер очередного элемента в группе нала с тактового входа 17 на вход сдвига сдвигового регистра 10 на первом цикле контроля.

Первый цикл контроля идентифицируется при помощи элемента ИЛИ-НЕ 7, который выдает на вход второго элемента И 8 единичное значение при ну,левом коде на информационных выходах первого счетчика 2. Это же единичное значение поступает на второй вход разрешения сравнения второго блока

15 сравнения> запрещая работу этого блока.

Таким образом в сдвиговый регистр заносятся элементы информации только в первом цикле контроля, причем записываются элементы той группы, номер которой определяется кодом на информационных выходах второго счетчика 3.

Второй блок l5 сравнения выполняет функции сравнения только при подаче на его входы элементов информации с одинаковыми номерами, причем через

55 (младшие разряды номера контролируемого элемента), Количество циклов контроля каждой группы определяется разрядностью первого счетчика 2, на

5 счетный вход которого через первый элемент И 1 поступают сигналы g, начала очередного цикла контроля. На информационных выходах первого счетчика 2 определяется номер текущего цикла контроля. После завершения всех циклов контроля одной группы с приходом очередного сигнала о4 на выходе переноса первого счетчика 2 вырабатывается сигнал, увеличивающий на единицу код на информационных выходах второго счетчика 3. Этот код указывает на номер проверяемой группы. Разрядность второго счетчика 3 равна разрядности третьего счетчика

4, что обеспечивает воэможность появления на выходах второго счетчика 3 последовательно номеров всех групп.

Коды с информационных выходов второго 3 и третьего 4 счетчиков поступают на входы первого блока 6 сравнения, который при поразрядном совпадении (и только в этом случае) вырабатывает на выходе равенства сравниваемых кодов единичное значение.

Последнее поступает на первый вход разрешения сравнения второго блока

15 сравнения, разрешая работу этого .блока, и на вход второго элемента

И 8, разрешая прохождение синхросиг- .

1277117 коммутатор 13 под воздействием управляющего кода, поступающего с информационного выхода четвертого счетчика

5, поочередно поступают с выходов сдвигового регистра 10 элементы груп- 5 пы, записанные в него в первом цикле контроля. Второй блок 15 сравнения вывыполняет поразрядное сравнение значений элементов и при их полном совпадении (и только в этом случае) вы- г0 рабатывает нулевой код, который идентифицируется при помощи элемента ИЛИ

11. При несовпадении значений элементов информации вырабатывается на выходе элемента ИЛИ 11 единичное значе" 15 ние, устанавливающее триггер 14 в состояние, запрещающее прохождение сигналов через первый элемент И 1.

Одновременно сигнал с выхода триггера, являющегося выходом 20 сбоя конт- 20 ролируемой информации, останавливает подачу импульсов и информации с контролируемого объекта соответственно на тактовый вход 17 контролируемого элемента и контролируемый информационный вход 19, а также свидетельствует о наличии неустойчивого сбоя в контролируемой информации.

Код с выхода первого блока 15 сравнения записывается в регистр 9, З0 с выхода которого поступает на второй вход блока 12 индикации. На первый и третий входы блока 12 индикации поступают коды с выхода соответственно второго 3 и четвертого счетчиков, 5. При этом блок 12 индикации показывает номера разрядов элемента-и номер самого элемента информации, по которому зафиксирован неустойчивый сбой. 40

Формула изобретения

Устройство для фиксации неустойчивых сбоев, содержащее два элемента И,45 два регистра, первый, второй и третий счетчики, элемент ИЛИ-НЕ, первый и второй блоки сравнения, блок индикации, элемент ИЛИ и триггер, причем вход запуска цикла контроля устройст- 50 ва подключен к первому входу первого элемента И, второй вход которого соединен с инверсным выходом триггера, а выход элемента И соединен Со счетным входом первого счетчика, информа-55 ционные выходы и выход переполнения первого счетчика соединены соответственно с входами элемента ИЛИ-НЕ и

) счетным входом второго счетчика, информационный выход второго счетчика соединен с первым информационным входом первого блока сравнения и первым входом блока индикации, информационный выход третьего счетчика соединен с вторым информационным входом первого блока сравнения, выход равенства которого соединен с первым разрешающим входом второго блока сравнения и с первым входом второго элемента

И, вход контролируемой информационной последовательности устройства подключен к информационному входу первого регистра и к первому информационному входу второго блока сравнения, выход второго блока сравнения соединен с информационным входом второго регистра и входом элемента ИЛИ, выход которого соединен с S-гходом триггера, инверсный выход которого является выходом фиксации сбоя устройства, выход второго регистра соединен с вторым входом блока индикации, вход начальной установки устройства соединен с установочными входами первого, второго и третьего счетчиков, с установочным входом второго регистра и с R-входом триггера, выход элемента ИЛИ-НЕ соединен с вторым входом второго элемента И, выход которого соединен с входом сдвига первого регистра, о т л и— ч а ю щ е е с я тем, что, с целью повышения достоверности фиксации неустойчивых сбоев путем одновременной проверки большего числа тактов в каждом цикле, устройство содержит четвертый счетчик и коммутатор, причем тактовый вход устройства подключен к третьему входу второго элемента И и к счетному входу четвертого счетчика, установочный вход которого соединен с входом начальной установки устройства, информационный выход четвертого счетчика соединен с управляющим входом коммутатора и с третьим входом блока индикации, а выход переполнения четвертого счетчика соединен со счетным входом третьего счетчика, группа информационных выходов первого регистра соединена с группой информационных входов коммутатора, выход которого соединен с вторым информационным входом второго блока сравнения, второй разрешающий вход второго блока сравнения соединен с выходом элемента ИЛИ-НЕ.

1277117

Составитель Д. Ванюхин

Техред И.Попович Корректор И. Эрдейи

Редактор Е. Копча

Закан 6668/43 Тираж 671 Подписное

ВНИИЛИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4