Устройство для сопряжения электронно-вычислительной машины с абонентом

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники, в частности к устройствам для сопряжения источника и приемника информации, и может быть использовано в качестве устройства буферной памяти. Основной задачей изобретения является повышение достоверности передачи информации за счет устранения наложения сигналов обращения к устройству от ЭВМ и абонента . Устройство содержит блок памяти , синхронизатор, реверсивный счетчик , триггер, счетчик записи, счетчик считывания, два элемента задержки , две группы элементов И, группу элементов ИЛИ, элемент ИЛИ. 1 ил.

СОЮЗ СОВЕТСНИХ

Си

РЕСПУБЛИН,SU„„

А1 (д) 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬГПФ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ (21) 3890480/24-24 (22) 24.04.85 (46) 15.12.86. Бюл. М 46 (72) С.С.Игнатьев, В.А.Ионова, В.А.Бураков и E.M.Крылова (53) 681.325(088.8) (56) 1. Авторское свидетельство СССР

У 752321, кл . G 06 F 3/04, 1979, 2. Авторское свидетельство СССР

В 1019428, кл. G 06 F 3/04, 1983 (прототип). (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭЛЕКТРОННО-ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С АБОНЕНТОИ (57) Изобретение относится к области вычислительной техники, в частности к устройствам для сопряжения источника и приемника информации, и может быть использовано в качестве устройства буферной памяти. Основной задачей изобретения является повьппение достоверности передачи информации за счет устранения наложения сигналов обращения к устройству от ЭВМ и абонента. Устройство содержит блок памяти, синхронизатор, реверсивный счетчик, триггер, счетчик записи, счетчик считывания, два элемента задержки, две группы элементов И, группу элементов ИЛИ, элемент ИЛИ. 1 ил.

1277124

Изобретение относится к вычислительной технике, в частности к уст— райствам для сопряжения источника и приемника информации, и может быть использовано в качестве устройства буферной памяти.

Целью изобретения является повышение достоверности передачи информации за счет устранения наложения сигналов обращения к устройству от 38M и абонента.

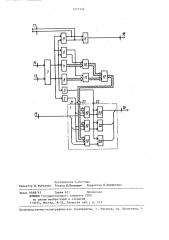

На чертеже представлена блок-схе— ма устройства для сопряжения ЭВМ с абонентом.

Устройство содержит блок 1 памя15 ти, первый 2 и второй 3 элементы задержки, счетчик 4 чтения, реверсивный счетчик 5, триггер 6 синхронизатор 7, счетчик 8 записи, элемент

ИЛИ 9, первую группу элементов И

10, вторую группу элементов И 11, группу элементов ИЛИ 12, первый 13 и второй 14 управляющие входы устройства, информационные входы 15 и выходы 16 устройства, контрольные выходы 17 и выход 18 разрешения устройства, элементы памяти 19, группы элементов И 20, первый 21 и второй

22 управляющие и.адресный 23 вхоцы

30 блока памяти.

Устройство работает следующим образом.

В исходном состоянии синхронизатор 7, с етчик 4 чтения, реверсивный счетчик 5 и счетчик 8 записи обну- 35 лены, триггер 6 находится в произ— вольном состоянии, на адресном входе

23 блока 1 памяти находится нулевой потенциал, на выходе 18 разрешения запрещающий потенциал, блокируюший 40 выдачу от абонента управляющих сигналов считывания по входу 14 устройства, на контрольном выходе 17 устройства — нулевой код, т,е. вся память свободна и ЭВМ может произво- 45 дить запись информации в блок памяти.

При появлении на входе 15 информацианнога слова параллельным кодсм на вход 13 приходит сигнал, который 50 записывает единицу в счетчик 8 и ре- версивный счетчик 5, устанавливает триггер 6 в нулевое состояние и через элемент 2 задержки разрешает запись информационного слова в блок 55

1 памяти по первому адресу.

Кад адреса по которому праисхо дит запись, подается на вход 23 блака 1 памяти с выхода счетчика 8 через элементы И 11, открьггые потенциалом с выхода триггера 6, и элементы

ИЛИ 12.

С выхода 18 разрешения снимается запрещающий потенциал, и абоненту разрешается обращаться в блок 1 памяти за информацией, выдавая сигналы считывания по входу 14 устройства.

При поступлении следующего информационного слова на вход 15 и сигнала на вход 13 в реверсивный счетчик

5 и счетчик 8 записывается еще по единице и на адресном входе 23 блока 1 памяти выставляется соответствующий адрес, по которому записывается код с входа 15 °

Аналогичным образом происходит дальнейшее заполнение элементов 19 блока 1 памяти.

Если на вход приходит сигнал считывания до того, как произойдет заполнение блока 1 памяти, счетчика

8 и реверсивного счетчика 5 импульсами, управляющими записью, триггер

6 устанавливается в единичное состояние, из содержимого реверсивного счетчика 5 вычитается единица, в счетчик 4 записывается единица и выходной сигнал с элемента 3 задержки разрешает считывание информации, причем кад адреса, по которому происходит считывание, подается с выхода счетчика 4 через элементы И 10, открытые потенциалом с выхода триггера 6, и элементы ИЛИ 12.

Значение информации, записанной по этому адресу, считывается и через открьггые элементы И 20 выдается на выход 16 устройства.

При поступлении следующего считывающего сигнала из содержимого реверсивного счетчика 5 вычитается еще одна единица, в счетчик 4 добавляется единица и на входе 23 блока 1 памяти выставляется код второго адреса. Зна4 чение информации, записанной по этому адресу, считывается и через открытые элементы И 20 выдается на выход

16.

При завершении считывания всех записанных кодов в памяти реверсивный счетчик 5 устанавливается в нулевое состояние, вследствие чего элемент

ИЛИ 9 формирует запрещающий потенциал на выходе 18 разрешения, по которому абонент блокирует выдачу управляющих сигналов по входу 14 считы!

277124 вания. После записи хотя бы одного слова элемент ИЛИ 9 снимает запрещающий потенциал с выхода 18 устройства и разрешается дальнейшее считывание.

В случае, когда реверсивный счет— чик 5 заполняется импульсами записи, поступающими по входу 13, на контрольном выходе 17 устройства появляется код, свидетельствующий о заполнении всего блока 1 памяти, и 3ВМ 1О блокирует выдачу информационных слов и управляющих сигналов соответственно по входам 15 и 13. Первый сигнал, поступивший на вход 14, производит считывание информации по одному из 15 адресов блока 1 памяти, запрещающий код снимается с выхода 17 устройства и разрешается дальнейшая запись информационных слов в блок памяти, Синхронизатор 7 синхронизируют сиг90 налы записи и считывания: при одновременном их поступлении на входы синхронизатора на выходах они. разнесены по времени.

Таким образом, устройство осуще- 25 ствляет прием и выдачу информации без искажений и в порядке ее поступления на вход как в условиях, строго согласованных по количеству и порядку следования управляющих сигналов ЗО записи и считывания, так и в условиях, когда на вход управляющих сигналов считывания поступает последовательность импульсов с постоянной частотой, а информация с сопровождаю-35 щими ее сигналами записи может появляться на входах устройства произвольно и объем информации-может быть р азл ич ным.

Устройство позволяет ЭВМ, сокра- 4п щая цикл работу программ, вести оперативный контроль над количеством занятых ячеек блока памяти, предотвращая его переполнение, появление ложной информации на выходе устройства и потерю информации, а введение обратной связи с абонентом исключает возможность приема абонентом недостоверной информации и позволяет ! перераспределить рабочий цикл або,нента сокращая время на ожидание обi

Э мена.

Кроме того, введение синхронизатора позволяет устройству работать при любых соотношениях частот записи и счить>вания.

Ф о р м у л а и з о 6 р е т е н и я

Устройство для сопряжения электронно-вычислительной машины с абонентом, содержащее блок памяти, реверсивный счетчик, триггер, счетчик чтения, счетчик записи, два элемента задержки, две группы элементов И, группу элементов ИЛИ, причем группа выходов реверсивного счетчика подключена к группе информационных входов ЭВМ, группа информационных входов блока памяти подключена к группе информационных выходов ЭВМ, группа информационных выходов блока памяти подключена к группе информационных входов абонента, при этом выходы первого и второго элементов задержки соединены с входами записи и считывания блока памяти соответственно, группа адресных входов которого соединена с группой выходов элементов ИЛИ группы, группы первых и вторых входов которых соединены с группами выходов элементов И первой и второй групп соответственно, нулевой и единичный выходы триггера соединены с первыми входами элементов И второй и первой групп соответственно, группы выходов счетчиков чтения и записи соединены с группами вторых входов элементов

И первой и второй групп соответственно, о т л и ч а ю щ е е с я тем, что, с целью повышения достоверности передачи информации за счет устранения наложения сигналов обращения к устройству от ЭВМ и абонента, в него введены синхронизатор и элемент

ИЛИ, причем первый и второй тактовые входы синхронизатора подключены к выходу записи ЭВМ и выходу считывания абонента соответственно, выход элемента ИЛИ подключен к входу разрешения абонента, при этом группа входов элемента ИЛИ соединена с группой выходов реверсивного счетчика, вход увеличения счета которого соединен с единичным входом триггера, счетным входом счетчика записи, входом первого элемента задержки и с первым тактовым выходом синхронизатора, второй тактовый выход которого соединен с входом второго элемента задержки, счетным входом счетчика чтения, нулевым входом триггера и входом уменьшения счета реверсивного счетчика.

1277124

Составитель С.Пестмал

Редактор И,Рыбченко Техред И.Попович Корректор Л.Пилипенко, Заказ 666S/43 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

11303S, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4