Ттл-элемент

Иллюстрации

Показать всеРеферат

Изобретение относится к импульсной технике и может быть использовано в ТТЛ-интегральных микросхемах. Цель изобретения - повышение помехоустойчивости и быстродействия устройства. Для достижения поставленной целив устройстве введен дополнительньй транзистор 16, коллектор которогосоединен с шиной 6 питания, база подключена к точке соединения первого и второго резисторов 4,5, а эмиттер - к второму выводу пятого резистора 15, Кроме того, устройство содержит транзисторы 1,7,13,14,20, резисторы 8, 10,18,19, входы 2,3, выход 12, диод 11. Техническими преимуществами предложенного устройства являются получение уровня помехоустойчивости, соответствующего типовым значениям ТТЛ- элементов, и более высокое быстродействие по времени задержки выключения схемы. 1 ил. с (Л Ь9 СО 00 ю

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (,5ц 4 Н 03 К 19/088

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н ABTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3935791/24-21 (22) 30.07.85 (46) 15.12.86. Бюл. У 46 (72) Д.К. Сургуладзе, В.П. Акопов и Н.И. Кахишвили (53) 621.374(088.8) (56) Букреев И.П. и др. Микроэлектронные схемы цифровых устройств, М.:

Советское радио, 197$, с.27, рис . 1. 17.

Авторское свидетельство СССР

Р 314307, кл. Н 03 К 19/088, 1970. (54) ТТЛ-ЭЛЕМЕНТ (57) Изобретение относится к импульсной технике и может быть использовано в ТТЛ-интегральных микросхемах. Цель изобретения — повышение помехоустойчивости и быстродействия устройства.

„„Я0„„1277382 A 1

Для достижения поставленной цели в устройстве введен дополнительный транзистор 16 коллектор которого соединен с шиной 6 питания, база подключена к точке соединения первого и второго резисторов 4,5, а эмиттер— к второму выводу пятого резистора 15.

Кроме того, устройство содержит транзисторы f 7, 13 14,20, резисторы 8, 10, 18, 19, входы 2,3, выход 12, диод

11. Техническими преимуществами предложенного устройства являются получение уровня помехоустойчивости, соответствуюцего типовым значениям ТТЛэлементов, и более выСожое быстродействие по времени задержки выключения схемы. 1 ил.

1277382

Изобретение относится к импульсной технике, и в частности, может быть использовано в ТТЛ-интегральных микросхемах.

Цель изобретения — повышение поме- 5 хоустойчивости и быстродействия ТТЛэлемента.

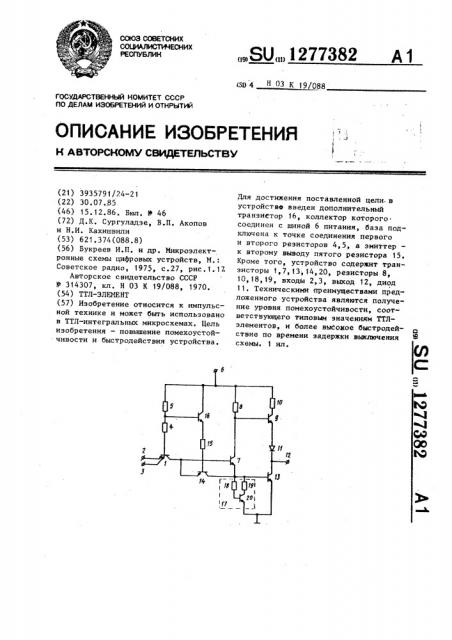

На чертеже приведена принпипиальная электрическая схема ТТЛ-элемента.

ТТЛ-элемент содержит входной многоэмиттерный транзистор 1, эмиттеры которого соединены с входами 2 и 3, база через первый и второй последовательно включенные резисторы 4 и 5 подключена к шине 6 питания, а коллектор подключен к базе фазоинвертирующего транзистора 7, коллектор которого через третий резистор 8 соединен с шиной 6 питания и подключен к базе первого выходного транзистора

9, коллектор которого через четвертый резистор 10 соединен с шиной 6 питания, а эмиттер через диод 11 подключен к выходу 12 и коллектору второго выходного транзистора 13, эмиттер которого соединен с общей шиной, а база подключена к эмиттеру транзистора 7 и коллектору токоответвляющего транзистора 14, эмиттер которого соединен с коллектором транзистора 1, а ЗО база через пятый резистор 15 — с эмиттером дополнительного транзистора

16, коллектор которого соединен с шиной 6 питания, а база подключена к точке соединения резисторов 4 и 5, база транзистора 13 через рассасынаю— щую цепь 17 на двух резисторах 18 и

19 и рассасывающем транзисторе 20 соединена с общей шиной.

ТТЛ-элемент работает следующим об- 40 разом.

При наличии на обоих входах 2 и

3 высокого уровня напряжения логической "1" многоэмиттерный транзистор

1 работает в активном инверсном режи- 45 ме, при котором ток, протекающий от шины 6 питания через резисторы 4 и

5 и открытый коллекторный переход многоэмиттерного транзистора 1, втекает в базу транзистора 7, обеспечи- gp вая его насыщенное состояние. Часть этого тока ответвляется в базу транзистора 16, эмиттерный ток которого, ограниченный резистором 15, через открытый коллекторный переход тран- у зистора 14 вместе с эмиттерным током транзистора 7 втекает в базовую цепь транзистора 13. При этом послецний находится в режиме насыщения, транзистор 9 благодаря наличию низкого потенциала на коллекторе насыщенного транзистора 7, выключен, и на выходе

12 ТТЛ-элемента поддерживается низкий уровень напряжения логического

"0". Номиналы резисторов 4 и 5 подобраны таким образом, что с учетом прямого падения напряжения на базоэмиттерном переходе дополнительного транзистора 16 схема инвертора имеет типовую для ТТЛ-схем передаточную характеристику, что обеспечивает соответствующую помехозащищенность, При подаче хотя бы на один из входов 2 или 3 низкого уровня напряжения логического 0 соответствующий змиттерний переход многоэмиттерного транзистора 1 открывается, потенциал его базы понижается и транзистор 1 из активного инверсного режима переходит в режим насыщения, При этом в связи с понижением потенциала базы транзистора 1 дополнительный транзистор

16 выключается, а токоответвляющий транзистор 14, в базе которого в исходном режиме накоплен значительный заряд неосновных носителей, из активного инверсного режима переходит в .режим насыщения. Таким образом, в момент подачи на одну из входных шин схемы низкого уровня напряжения логического "0" между ней и базой насыщенного транзистора 13 параллельно с активной рассасывающей цепью 17 неосновных носителей, состоящей из резисторов 18 и 19 и транзистора 20, образуется дополнительная низкоомная токоотводящая цепь из последовательно включенных транзисторов 1 и 14, что значительно ускоряет выключение транзистора 13 и устройства в целом.

Насьпценный транзистор 7, как в известной схеме быстро выключается благодаря значительному току, вытекающему к входам 2 и 3 через насьпценный транзистор 1, Формула изобретения

ТТЛ-элемент, содержащий входной многозмиттерный транзистор, эмиттеры которого соединены с входами, база через первый и второй последовательно включенные резисторы соединена с ши-, ной питания, а коллектор подключен к базе фазоинвертирующего транзистора, коллектор которого через третий ре1277382

Составитель А. Янов

Редактор M. Петрова Техред H.Ïîïîâè÷ Корректор M.Ûàðoøè

Заказ 6759/56 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул..Проектная, 4 зистор соединен с шиной питания и подключен к базе первого выходного транзистора, коллектор которого через четвертый резистор соединен с шиной питания, а эмиттер через диод подклю- чен к выходу и коллектору второго выходного транзистора, эмиттер которого соединен с общей шиной и через рассасывающую цепь с его базой, база токоответвляющего транзистора соединена10 с первым выводом пятого резистора, эмиттер — с коллектором входного многоэмиттерного транзистора, а коллектор подключен к эмиттеру фазоинвертирующего транзистора и базе второго выходного транзистора, о т л и ч аю шийся тем, что, с целью повышения помехоустойчивости и быстродействия, в него введен дополнительный транзистор, коллектор которого соединен с шиной питания, база подключена к точке соединения первого и второго резисторов, а эмиттер — к второму выводу пятого резистора.