Управляемый делитель частоты

Иллюстрации

Показать всеРеферат

Изобретение может быть использовано в устройствах цифровой и измерительной техники, в устройствах отсчета временных интервалов и устройствах синхронизации цифровых систем. Целью изобретения является уменьшение фазового сдвига между входньми и выходными импульсами при сохранении скважности выходных импульсов, равной двум. С этой целью в устройство введены элементы ИЛИ 9,10,11,12, элементы И-НЕ 7,8, инвертор 18 и элемент 16. Кроме того, устройство содержит счетчик 1 импульсов, шину 2 кода коэффициента деления, формирователь 3 импульсов, триггеры 4 и 5, входную и выходную шины 6,19, элементы И 13,14, шину 15 начальной установки , инвертор 17. При формировании фронтов выходных импульсов осуществляется прямая передача входных импульсов или их инвертирование, а при формировании выходного импульса или паузы осуществляется блокировка выхода на соответствующем уровне после формирования фронта и разблокирование перед очередным фронтом. 2 ил. (Л J9 Ь СО сх ;о

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (gg 4 Н 03 К 23/66

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A ВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3936812/24-21 (22) 01. 08, 85 (46) 15. 12.86. Бюл. Р 46 (71) Львовский ордена Ленина политех— нический институт им. Ленинского комсомола (72) И.П.Паралюх (53) 62 1.374 .3 (088 .8) (56) Авторское свидетельство СССР

Р 1119176, кл. Н 03 К 23/00, 01.06.83 °

Авторское свидетельство СССР

N- 1238234 кл Н 03 К 23/66 27,09.84. (54) УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ (57) Изобретение может быть использовано в устройствах цифровой и измерительной техники, в устройствах отсчета временных интервалов и устройствах синхронизации цифровых систем. Целью изобретения является уменьшение фазового сдвига между входными и выход„„SU„„1277389 A 1 ными импульсами при сохранении скважности выходных импульсов, равной двум. С этой целью в устройство введены элементы ИЛИ 9,10,11,12, элементы И-НЕ 7,8, инвертор 18 и элемент

ИЛИ-НЕ 16. Кроме того, устройство содержит счетчик 1 импульсов, шину 2 кода коэффициента деления, формирователь 3 импульсов, триггеры 4 и 5, входную и выходную шины 6,19, элементы И 13, 14, шину 15 начальной установки, инвертор 17. При формировании фронтов выходных импульсов осуществляется прямая передача входных импульсов или их инвертирование, а при формировании выходного импульса или паузы осуществляется блокировка выхода на соответствующем уровне после формирования фронта и разблокирование перед очередным фронтом. 2 ил.

1277389

Изобретение относится к импульсной технике и может быть использовано в устройствах цифровой и измерительной техники, в устройствах отсчета временных интервалов и устройствах синхронизации цифровых систем.

Цель изобретения — уменьшение фазового сцвига между входными и выходными импульсами при сохранении скважности выходных импульсов, равной

1О двум.

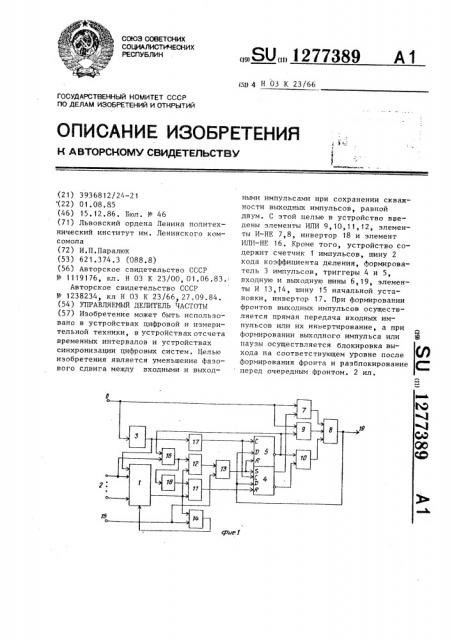

На фиг.1 представлена электрическая функциональная схема устройства; на фиг.2 — временная диаграмма, поясняющая работу устройства.

Управляемый делитель частоты содержит (вычитающий двоичный) счетчик

1 импульсов, шину 2 кода коэффициента деления, формирователь 3 импульсов, первый и второй триггеры 4 и

5, входную шину 6, первый и второй элементы И-НЕ 7 и 8, первый, второй, третий и четвертый элементы ИЛИ 9, 10, 11 и 12, первый и второй элементы

И 13 и 14, шину 15 начальной установ- 25 ки, элемент ИЛИ-НЕ 16, первый и второй инверторы 17 и 18 и выходную шину

19. Информационные входы счетчика 1 импульсов соединены с шиной 2 кода коэффициента деления, тактовый вход- 30 через первый инвертор 17 с С-входами первого и второго триггеров 4 и 5, а через формирователь 3 импульсов с входной шиной 6 и с первыми входами первых элементов И-НЕ 7 и ИЛИ 9, выходы которых соединены соответственно с первым и вторым входами второго элемента И-НЕ 8, выход которого соединен с выходной шиной 19 и с D-входами первого и второго триггеров 4 и 5, à 4П третий вход — с выходом второго элемента ИЛИ 10, первый вход которого соединен с инверсным выходом первого триггера 4, прямой выход которого соединен с вторым входом первого эле- 4g мента И-НЕ 7, R-вход — с выходом третьего элемента ИЛИ 11, à S-вход — с

R-входом второго триггера 5 и с выходом первого элемента И 13 первый вход которого соединен с первым входом второго элемента И 14, выход которого соединен с входом предварительной установки счетчика 1 импульсов, и с шиной 15 начальной установки, а второй вход — с выходом четвертого элемента ИЛИ 12, инверсный выход второго триггера 5 соединен с вторыми входами первого и второго элементов

ИЛИ 9 и 10 и первым входом элемента

ИЛИ-НЕ 16, второй вход которого соединен с младшим разрядом шины 2 кода коэффициента деления, а выход — спервым входом четвертого элемента ИЛИ 12 и через второй инвертор 18 с первым входом третьего элемента ИЛИ 11. Вторые входы третьего и четвертого элементов ИЛИ 11 и 12 и второго элемента

И 14 соединены с выходом "Заем" счетчика 1 импульсов.

Формирователь 3 импульсов может быть выполнен в виде элемента ИСКЛЮЧАЮЦЕЕ ИЛИ, первый вход которого непосредственно,, а второй через элемент задержки соединены с его входом.

Управляемый делитель частоты работает следующим образом.

В исходное состояние устройство приводится подачей логического нуля на шину 15 начальной установки, при этом по S-входу в единичное состояние устанавливается триггер 4, по R-входу в нулевое состояние устанавливается триггер 5, а по входу предварительной установки в счетчик 1 с шины 2 записивается двоичный код N коэффициента деления частоты, По шине 6 на вход формирователя

3 поступают импульсы входной частоты (фиг.?с ), на выходе которого формируются короткие положительные импульсы по каждому фронту входного импульса (фиг.? 8), т.е. импульсы удвоенной входной частоты.

Посла начальной установки инверсный выход триггера 5 (фиг.2 6) и прямой выход триггера 4 (фиг.?.z.) находятся в состоянии единиц и обеспечивают режим прямой передачи входных импульсов на шину 19 поскольку элементы 9 и 10 блокированы на уровне единиц и не влияют на работу элемента 8, а элемент 7 открыт по второму входу.

Поэтому с приходом первого входного импульса (фиг.2a) через последовательно соединенные элементы 7 и 8 на шине

19 формируется положительный фронт (фиг.2 е), а с помощью формирователя.

3 - короткий положительный импульс (фиг.28), который уменьшает на единицу содержимое счетчика 1 импульсов (фиг.2 ), а своим задним фронтом через инвертор 17 устанавливает в единичное состояние триггеры 4 и 5, поскольку на их D-входах к этому моменту уже установится единица, поступающая с шины 19 (длительность импульсов

3 1277 формирователя 3 выбирается такой, чтобы вместе с задержкой инвертора 17 перекрывать время задержки любой пары элементов: 7 и 8 или 9 и 8).

Установка триггера 5 в единичное состояние вызывает логический ноль на инверсном выходе (фиг,2 6), а слечовательно, и ноль на выходе элемента

10, что приводит к блокировке выхода элемента 8 и шины 19 устройства на t0 уровне логической единицы.

Последующие входные импульсы не изменяют сигнал на шину 19, а импульсы с выхода формирователя 3 изменяют лишь содержимое счетчика 1 (Фиг.2 )1 15 осуществляя подсчет полупериодов. С приходом на шину 6 (N+1)/2-ro импульса при нечетном N или по окончании

N / 2-ro импульса при четном N на выходе Формирователя 3 формируется N-й импульс, который уменьшает содержимое счетчика 1 до нулевого значения (фиг.2 y), а по его окончании на выходе "Заем" счетчика 1 выбирается нулевой уровень (фиг.2д), который через 25 элемент 14 поступает на вход предварительной установки счетчика 1 и записывает в него вновь код И коэффици,ента деления (фиг.2 p), после чего логический ноль на выходе "3aeM" ис- gp чезает (фиг.?B?. Однако еще до этого в зависимости от четности коэффициента N деления и состояния триггера

5 производится переключение триггера 4 или 5 (с целью устранения возll ев

35 можности возникновения гонок пере.— ключение производится всегда только одного из триггеров). При нечетном

N младший разряд коэффициента деления на шине 2 находится в единице, кото- 4О рая удерживает на выходе элемента 16 ноль, открывая тем самым элемент 12 и закрывая через инвертор 18 элемент

11 для пропуска уровня логического нуля. Поэтому ноль с выхода "Заем" счетчика 1 через элементы 12 и 13 поступает на К- и $-входы триггеров

4 и 5 (пытаясь установить их прямой и инверсный входы соответственно в единицу). Поскольку к этому моменту поочередно один из указанных выходов находится в единице, то и происходит поочередная установка в единицу первого и подтверждение этого состояния второго из указанных выходов триггеров (и, наоборот, при следующем импульсе (фиг.2Ь,z) при нечетном N).

Такая установка снова переводит

389 4 устройство в режим прямой передачи входных импульсов. Поэтому после окончания импульсов или паузы (фиг.2a) на выходе формируется задний или передний фронт выходного импульса (фиг,2 е) соответственно.

По ле формирования заднего фронта выходного импульса (фиг.2 е) логический ноль с шины 19 поступает на Рвходы триггеров 4 и 5, и первый импульс с выхода формирователя 3 устанавливает в ноль триггер 4 прй нечетном N (или подтверждает это состояние при четном N) (фиг.2z), что вызывает логическую единицу на выходе элемента 7, а триггер 5 этим импульсом с выхода формирователя 3 устанавливается в логический ноль при четном N или подтверждается в этом сос1 тоянии при нечетном N. Единица с инверсного выхода триггера 5 через элементы 9 и 10 поступает на второй и третий входы элемента 8, которые вместе с единицей с выхода элемента

7 удерживает на выходе элемента 8 логический ноль. Последующие входные импульсы вновь не изменяют состояния выхода, а только уменьшают содержимое счетчика 1, и идет формирование паузы между импульсами.

При четном N младший разряд на шине 2 коэффициента деления находится в логическом нуле, который открывает элемент 16, единица с выхода которого при логическом нуле на инверсном выходе триггера 5 закрывает элемент

12, а через инвертор 18 открывает элемент 11. Поэтому ноль с выхода

"Заем" счетчика 1 по окончании N/2ro входного импульса через элемент

11 по R âõîäó устанавливает триггер

4 в логический ноль, который вместе с единицей с инверсного выхода устанавливают логические единицы на выходах элементов 7 и 10 соответственно, а оставшийся логический ноль на инверсном выходе триггера 5 разрешает элементу 9 пропуск входных импульсов, которые инвертируются элементом 8.

По окончании N/2-го периода поступивший на шину 6 (N/2+1) импульс инвертируется, формируя на выходе задний фронт выходного импульса (фиг.2 е).

Если инверсный выход триггера 5 находится в логической единице, то она через элемент 16 открывает элемент 12, через который ноль с выхода

"Заем" счетчика 1 по окончании N-ro

5 12773 входного импульса поступает на элемент 13 и устанавливает в единичное состояние по S-входу триггер 4, а по R-входу подтверждает логическую единицу на инверсном выходе триггера

5. T,е устройство возвращается в исходное состояние, при котором идет прямая передача импульсов с шины 6 на шину 19, поэтому по окончании Nго периода входных импульсов с при- ip ходом (N+1)-го импульса будет сформирован передний фронт нового выходного импульса.

В итоге на шину 19 поступают импульсы, частота следования которых равна частоте импульсов, поступающих на шину 6, деленной на коэффициент деления N, поданный на шину 2. Причем как при четном значении N выход- 2О ные импульсы имеют всегда скважность, равную двум, так и при нечетном значении N. Если при нечетном N входные импульсы поступают со скважностью, не равной двум, то длительность вы- 25 ходного импульса отличается от длительности паузы между. импульсами на время, равное аналогичной разности во входных импульсах.

Формула из обретения

Управляемый делитель частоты, содержащий счетчик импульсов,информационные входы которого соединены с шиной кода коэффициента деления, тактовый вход — черезформирователь импульсов с входной шиной, а через первый инвертор с С-входом первого триггера, S-вход которого соединен с выходом 40 первого элемента И, первый вход которого соединен с шиной начальной уста89 новки и с первым входом второго элемента И, выход которого соединен с входом предварительной установки счетчика импульсов, второй триггер и выходную шину, отличающийся тем, что, с целью уменьшения фазового сдвига между входными и выходными импульсами при сохранении скважности выходных импульсов, равной двум, в него введены четыре элемента ИЛИ, два элемента И-НЕ, второй инвертор и элемент ИЛИ-НЕ, причем входная шина соединена с первыми входами первых элементов И-НЕ и ИЛИ, выходы которых соединены соответственно с первыми вторым входами второго элемента И-НЕ, выход которого соединен с выходной шиной и с D-входами первого и второго триггеров,. а третий вход соединен с выходом второго элемента ИЛИ, первый вход которого соединен с инверсным выходом первого триггера, прямой выход которого соединен с вторым входом первого элемента И-НЕ, R-вход — с выходом третьего элемента ИЛИ, а С-вход и S-вход соединены соответственно с

С-входом и R-входом второго триггера, инверсный выход которого соединен с вторыми входами первого и второго элементов ИЛИ и первым входом элемента

ИЛИ-НЕ, второй вход которого соединен с младшим разрядом шины кода коэффициента деления, а выход — с первым входом четвертого элемента ИЛИ и через второй инвертор с первым входом третьего элемента ИЛИ, выход четвертого элемента ИЛИ соединен с вторым входом первого элемента И, при этом вторые входы третьего и четвертого элементов ИЛИ и второго элемента И соединены с выходом "Заем счетчика импульсов.

1277389

1 ь

4

@а я 2

Составитель А.Соколов

Техред И.Попович Корректор M.Ñàìáîðñêàÿ

Редактор M,Ïåòðoâà

Заказ 6759/56 Тираж 816 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r., Ужгород, ул. Проектная, 4