Устройство преобразования синусных сигналов в код

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике, в частйости к аналого-цифровым преоб разователям, обеспечивающим связь цифровых вычислительных машин с устройствами , вьщающими информацию в аналоговой форме. Целью изобретения является расширение динамического диапазона и расширение функциональных возможностей устройства.. Для этого в устройство преобразования синусных сигналов в код, содержащее селектор рктантов, блок преобразования напрярсения в код, инвертор и суммирующий усилитель, введены два квадратора, источник опорных напряжений и делитель напряжений. Поставленная цель достигается за счет разложения функции suiet/o6 в ряд Тейлора, которое используется для выделения сигнала в аналоговой форме и обеспечивает расширение динамического диапазона. 2 ип. г (Л

(19I (11) (59 4 Н 03 М 1/5.8

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3894846/24-24 (22) 11.05.85 (46) 15.12.86. Бюл. Ф 46 (72) А.Н. Гуляев, И.Г. Дорух и П.К. Ермоленко (53) 681.325 (088.8) (56) Авторское свидетельство СССР

У 283701, кл. G 01 В 7/30, 1967.

Авторское свидетельство СССР

У 1104567, кл. G 01 В 7/30, G 08 С 9/04, 1983. (54) УСТРОЙСТВО ПРЕОБРАЗОВАНИЯ СИНУСНЫХ СИГНАЛОВ В КОД (57} Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровым преоб разователям, обеспечивающим связь цифровых вычислительных машин с устройствами, выдающими информацию в аналоговой форме. Целью изобретения является расширение динамического диапазона и расширение функциональных возможностей устройства. Для этого в устройство преобразования синусных сигналов в код, содержащее селектор рктантов, блок преобразования напрякения в код, инвертор и суммирующий усилитель, введены два квадратора, источник опорных напряжений и делитель напряжений. Поставленная цель достигается за счет разложения функ- ции зъп(/о(, в ряд Тейлора, которое используется для выделения сигнала в аналоговой форме и обеспечивает расширение динамического диапазона.

2 ил.

77399 без большой погрешности можно запи20

U (1) Сигнал Х на выходе делителя 3 образуется путем деления и последующего инвертирования сигнала Singа на

его первом входе на сигнал g на его втором входе входе делимого, поступающий с выхода усилителя 8 Sin@

ЗО

Х

Устройство работает следующим образом.

Селектор 1 формирует .сигнал,, пропорциональный синусу угла 0(в пределах первого октанта, который посту- . пает на измерительный вход блока 2 и на вход (вход делимого} делителя 3. 35

На опорный вход блока 2 с выхода усилителя 8 поступает сигнал, амплитуда которого с высокой точностью

si.пс4 пропорциональна величине — — — . По 40

OC этому выходной код блока 2 получается пропорциональным углу К в пределах первого октанта из отношения напряжений, Поступивших íà его измерительный и опорный входы. 45

Рассмотрим процесс формирования сигнала на выходе усилителя 8.

Пусть Х вЂ . сигнал на выходе делителя 3. Тогда сигнал U на выходе квадратора 4, т.е. на первом входе . усилителя 8, определяется З

U — Х

1 делителя 3, а следовательно, и на втором выходе устройства, пропорциональна углу e, 50

Таким образом, устройство обеспечивает получение сигналов, пропорциональных углу поворота oC как в цифровой (на выходе блока 2), так и в аналоговой (на выходе делителя 3) форме, при этом обеспечивается достаточно высокая точность преобразования при изменении угла сб в прео делах 0-90

Изобретение относится к автоматике и вычислительной технике, в частности к аналого-цифровым преобразователям, обеспечивающим связь цифровых вычислительных машин с устройствами, выдающими информацию в аналоговой форме.

Цель изобретения — расширение динамического диапазона и функциональных возможностей устройства.

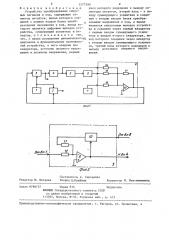

На фиг. 1 приведена структурная схема устройства преобразования синусных сигналов в код; на фиг.2— структурная схема делителя напряжений.

Устройство преобразования синусных сигналов в код содержит селектор 1 октантов, блок 2 преобразования напряжения в код, делитель 3 напряжения, квадраторы 4 и 5, инвертор б, источник 7 опорного напряжения, суммирующий усилитель 8.

Делитель 3 содержит операционный усилитель 9, перемножитель 10 и резисторы 11 и 12, суммирующий усилитель 8 содержит операционный усили- > тель 13 и резисторы 14-17.

Учитывая, что сигнал. U на втором входе усилителя 8 образуется путем возведения в квадрат с помощью квадратора 5 и последующего инвертирования сигнала П,инвертором б, получим г

= -U = -Х .

Источник 7 вырабатывает, сигнал 0 единичного уровня отрицательной полярности, который поступает на третий вход усилителя 8.

Коэффициенты передачи по первому, второму и третьему входам усилителя

8 выбраны равными 1/6, 1/120.и 1 соответственно. С учетом этого выходной сигнал U усилителя 8 определится

1 1 1 г 1

U = —. — U — — — U — U =1- — Х +- — Х.

120 г 5 6 120 о

При Х 90 с учетом разложения функции Sin Х в степенной ряд вида

5 7 2@+ >

Х Х Х Х

SinX "- Х- --+ — — --+... (-1 )

3! 5! 7! (2n+1)!

Эта операция осуществляется за счет установления равенства тока через первый резистор усилителя 9, образуемого сигналом Sim g с выхода селектора 1, току через второй резистор усилителя 9, образуемому сигналом x U с выхода перемножителя 10. С учетом выполнения (1) получим

Б1пК

Х=-cG u

С

Амплитуда сигнала на выходе усилителя 8, а следовательно, и на опорном входе блока 2 пропорциональна

Sin с а амплитуда сигнала на выходе

Составитель А. Сидоренко

Редактор M. Петрова Техред Л.Олейник

KoppeKTop M. Максимишинец

Заказ 6760/57 Тираж 81б

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж вЂ” 35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4

12773 формула изобретения .Устройство преобразования синусных сигналов в код, содержащее селектор октантов, выход которого соединен с первым входом блока преобразования напряжения в код, выход которого является цифровым выходом устройства, суммирующий усилитель и инвертор, о т л и ч а ю щ е е с я тем, что, с целью расширения динамического1О диапазона и функциональных возможностей устройства, в него введены два квадратора, источник опорного напряжения и делитель напряжения, первый

99 4 вход которого подключен к выходу селектора октантов, второй вход — к выходу суммирующего усилителя и соединен с вторым входом блока преобразования напряжения в код а выход является аналоговым выходом устройства и соединен через первый квадратор с первым входом суммирующего. усилителя и входом второго квадратора, выход которого соединен через инвертор с вторым входом суммирующего усилителя, третий вход которого подключен к выходу источника опорного напряжения.