Устройство декодирования тональных сигналов

Иллюстрации

Показать всеРеферат

Изобретение относится к радиосвязи и является дополнительным к изобретению по авт. св. № 1160614. Цель изобретения - повьшение помехоустойчивости . Устройство содержит фильтр 1, компаратор 2, синхрогенератор 3, триггеры 4, 12, 21, блоки оперативной памяти (БОП) 5 и 25, элементы И 6, 17, 22 - 24, счетчики 7, 8, 14, 18, блок 9 постоянной памяти (БПП), блок 10 начальной установки , регистр 11, сумматор 13, делитель 15 частоты, элементы ИЛИ 16 и 24, дешифратор 19 и элемент 20 задержки. Управление работой БОП 5 и 25 осуществляется выходным сигналом делителя 15 частоты: при сигнале 1 они переводятся в режим записи , при сигнале О - в режим считывания информации. Для осуществления записи и считывания на их вторые управляющие входы подается О. Адреса записи и считывания БОП 5 и 25 изменяются одновременно и определяются сигналом сумматора 13. При записи информации в БОП 5 и 25 на выходе БПП 9 будут постоянные сигналы, не зависящие от адресов на его информационных входах. Появление 1 на выходе БОП 5 при считывании свидетельствует о том, что обнаружено совпадение появления импульсов на (О (Л ю со 00 14)

СОЮЗ СОВЕТСНИХ

СОЩ4АЛИСТИЧЕСНИХ

РЕСПУБЛИН

„„SU„„>27743

А2

Н 04 9/ОО

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н А BTOPCKOMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (61) 1160614 (21) 3863440/24-09 (22) 04.03.85 (46) 15.12.86. Бюл. Ф 46 (72) В. Ф. Калиниченко и С, В, Саврасов (53) 621,395.632(088,8) (5á) Авторское свидетельство СССР

Ф 1160614, кл. Н 04 11 9/00, 1983. (54) УСТРОЙСТВО ДЕКОДИРОВАНИЯ ТОНАЛЬНЫХ СИГНАЛОВ (57) Изобретение относится к радиосвязи и является дополнительным к изобретению по авт ° св. В 1160614.

Цель изобретения — повышение помехоустойчивости. Устройство содержит фильтр 1, компаратор 2, синхрогеие- ратор 3, триггеры 4, 12, 21 блоки оперативной памяти (БОП) 5 и 25, элементы И 6, 17, 22 — 24, счетчики 7, 8, 14 18, блок 9 постоянной памяти (БПП), блок 10 начальной установки, регистр 11, сумматор 13, делитель 15 частоты, элементы ИЛИ 16 и 24, дешифратор 19 и элемент 20 задержки, Управление работой BOIL 5 и 25 осуществляется выходным сигналом делителя 15 частоты: при сигнале "1" они переводятся в режим записи, при сигнале "0" — в режим считывания информации, Для осуществления записи и считывания на их вторые управляющие входы подается "О", Адреса записи и считывания БОП 5 и 25 изменяются одновременно и определяются сигналом сумматора 13. При записи информации в БОП 5 и 25 на выходе БПП 9 будут постоянные сигналы, не зависящие от адресов на его ини 1I формационных входах, Появление 1 на выходе БОП 5 при считывании свидетельствует î ТоМ что обнаружено совпадение появления импульсов на

1277433 выходе синхрогенератора 3, разделенных интервалом времени, равным N периодам принимаемой частоты. Окончательное решение о том, что принят

Изобретение относится к радиосвязи и может быть использовано в уст" ройствах для приема тональных сигналов нескольких заданных частот, в частности, для приема данных, пере" даваемых последовательным частотным кодом.

Цель изобретения — повышение помехоустойчивости.

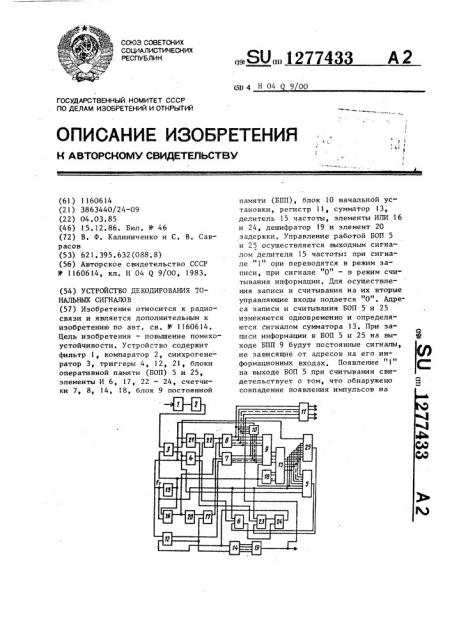

На чертеже представлена структурная схема устройства.

Устройство декодирования тональных сигналов содержит фильтр 1, компаратор 2, синхрогенератор З,,первый триггер 4, первый блок 5 оперативной памяти, первый элемент И 6, первый счетчик 7, второй счетчик 8, блок 9 постоянной памяти, блок 10 начальной установки, регистр 11, второй триггер 12, сумматор 13, третий счетчик

14, делитель 15 частоты, первый элемент ИЛИ 16, второй элемент И 17, четвертый счетчик 18, дешифратор

19, элемент 20 задержки, третий триггер 21, третий элемент И 22, четвер-.ый элемент И 23, второй элемент ИЛИ 24 и второй блок 25 оперативной памяти, Устройство декодирования тональных сигналов работает следуюпщм образом.

В исходном состоянии на вторых выходах первого, второго и третьего триггеров 4, 12, 21 присутствует логическая "1", на выходе третьего элемента И 22 — логическая "1".

Первый, второй и третий счетчики 7, 8, 14 установлены в нулевое состояние. На выходах первого и четвертого элементов И 6 и 23 присутствует

"0". Выходным сигналом делителя 15 частоты управляется работа блоков

5 и 25 оперативной памяти, При логической "1" на выходе делителя 15 первый и второй блоки 5 и 25 операсигнал соответствующей частоты, принимается после проверки отклонения каждого периода сигнала от номинального значения. 1 ил.

2 тивной памяти переводятся в режим записи, при "0" — в режим считывания информации, причем для осуществления записи и считывания необхо5 димо на вторые управляющие входы блоков 5 и 25 оперативной памяти подать логический "0". Адресу записи и считывания блоков 5 и 25 оперативной памяти изменяются одновременно и определяются выходным сигйалом сумматора 13. При записи информации в блоки 5 и 25 оперативной памяти на выходе блока 9 постоянной памяти— постоянные сигналы, не зависящие от адресов на его информационных входах, На выходе синхрогенератора 3 по переднему фронту входного сигнала формируется импульс, передний фронт которого совпадает с передним фронтом выходного сигнала делителя 15 частоты, Выходной импульс синхрогенератора 3 поступает на информационный вход блока 5 оперативной памяти, 25: в результате чего в него записывается "1", Адрес ячейки оперативного блока 5 памяти, в которую записывается информация, определяется суммой выходного кода четвертого счет30 чика 18 и выходного кода блока 9 постоянной памяти, По этому же адресу во второй блок 25 оперативной памяти записывается "0", так как в это время на дополнительном выходе

З5 синхрогенератора 3 будет "0", Одновременно выходным сигналом синхрогенератора 3 первый триггер 4 устанавливается в состояние, при

4О котором на его первом выходе "1", а ,на втором - "0", в результате чего на выходе третьего элемента И 22 появляется "0", разрешающий работу второго счетчика 8 (для перевода первого счетчика 7 в режим счета необходимо на его третий вход подать "1").

При появлении "0" на выходе делителя 15 частоты блоки 5 и 25 оперативной памяти переводятся в режим считывания, к входам сумматора 13 подключается блок 9 постоянной памяти, на выходе которого. будет информация из ячеек памяти, адрес которых задается выходными кодами первого и второго счетчиков 7 и 8, На второй вход третьего счетчика

14 и первый вход второго триггера

12 информация через второй элемент

ИЛИ 24 поступает только из блока 5 оперативной памяти. Это обусловлено тем, что на первом входе четвертого элемента И 23 — логический "0", Независимо от выходной информации второго блока 25 оперативной памяти на выходе четвертого элемента И 23 будет "0".

В блоке 9 постоянной памяти по адресу 00000, задаваемому в исходном состоянии выходными кодами первого и второго счетчиков 7 и 8, записана информация, суммирование которой с выходным кодом четвертого счетчика 1 8 дает адрес блока 5 оперативной памяти, по которому ранее производилась запись информации на время, равное N периодам первого из .!ринимаемых устройством сигналов ,1аданной частоты, Если в тот момент (! сигнала на выходе синхрогенератора

3 не было, по этому адресу в блоке

5 оперативной памяти. записан "0", На выходе первого элемента И 6, второго элемента ИЛИ 24 и второго триггера 12 значение не изменяется, При появлении с выхода второго элемента

И 17 на втором входе второго счетчика 8 логической "1" он перейдет в состояние 0001, изменяя адрес блока

9 постоянной памяти, По данному адресу в блоке 9 постоянной памяти хранятся данные, суммирование которых с кодом четвертого счетчика 18 дает новый адрес считывания для блока 5 оперативной памяти, т.е. устройство декодирования перестраивается на прием второй частоты, Если и по этому адресу в блоке 5 опе" ративной памяти ранее был зайисан логический "О", т,е, и эта частота не обнаружена, то второй счетчик 8 переходит в состояние 0010, что соответствует настройке устройства на

1277433 прием третьей частоты, Если ни одна из частот, на прием которых настроено устройство, не обнаружена, что соответствует установке второго счетчика 8 в определенное состояние, то на выходе блока 10 начальной установки формируется логическая

"1", устанавливающая второй счетчик

8 и первый триггер 4 в исходное со10 стояние, Если же при считывании информации из блока 5 оперативной памяти по одному из адресов на его выходе будет логическая "1", то на выходе первого элемейта И 6, а следовательно, на выходе второго элемента ИЛИ 24, появляется логическая "1". Второй— триггер 12 устанавливается в состояние, при котором на его первом выходе — логическая "1", а на втором выходе — логический "0", запрещающий прохождение через второй элемент И

17 импульсов с выхода элемента ИЛИ

16 на второй вход второго счетчика

8 и разрешающий работу третьего счетчика 14, В результате фиксируется выходной код второго счетчика 8, а так как íà IfppBQM выходе ,второго триггера 12 — логическая

ЗО "!" то,разрешается работа первого. счетчика 7.

Появление логической "1" на выходе блока 5 оперативной памяти

35 свидечельсчвует о том, ччо обнаруже но совпадение (с точностью до периода выходной частоты делителя 15) моментов появления импульсов на выходе синхрогенератора 3, разделенных ин4О тервалом времени, равным N периодам одной из принимаемых устройством частот. Выходной код второго счетчтка

8 является при этом кодом обнаруженной частоты.

Окончательное решение о том, что принят сигнал соответствующей частоты, принимается после проверки отклонения каждого периода сигнала от ьоминального значения, что осуществляется следующим образом, Так как на первом выходе второго триггера 12 устанавливается сигнал логической 1", то по переднему фронту импульса, поступающего с выхода

55 первого элемента ИЛИ 16 на второй вход первого счетчика 7, он будет изменять свое состояние, что вызывает изменение адресов блока 9 постоянной памяти. По этим адресам в

1277433 блоке 9 постоянной памяти записаны данные, суммирование которых с выходным кодом четвертого счетчика 18 дает такие коды на адресных входах блока 5 оперативной памяти, что счи" тывание информации иэ него производится по адресам, которые были в моменты времени, отстоящие от момента последнего появления сигнала на выходе синхрогенератора 3 на время, равное (Ы-1), (N-2)...2,1 периоду сигнала обнаруженной частоты, Если в эти моменты отклонение передних фронтов выходного сигнала компара1 тора .2 не превышает величины, равной периоду выходного сигнала делителя 15, то при считывании из блока оперативной памяти по этим адресам на его выходе будет логическая "1".

Число периодов входного сигнала, для которых отклонение переднего фронта каждого периода не превышает заданного, т,е. число логических

"1" на выходе блока 5 оперативной

2 памяти подсчитывается третьим счетчиком 14 и при достижении им определенного значения на выходе дешифратора 19 формируется импульс, а в регистр 11 записывается код принятой частоты, Если под действием помех отклонение переднего фронта входного сигнала превышает номинальную величину, то приема не происходит. Устройство устанавливается в исходное состояние выходным импульсом блока

10 начальной установки, который формируется при достижении первым 7 или вторым 8 счетчиками определенных состояний вне зависимости от того, был принят сигнал или нет.

ll0

35

По отрицательному фронту входного сигнала на дополнительном выходе синхрогенератора 3 формируется импульс, передний фронт которого сов- 4 падает с передним фронтом выходного сигнала делителя 15 частоты. Зто при" водит к записи в ячейку второго блока

25 оперативной памяти логической "1" по адресу, определяемому выходным 5 кодом сумматора 13, и установке третьего триггера 21 в состояние, при котором на его первом выходе - логическая,"1", а на втором - логический "0". На выходе третьего элемен" та И 23 появляется "0", т.е. разрешается работа второго счетчика 8, При появлении "0" на выходе делителя 15 происходит считывание информации из блоков 5 и 25 оперативной памяти, Однако прохождение выходной информации первого блока 5 оперативной памяти через первый элемент И 6 блокировано, так как на первом входе элемента И 6 - логический "0", Устройство осуществляет обработку входного сигнала аналогично, с той лишь разницей, что обрабатывается информация, считываемая из второго блока 25 оперативной памяти, т.е. прием ведется по отрицательному " фронту входного сигнала, Формула изобретения

Устройство декодирования тональных сигналов по авт. св, Р 1160614, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости, в него введены третий триггер, третий и четвертый элементы И, второй элемент ИЛИ, второй блок оперативной памяти, при этом первый вход третьего триггера соединен с дополнительным выходом синхрогенератора и информационным входом второго блока оперативной памяти, адресные, первый и второй управляющие входы которого соединены соответственно с адресными, первым и вторым управляющими входами первого блока оперативной памяти, второй вход третьего триггера соединен с вторыми входами первого и второго триггеров и выходом блока начальной установки, а первый выход подключен к первому входу четвертого элемента И, второй и третий входы которого соединены соответственно с выходом и вторым управляющим входом второго блока опера- тивной памяти, выход четвертого элемен 1 та И подключен к второму входу второго элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, а выход подключен к объединенным первому входу второго триг" гера и второму входу третьего счетчика, а вторые выходы первого и третьего триггеров соединены соответственно с первым и вторым входами третьего элемента И, выход которого соединен с объединенными первыми входами первого и второго счетчиков.