Процессор быстрого преобразования фурье

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано при решении задач гармонического анализа, где необходимо производить обработку сигналов в реальном . масштабе времени. Цель изобретения - повышение быстродействия процессора. Поставленная цель достигается тем, что он содержит четыре блока оперативной , блок постоянной памя- ;ти, арифметический блок, десять мультиплексоров , пять регистров адреса, дешифратор адр.еса, элемент ИЛИ, сдвиговый регистр, блок синхронизации и соответствующие связи между узлами процессора. 2 ил. СЛ е g 00 00 00 u

СООЗ СОНЕТСНИХ

СО) 1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (19) (11) (51) 4 С 06 F 15/332

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К Д BTOPCHOiVlV СВИДЕТЕЛЬСТВУ.

ГОСУДАРСТ8ЕННЫЙ НОМИТЕТ СССР

llO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3874334/24-24 (22) 23,12,84 (46) 23.12.86. Бюл. 9 .47 (72) В.A.Шаньгип, П.П.Перьков и В,Е.Мельник (53) 681.32(088.8) (56) Авторское свидетельство СССР

У 590750, кл, G 06 F 15/332, 1978.

Авторское свидетельство СССР

11 11190?7, кл. G 06 F 15/332, !982. (54) ПРОЦЕССОР БЫСТРОГО ПРЕОБРАЗОВА НИЯ ФУРЬЕ (57) Изобретение относится к вычислительной технике и может быть использовано при решении задач гармонического анализа, где необходимо производить обработку сигналов в реальном . масштабе времени, Цель изобретения— повышение быстродействия процессора.

Поставленная цель достигается тем, что он содержит четыре блока оперативной памяти, блок постоянной памя,ти, арифметический блок, десять мультиплексоров, пять регистров адреса, дешифратор адреса, элемент ИЛИ, сдвиговый регистр, блок синхронизации и соответствующие связи между узлами процессора. 2 ил.

1278884

Изобретение относи1 .Ся к нычисли.тел1:най технике и мажет быть нспользоиано прп решении .задач гармонического апа:п1за., где необходимо производить отработку сигнала B реальном 5 масштабе времени,, Целью изобретения янляется повыше не Сыстродейстипя процессора.

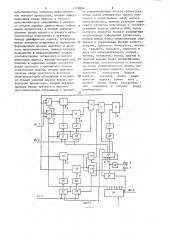

На фиг.,) прецстанлепа функциональная схе b!1 Hpolleccopa; на фиг,2 — вре-10 менная Днагт)аг111а рабаты процессора ,для Ы = 512 гочек, Процессор БПФ стэдерл1т мультиплексор 1, блОки 2 H 3 o(lcpaTHBHoй IlaMB» ти, гну)1ьтип.т1ексарь1 4 H 5, арит))етичес1(Hl; блат(6 ре! пстртт 7 и Я адреса (мультиплексоры 9 и 10, блок 11 посTOlПП1О1I 1la!!!ITH, т Pa«11С !7 1 2 Л,PBCa т

)бтт.)к ) 3 >те111111)?ратара адреса, G. Iol(H 1 4

H 5 ап(>l)aTIIBHojj памяти, мул,типлексоры 16 -:1 ) /> .)31еттсп1 ИЛ)1 )8, реГ11(. T" рl>1 1 9 и 20 а !p Оса., (иTepa;!>1ан—

EIbE.I ) сдннГoB! Iй pr Ã.".тстр 2 ), гтульт11плексары 22 и ?3, Слок 24 жп(хронизацтзтт и ьгультпплексар 25.

Ра(:смотрим р(1бату процессора На !

E1)H1 Iepv. обр;1.6o T!(H !!accHDa ттт1инай

) 2 1атт к, J> ттСХОЦНОМ СОС "с ОЯНИИ BCQ РЕГHCTPbl .Обгтулечы, I!a нервам выходе блока 24

30 устапав>1г1вается уровень "1", при этом D мультипле ссорах 1,, ;,9,10,16, 1 7,. 22 23 и 25 буд) т Отl(pbll ы Для Нро хо)т(ден1111 информа тпн пергые входы. На пятам выхаце дегш(с!)ратара 3 у "Taнаcc витая уровень и пр,! этом н мультиплексоре 5 будет открыт первый вход. !!а Bb!E(o!:,е разрешеяия операций ввода-вывода уст «oB»Tcя уровень"0, 40 чта является сигналам запрета вьпталНЕНИ)-.. ЭТНХ ОПЕРа1тнй ДЛЯ Н11ЕШГ1ИХ УСтройств.

С приходом залускающега импульса на нхад.aa!IycE(a блока ?4, блок 24

СИ11Хр>ОП11эа1т1111 НаЧИНаЕт ВшрабатЫВатЬ

TaE(1 ОВНЕ СИГНатЬЫ с(ЛЯ BCC .Õ )тстт)айтстн, При этом н первый разряд регистра 21 сдвига устанавливается "1 и !Ia вьтходе разр ешения выполнения аперацип ввода-вывода уc I aEIBBJ!HBaå>ñÿ сигнал

50 ттс ст что разре111ае г внешним ус I ðoéñòDai>! . 3bIIIOJ>>Ie11HP. O.>el>;1Ц11тт т> с)(7да ВЬ>НОДа

11ас(.HD чпce!!, который неабха„тима Обрабата 1», поступает «а вход працсссора. H д(2лее через вход г(ультиплексо1)а

1 — на вход блока. 2. }1а адресный вход блат:.а 2 чер 3 зхад му)1ыип>1ексара 9 и ас Hстр 7 поступают адреса, котG рые вырабатывает внешнее устройство синхронно с входной информацией и подает на первый адресный вход процессора. Одновременно с вводом информации в процессоре выполняется операция обработки информации (операция БПФ), При этом дешифратор 13 вы" рабатынает на третьем выходе адреса операндов, по которым производится считынание информации из блока 3.

Через вход мультиплексора 10 адреса поступают на регистр 8 и далее — на адресный вход блока 3. Информация с вь1хода блока 3 через входы мультиплексоров 4 и 5 поступает на информационный вход блока 6. На первом выходе дешифратора 13 формируются адреса весовых коэффициентов, которые записынатотся в регистр 12, С гыхода блока )! считываются весовые коэффициенты, которые синхронно с входными операндами поступают на вход задания каэф )итциентов блока

6. В блоке 6 выпал:тяются базовые операции алгоритман БПФ. Результаты вып1слений с выхода блока 6 поступают на нхады блоков 14 и 15. При выполнении первой итерации БПФ (нечетных итерациях) блок синхронизации вырабатывает строб записи для блока 15.

Па четвертом выходе дешифратора

13 вырабатываются адреса, по которым производится запись результатов базовой операции в блок 1". Опи поступают на адресный вход блока 15 через нход мультиплексора 22 и регистр 30.

Одновременно с операциями ввода информации и обработки в процессоре выполняется операция вывода информации, которая была абраСотана на предьщуцем цикле вычислений. При этом внешнее устройство выставляет на второй адресный вход процессора адреса, по которым необходимо считать инфармап11ю. Через вход мультиплексора 22 адреса поступают на регистр 19 и далее па адресный вход блока 14. Из блока 14 считывается информация, I оторая через вход мультиплексора 17 поступает на информационный выход процессора и далее во внешнее устройство. После выполнения первой итерации на выходе дешифратара !3 устанавливается уровень О и при этом в мультипгексаре 5 открывается второй нхад. На втором выходе дешифратора

13 формируется сигнал, по которому происходит сдвиг "1" в регистре 21

127Е8Я4

50

20

50 во второй разряд. 11ачпнает HEI

Процесс вычисления на последующих итерациях ныполняется аналогичным образом. После выполнения последней, денятой, итерации регистр 21 обнуля.ется и с выхода переноса сигнала "!" поступает на вход останона блока 24.

Процессор переходит в режим останова.

При этом на выходе разрешения выполнения операции ввода-вывода устанавливается сигнал 0, что служит сигналом запрета для операций ввода-вывода.

Таким образом, н блоке 15 находится результат вычислений операцпп БП<1>, в блоке 2 введен новый входной массив информации, который необходимо обработать, а в блоке 14 находится информация, которая выведена из процессора но внешнее устройство. С приходом второго запускающего импульса в процессоре сиона начинается выполнение операции БПФ. При этом, блоки

2 и 14 памяти заняты для хранения результатон вычислений на итерациях, поочередно работая в режиме считывания-записи. По окончании операции н блоке 14 находятся результаты вычислений.

Блок 3 памяти представлен внешнему устройству для ввода информации, которую необходимо обработать на следующем цикле вычислений. Блок 15 памяти в это нремл представлен ьнешнему устройству и из него считываются результаты предыдущей обработки.

Формула изобретения

Процессор быстрого преобразования

Фурье, содержащий арифметический блок, перный и второй блоки оперативной памяти, адресные входы которых подк почень1 к выхоцам соответственно первого и второго регистров адреса, информационные входы которых подключены к ныходам соответственно первого и второго мультттексорон, вход задания коэффициентов арифметического блока подключен к выходу блока постоянной памяти, третий адресный вход которого подключен к выходу третьего регистра адреса, информационный вход которого подключен к первому выходу деши<1>ратора адреса, первый вход которого подключен к инфор,мационному гыходу сднигового регистра, тактовый вход которого подключен к второму выходу дешифратора адреса, выход переноса сдвигового perистра подключен к входу остапова блока синхронизации, вход запуска которого явллется входом запуска процессора, входом на:альной устапонки процессора лнллетсл вход начальной установки блока синхронизации, информационный выход арифметического блока подключен к первому информационному входу третьего мультиплексора, выход которого подключен к информационному входу первого блока оперативной памяти, выход которого подключен к первому информационному входу четвертого мультиплексора, второй информационный вход которого подключен к выходу второго блока оперативной памяти, отличающийся тем, что, с целью повышения быстродействия, н него введены третий и четвертый блоки оперативной памя "и, четнертый и плтый регистры адреса, шесть мульти- . плексоров и элемент ИЛИ, причем .ныход четвертого мультиплексора подключен к первому информацпонному нходу пятого мультиплексора, выход которого подключен к информационному входу арифметического блока, ипформацпоппыи выход которого подключен к первому информационному входу шестого мультиплексора и информационным входам третьего и четвертого блоков оперативной памлти, выход третьего блока оперативной памяти подключен к перным информационным входам седьмого и восьмого мультиплексоров, выход четвертого блока оперативной памяти подключен к вторым информационпым входам седьмого и восьмого мультиплексоров, выход седьмого мультиплексора подключен к второму информационному входу плтого мультиплексора, а информационный выход восьмого

5 127 мультиплексора является информационным выходом процессора, первые информационные входы первого и второго мультиплексоров объединены и являются входом задания адреса ввода информации процессора;; а вторые информационные входы первого и второго мультиплексоров подключены к третьему выходу дешифратора адреса, четвертый выход которого подключен к первым информационным входам девятого и десятого мультиплексоров, выходы которых подключены к информационным входам соответственно четвертого и пятого регистров адреса, выходы которых подключены к адресным входам соответственно третьего и четвертого блоков оперативной памяти, вторь1е информационные входы девятого и десятого мультиплексоров объединены и являют-. ся входом задания адреса вывода информации процессора, вторые информационные входы третьего и шестого мультиплексоров объединены и являют8884 б ся информационным входом процессора, пятый выход дешифратора адреса подключен к управляющему входу пятого мультиплексора, выходы разрядов сдви5 гового регистра подключены к соответствующим входам элемента ИЛИ, выход которого является выходом разрешения ввода-вывода информации процессора, первый выход блока синхронизации под1С ключен к управляющим входам первого, второго, третьего, четвертого, шестог"o, седьмого, восьмого, девятого и десятого мультиплексоров, второй, третий„ четвертый, пятый, шестой и

15 седьмой выходы блока синхронизации подключены соответс-вeíío к тактовому входу арифметического блока, управляющим входом первого, второго, третьего, четвертого блоков

20 иамлти, третьему входу дешифратора адреса, кроме того второй выход блока синхрониэа ции подключен к второму входу дешифратора, 25

1278884

Итерации

И перации адад к+1)

ОЗУ2Щ

1259557gg 1250567Я9

Счип ыбание(запись) 3апись Считыбание(запись

I l аМ(К-?) ИПМК. 1) игиерацди ВыЫ (h 1)

I. I

ОЛУХА(15) г г 5 "567 В9

1

1 23956 70

Запись(считы спиел СчитыЗание Запись(считыЗапи ! (1 l

Итерации I ЮВР (К+Я)

ОЩ1(г)

125 956788

Запись 1Считьдание(лпись/1 Зались

1 I l

I I

Б/7Ф(/ )

1 ) . в&У(к-z) Еьз&о (к) I

ОЗУЗ119)

1239567 Я

Считыбание Запись(считы8ание) Считыдание

Мод (К) Составитель АьБаранов

Техред A.Êðàâ÷óê

Редактор В.Иванова

Корректор ОьЛуговая

Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Заказ 6841/49

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4