Устройство для синусно-косинусного цифроаналогового преобразования

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления. Целью изобретения является расширение области применения за счет преобразования с различной дискретностью задания и расширения класса решаемых задач за счет имитации сигналов реальных датчиков. Устройство содержит блок 1 постоянной памяти, блок 2 выборки, реверсивные счетчики 3 и 4, блок 5 реверса счет, селектор 7 квадрантов, генераторы синусной 8 и косинусной 9 функций, фаэоинверторы 10 и 11, цифроаналоговые преобразователи 1-2-15, сумматорчл 16 и 17. Формирование сигналов сину са и косинуса осуществляется С помощью линейной амплитудной модуляции опорных напряжений 4 сигналов положительных обратных связей с последующим суммированием с соответствующим масштабным коэффициентом сигналов , полученных в результате модулдций. Устройство обеспечивает возможность построения унифицированных преобразователей, работакяцих в сис темах с различной дискретностью задания, и возможность имитации (с учетом внутришаговой погрешности) сигналов реального индукционного датчика. 1 з.п. ю-лы, 2 ил. (Л

СОК)З СОВЕТСНИХ

И

РЕСПУ БЛИН

09) (11) (50 4 С 06 С 7/22

ОПИСАНИЕ ИЗОБРЕТЕНИЯ н авто сномм свидетвъствм

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3543126/18-24 (22) 10.01.83 (46) 23.12.86. Вюл. У 47 (72) А.Н. Черногорский и В.И.Цветков (53) 681.3(088.8) (56) 1. Авторское свидетельство СССР

У 551659, кл. G 06 С 7/22, 1977.

2. Патент США Р 3728719, кл. Н 03 К 13/02, опублик. 1973. (54) УСТРОЙСТВО ДЛЯ СИНУСНО-КОСИНУСНОГО ЦИФРОАНАЛОГОВОГО ПРЕОБРАЗОВАНИЯ (57) Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления.

Целью изобретения является расширение области применения за счет преобразования с различной дискретностью задания и расширения класса решаемых задач за счет имитации сигналов реальных датчиков. Устройство содержит блок 1 постоянной памяти, блок 2 выборки, реверсивные счетчи" ки 3 и 4, блок 5 реверса счета, селектор 7 квадрантов, генераторы синусной 8 и косинусной 9 функций, фазоинверторы 10 и 11, цифроаналоговые преобразователи 1-2- 15, сумматоры, 16 и 17. Формирование сигналов синуса и косинуса осуществляется с помощью линейной амплитудной модуляции опорных напряжений 4 сигналов положительных обратных связей с последующим суммированием с соответствующим масштабным коэффициентом сигналов, полученных в результате иодуляций. Устройство обеспечивает возможность построения унифицированных преобразователей, работающих в системах с различной дискретностью задания, и возможность имитации (с учетом внутришаговой погрешности) сигналов реального индукционного датчика. 1 з.п. в-лы, 2 ил.

1278897

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах числового программного управления.

Известно устройство синусно-косинусного преобразования с заданием узловых точек аппроксимации с помощью ряда опорных напряжений и с аппроксимацией функций синуса и косинуса между узловыми точками путем линейной амплитудной модуляции опорных напряжений цифровыми сигналами, сформированными из сигнала задания, содержащее блок задания узловых точек аппроксимации, входной счетчик, селектор квадрантов, селектор точек аппроксимации, дешифраторы, линейные реэистивные сетки, выходной фазоинвертор f1) .

Наиболее близким к изобретению по технической сущности является устройство синусно-косинусного преобразования, основанное на преобразовании опорных напряжений по законам аппроксимирующих функций где W =-1,80148; — угол задания в текущем квадранте датчика; к(у), К*()1) " линейные положительные функции, дополняющие друг друга до единицы.

Известное устройство содержит селектор квадрантов, генератор синуса, в состав которого входит первый фазоинвертор и первый цифроаналоговый преобразователь, связанный выходом с первым входом первого сумматора, и генератор косинуса, в состав которого входит второй фазоинвертор и второй цифроаналоговый преобразователь, связанный выходом с первым вхоцом второго сумматора (2J .

Недостатком известных устройств является ограниченность возможностей прц выборе дискретности аргумента и соответственно при выборе числа дискрет деления шага индукционного датчика (периода синусной и косинусной функции), что исключает возможность перенастройки схемы устройства на различные дискретности задания входного угла.

Кроме того, недостатком является отсутствие возможности учета внутришаговой погрешности датчика при преобразовании, т.е, отсутствие возможности имитации сигналов реального индукционного,цатчика типа индуктосин или вращающийся трансформатор, например, для целей компенсации погрешностей датчиков в следящих системах.

Цель изобретения - расширение области применения за счет преобразования с разл)лчной дискретностью задания и расширение класса решаемых задач эа счет имитации сигналов реальных датчиков.

Поставленная цель достигается тем, что .устройство для синусно-косинусного цифроаналогового преобразования, содержащее селектор квадрантов, генератор синусной функции, содержащий первый фазоинвертор, первый сумматор

1 и первый цифроаналоговый преобразователь, аналоговый вход которого соединен с шиной первого опорного напряжения,, а выход — с первым входом первого сумматора, и генератор косинусной функции, содержащий втоЗО рой фазоинвертор, второй сумматор и второй цифроаналоговый преобразователь, аналоговый вход которого соединен с шиной второго опорного напряжения, а выход — с первым входом второго сумматора, выходы первого и второго фазоинверторов являются выходами устройства., содержит блок постоянной памяти.„ блок выборки, первый и второй реверсивные счетчики, блок реверса счета, третий и четвертый цифроаналоговые преобразователи, при этом вход устройства соединен с первым информационным входом блока реверса счета, первый и второй выходы которого соединены с входами управления реверсом соответственно первого

1 и второго реверсивных счетчиков, а третий выход блока реверса счета:.— со счетным входом первого и второго

О реверсивных счетчиков, выходы отрицательного переноса которых соединены соответственно с вторым и третьим информационными входами блока реверса счета, четвертый выход которого

55 соединен с входом селектора квадрантов и с информационным входом блока выборки, а пятый выход — с управляющим входом блока выборки, выход которого соединен с входом блока пос1278897 тоянной памяти, выход которого соединен с кодовыми входами первого и второго реверсивных счетчиков, кодовый выход первого реверсивного счетчика соединен с кодовыми входами перваго и четвертого цифроаналоговых преобразователей, кодовый выход второго реверсивного счетчика соединен с кодовыми входами второго и третьего цифроаналоговых преобразователей, 10 выход третьего и четвертого цифроаналоговых преобразователей соединен с вторыми входами соответственно первого и второго сумматоров, выход первого сумматора соединен с анало- 15 говым входом третьего цифроаналогового преобразователя и с информационным входом первого фазоинвертора, выход второго сумматора соединен с аналоговым входом четвертого цифро- 20 аналогового преобразователя и с информационным входом второго фазоинвертора, первый информационный выход селектора квадрантов соединен с входом определения направления счета блока реверса счета, второй и третий информационный выходы селектора квадрантов соединены со знаковыми входами соответственно первого и второго фазоинверторов, а также тем, 30 что блок реверса счета содержит коммутатор, первый и второй RS-триггеры, формирователь импульсных последовательностей, первый, второй, третий и четвеРтый элементы ИЛИ и формирова- 35 тель импульсов, первый и второй выходы которого являются первым и вторым управляющими выходами блока, а третий и четвертый выходы соединены с первыми входами первого и второго 40 элементов ИЛИ, выход которых подключены к третьему выходу блока, первый и второй входы третьего элемента ИЛИ соединены с S-входами первого и второго RS-триггеров и явля- 45 ются вторым и третьим информационными входами блока, выход третьего элемента ИЛИ соединен с управляющим входом формирователя -импульсных последовательностей, информационный 50 вход которого соединен с информационным входом коммутатора и является первым информационным входом блока, выход формирователя импульсных последовательностей является четвертым выходом блока, прямые выходы RS-триггеров соединены с соответствующими входами формирователя импульсов, а инверсные выходы — с соответствующими входами четвертого элемента

ИЛИ, выход которого является пятым выходом блока, первый и второй выходы коммутатора соединены с вторыми входами соответственно первого и второго элементов ИЛИ, управляющий вход коммутатора является входом определения направления счета блока.

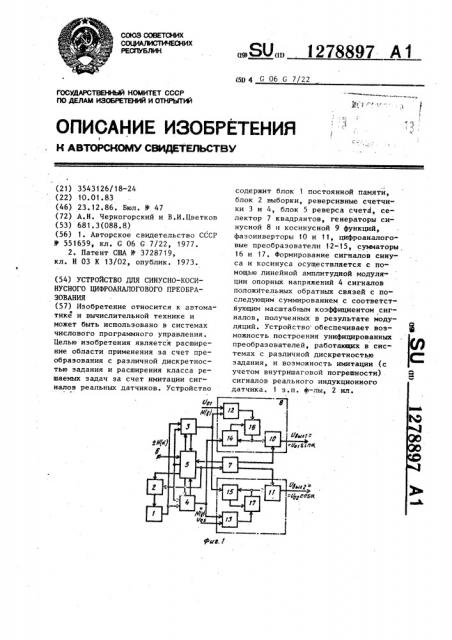

На фиг. 1 представлена схема предлагаемого устройства; на фиг. 2 схема блока реверса счета и селектора квадрантов.

Устройство содержит блок 1 пос-. тоянной памяти, блок 2 выборки, реверсивные счетчики (РС) 3 и 4, блок 5 реверса счета, вход 6, селектор 7 квадрантов, генератор 8 синусной функции, генератор 9 косинусной функции, фазоинверторы 10 и.11, цифроаналоговые преобразователи (ЦАП) 12-15, сумматоры 16 и 17, селектор 7 квадрантов содержит реверсивный счетчик 18 и элемент ИСКЛОЧАЮЩЕЕ ИЛИ 19.

Блок 5 реверса счета содержит коммутатора 20, RS-триггеры 21 и

22, элементы ИЛИ 23-26, формирователь 27 импульсных последовательностей, формирователь 28 импульсов, выходы положительной 29 и отрицательной 30 импульсных последовательностей, образующие первый информационный выход блока 5.

Устройство работает следующим образом.

Выходные сигналы идеального индукционного датчика, имеющие вид

U, =1.1 созеsinut;

11 =17 з пм.. sinut, на практике реализуются с ошибками.

Основная причина этого явления— внутрипериодная (внутришаговая) по-. грешность датчика. Это в основном технологическая погрешность. Ее главные составные части могут быть аппроксимированы с помощью гармонических функций вида sin K и

cos Ka, где К=1,2,4. Наибольший удельный вес средч них имеет первая гармоника. Она обусловлена, в основном, геометрической неортогональностью синусных и косинусных обмоток датчика и проявляется в электрической асимметрии синусного и косинусного сигналов.

1278897

Эту погрешность можно воспроизвести и, тем самым скомпенсировать с помощью предлагаемого устройства.

:Это обеспечивается следующим образом.

Опорные напряжения 001 и 002 мо дулируются в каналах синуса и косинуса первым N(g) и вторым М*() цифровыми модулирующими сигналами соответственно. Эти сигналы изменяются по законам линейной аппроксимации 10 функций /sing/ и /cosa / соответственно.

Сигналы. N(() и N*()) формируются из входной последовательности счетных импульсов . М(М), в которой каждый импульс соответствует элементарному углу задания в

5 йЖ

2 II оЯ, с, ° М

Для реального датчика, имеющего внутришаговую погрешность, угол / связан с ю(. следующими зависимостями н + -.о 0 оа 1;

25 с "., Ii О

f =II40 -сб 1 — +g c Я, о "-м 1 н4R фо а II4f (1) 3, У -2 -ot, — Т4 3 о а 2;, 3 Г ««»

Таким образом, угол — пересчитанный к квадрантам датчика угла о6

3", о ", 8 "" — составляющие погрешности в точках о /2, Ч, 3/2и. (о6 " угол поворота вектора задания в З5 декартовой системе координат, ) угол поворота вектора в системе координат, образованной электрическими полуосями датчика; они повернуты относительно декартовых осей и обра- 40 зуют квадранты датчика, которые не ,совпадают с декартовыми квадрантами).

Если обозначить через " максиоэ мальное значение угла в квадранте

S то для каждого квадранта, начи- 45 ная с первого, эта величина равняется — или (4)

М(У) о 2"!

"5(siin) =U, к, к(у), с() 1 где U — сигнал, полученный в результате модуляции напряжения U цифровым модулирующим сигна—

50 лом N(g);

К = — — масштабный коэффициент

5 линейной модуляции.

Задавая величины сигналов М, которые являются сигналами начальных условий датчика, меняем поквадратно амплитуды сигналов, получаемых в результате линейной модуляции. Сигналы М предварительно формируются, исрФММ g IIII

II 4% (2) Величина является начальным условием квадранта S для выбранного датчика и выражается в угловых единицах измерения, Если в качестве единицы измерения использовать элементарный угол задания Ь|у„, то углу соответствует число

При этом числовые значения модулирующих сигналов определяются из следующих выражений:

Таким образом, цифровые сигналы

N(() и М*() меняются по законам линейных функций. Они представляют собой двоичные коды разрядности и и формируются путем суммирования счетных импульсов :М(ос) от нуля до величины N и путем вычитания — от

5 величины N до нуля в каждом квадранте датчика. При этом один сигнал всегда возрастает, а другой — убывает. При смене квадранта направления задания угла о характер изменения модулирующих сигналов меняется на противоположный

Сигналы М (g) и N*(g), как уже отмечалось, используются в генераторах синуса и косинуса для линейной модуляции опорных напряжений Uo,, Ъ

U и формируемых сигналов, которые используются также в качестве сигналов положительных обратных связей.

Линейная модуляция этих сигналов, например модуляция опорного напряжения U сигналом N(g) в канале синуса осуществляется по следующему закону:

12788 ходя из дискретности задания с и величин внутришаговых погрешностей датчика b5, и запоминаются. Величина сигнала N равняется числу дис5 крет деления квадранта S датчика.

Поэтому для числа N справедливо следующее равенство:

ы г. Ъ 4

Максимальная величина сигнала

N =2

5 ма с используется для выбора разрядности кодов N(g), N*(f), И

Величина N и, следовательно, число дискрет деления квадранта датчика меняется от квадранта к квадранп-t ту, не превьппая значения 2 . Этим 20 обеспечивается решение задачи имитации сигналов реального индукционного датчика и, соответственно, решение задачи по компенсации составляю щей внутришаговой погрешности датчика. Кроме того, сохраняя разрядность аппаратных средств преобразования, можно переходить на другую дискретность задания ЬМ, т.е. менять число

N и его слагаемые М . Благодаря это- 30 му можно строить унифицированные преобразователи, т.е. использовать один и тот же преобразователь в различных системах, отличающихся друг от друга дискретностью задания. При пере- 35 ходе от одной дискретности задания к другой формируются и запоминаются новые сигналы начальных условий N а также в масштабном коэффициенте суммирования меняется коэффициент К . 40

Формирование сигналов синуса и косинуса осуществляется с помощью линейной амплитудной модуляции опорных напряжений и сигналов положитель- g5 ных обратных связей с последующим суммированием с масштабным коэффици1 ентом К 1 сигналов, получен5 ных в результате этих модуляций. 50

Масштабный коэффициент линейной модуляции К в масштабном коэффициен3 те суммирования учитывает изменения амплитуд сигналов, получаемых в результате модуляции, и служит для сохранения неизменным общего коэффициента передачи.

Формирование функций синуса и косинуса в пределах всего периода со/

97 8 провождается сменой полярности сигналов L (;,) и Н -,, ) в зависимости от номера квадранта.

На вход устройства поступает тактированная последовательность счетных имп3 пьсо в N (0(,) один импульс ко торой соответствует дискрету задания.

В зависимости от знака задания импульсная последовательность поступает на положительный или отрицательный вход блока 5 реверса счета (на чертеже входы функционально объеди-. нены в один информационный вход).

Счетные импульсы здесь тоже коммутируются в зависимости от значения младшего разряда кода номера S текущего квадранта датчика и подаются на счетные входы РС 3 и 4, в которых последовательный код преобразуется в два и-разрядных параллельных кода: в прямой код N()) в PC 3 и в дополняющий его до кода N код N*(g) в РС 4;

При этом

"(3 ) + "*(У) "5.

Реверсивные счетчики 3 и 4 считают импульсы синхронно, но всегда в противоположных направлениях. Реверс счетчиков осуществляется в блоке 5 реверса счета при смене знака задания или при смене номера квадранта, код которого формируется в селекторе 7 квадрантов. Текущее значение угла о в пределах одного квадранта хранится в виде кодов N(g) и

N*(g) в РЗС 4. При этом сигнал 1 pS с первого выхода селектора 7 квадрантов используется в блоке 5 для определения направления счета реверсивных счетчиков 3 и 4. Кроме того, в селекторе 7 квадрантов осуществляется дешифрация кода 2pS, 1pS и на втором выходе формируются сигналы управления фазоинверторами 10 и 11.

Номер квадранта меняется в селекторе 7 квадрантов по импульсам отрицательного переноса Р2, которые поступают через блок 5 с первых выходов

PC 3 и 4. Таким образом, импульс Р2 является сигналом смены квадранта.

Он формируется в РС, работающем на вычитание при переходе от кода 00 ...00 к коду 11...11. По сигналу

Р2 блоком 5 производят следующие операции: реверс счетчиков 3 и 4; установка в нуль РС, который сформировал импульс Р2 (в новом квадран1023 1

1024

9 127889 те PC работает на сложение); запись начальных условий N нового квадран5 та в другой PC который работает на вычитание, формирование и подача на счетные входы РС 3 и 4 дополнительного импульса, компенсирующего поте-, рю счетного импульса, вызвавшего импульс переноса Р2. После этого импульса в одном счетчике записано число 1 (одна дискрета), а в другом — 10 (И -1).

Начальные условия N заносятся в

РС 3 и 4 из блока 1 с помощью блока 2 выборки, который управляется сигналами из блока 5 реверса счета.

Сюда поступает команда выборки, которая формируется в блоке 5, а также импульсы Р2. Блок 2 выборки содержит свой PC квадрантов, где хранится номер текущего квадранта S датчика 20 (абсолютный номер, отсчет от первого шага датчика). Этот номер является адресом ячейки ПЗУ 1, хранящий начальные условия N данного квадран2S та. Для датчика 6 одной парой полю-сов в ПЗУ хранятся четыре числа, а для датчика с несколькими парами полюсов — соответственно больше. Например, для имитации сигналов реального индукционного датчика типа индук- 30 тосин с числом пар полюсов 180 в ПЗУ необходимо записать 720 чисел.

Двоичные коды N(y) и N*(g) с вторых выходов PC 3 и 4 подаются на цифровые входы ЦАП 12-15. B ЦАП 12 и 13 35 осуществляется модуляция опорных напряжений Uor, U, а в ЦАП 14 и с (э 1 H UG (oos j торые формируются в сумматорах 16 и 17 соответственно. Каждый ЦАП в 40 данном устройстве построен на основе резистивной сетки типа R-2R с ключами и операционного усилителя.

При подаче на аналоговые входы 4

UhII 12 и 13 синусоидального опорного напряжения

7 10

Рассмотрим несколько примеров выбора параметров преобразования N> и К для преобразователя раэряднос5 тью n=10 (N =1023) в зависимости

ware от значений исходных данных N„ и

b(ec) .

Пример 1. Дано: Нц Иэмакс

g (с6) =0.

Выбираем N =Ят=:Бз=М4=Язм.„,=1023.

Тогда

Пример 2. Дано- N„=2000, Р(М) =О.

Тогда М =500, Кэ=

Пример 3. Дано: N„=2000, 3*=27, 5 **=-18, ***=-22,5 .

Учитывая выражения (2) и (3), получаем Nr =650, N =250, N =475, N =625. 650 250

1024 1024

475 К 625

1024 1024

Пример 4. Дано- Н =4000, Р*=0,36, 3**=-0,18, g**%=-0,54 .

N =1004, N =994, Из=996, М„1006.

1004 994 996

1024 1024 1024

1006

4 1024

Таким образом, предлагаемое устройство обеспечивает возможность построения унифицированных преобразователей, работающих в системах с различной дискретностью задания, и возможность имитации (с учетом внутришаговой погрешности) сигналов реального индукционного датчика.

Это определяет технико-экономический эффект от использования изобретения.

Ф о р м у л а изобретения б ® Ыпу1

50 с выходов синусно-косинусных преобразователей снимаются два напряжения, модулированные по законам, аппроксимирующим функции синуса и косинуса 55

П „„, йП ззп g sing t;

"ььи, =Umcos C э1п t

1. Устройство для синусно-косинусного цифроаналогового преобразования, содержащее селектор квадрантов, генератор синусной функции, содержащий первый фазоинвертор, первый сумматор и первый цифроаналоговый преобразователь, аналоговый вход которого соединен с шиной первого опорного напряжения, а выход — с первым входом первого сумматора, и генератор косинусной функции, содержащий второй фа11 12788 зоинвертор, второй сумматор и второй

;цифроаналоговый преобразователь, аналоговый вход которого соединен с шиной второго опорного напряжения, а выход — с первым входом второго сумматора, выходы первого и второго фазоинверторов являются выходами устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения области применения за счет преобразования с fO различной дискретностью задания и расширения класса решаемых задач за счет имитаЦии сигналов реальных датчиков, оно содержит блок постоянной памяти, блок выборки, первый и вто- 15 рой реверсивный счетчики, блок реверса счета, третий и четвертый цифроаналоговые преобразователи, при этом ,вход устройства соединен с первым информационным входом блока реверса Z0 счета, первый и второй выходы которого соединены с входами управления реверсом соответственно первого и . второго реверсивных счетчиков, а третий выход блока реверса счета — 25 со счетным входом первого и второго реверсивных счетчиков, выходы отрицательного переноса которых соединены соответственно с вторым и третьим информационными входами блока ре- 30 верса счета, четвертый выход которого соединен с входом селектора квадрантов и с информационным входом блока выборки, а пятый выход — с управляющим входом блока выборки, вы- З5 ход которого соединен с входом блока постоянной памяти, выход которого соединен с кодовыми входами первого и второго реверсивных счетчиков, кодовый выход первого реверсивного 40 счетчика соединен с кодовыми входами первого и четвертого цифроаналоговых преобразователей, кодовый выход второго реверсивного счетчика соединен с кодовыми входами второго и третьего 45 цифроаналоговых преобразователей, выходы третьего и четвертого цифроаналоговых преобразователей соединены с вторыми входами соответственно первого и второго сумматоров, выход 50 первого сумматора соединен с аналоговым входом третьего цифроаналогового преобразователя и с информационным

97 12 входом первого фазоинвертора, выход второго сумматора соединен с аналоговым входом четвертого цифроаналогового преобразователя и с информационным входом второго фазоинвертора, первый информационный выход селектора квадрантов соединен с входом определения направления счета блока реверса счета, второй и третий информационные выходы селектора квадрантов соединены со знаковыми входами соответственно первого и второго фазоинверторов.

2. Устройство по п. 1, о т л и— ч а ю щ е е с я тем, что, блок реверса счета содержит коммутатор, первый и второй RS-триггеры, формирователь импульсных последовательностей, первый, второй, третий и четвертый элементы ИЛИ и формирователь импульсов, первый и второй выходы которого являются первым и вто рым выходами блока, а третий и четвертый выходы соединены с первыми входами первого и второго элементов ИЛИ, выходы которых подключены к третьему выходу блока, первый и второй входы третьего элемента KIH соединены с S-входами первого и второго RS-триггеров и являются вторым и третьим информационными входами блока, выход третьего элемента HJIH соединен с управляющим входбм формирователя импульсных последовательностей, информационный вход которого соединен с информационным входом коммутатора и является первым информационным входом блока, выход формирователя импульсных последовательностей является четвертым выходом блока, прямые выходы RS — òðèããåðîâ соединены с соответствующими входами формирователя импульсов, а инверсные выходыс соответствующими входами четвертого элемента ИЛИ, выход которого является пятым выходом блока, первый и второй выходы коммутатора соединены с вторыми входами соответственно первого и второго элементов ИЛИ, управляющий вход коммутатора является входом определения направления счета блока.

1278897

Составитель Г. Осипов

Редактор Г. Волкова Техред Л.Сердюкова корректор А. Ильин

Заказ 6842/50 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4