Устройство для обнаружения ошибок в блоках памяти программ

Иллюстрации

Показать всеРеферат

Устройство для обнаружения он1ибок в блоках памяти программ относится к области вычислительной те.хники. Изобретение позволяет повысить точность контроля блоков памяти программ за счет обнаружения ошибок непосредственно в процессе работы . Обнаружение ошибок производится за счет вычисления контрольного числа совокупности считанных слов, принадлежащих контролируемому модулю памяти, и сравнения с эталонной константой. Устройство позволяет обеспечить однократный учет каждого считанного слова даже при многократном обрагцении к нему. Устройство содержит блок 1 памяти программ, блок 2 управления суммированием , коммутатор 3, формирователь 4 контрольных чисел, боюк 5 сравнения. 2 з.п. g ф-лы, 2 ил. к д 00 со ОС Ю фиг.

ССФОЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (5в 4 б 11 С 29 00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К ABTQPCHQMY СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3474308/24-24 (22) 23.07.82 (46) 23.12.86. Бюл. № 47 (71) Московский ордена Ленина и ордена

Октябрьской Революции энергетический институт (72) Г. А. Бородин и Н. И. Егорова (53) 681.327 (088.8) (56) Авторское свидетельство СССР № 584338, кл, Ci 11 С 29/00, 1976.

Авторское свидетельство СССР № 235108, кл. G ll С 29/00, 1967.

Жураьлев 1О. Г1. и др. Надежность и контроль ЗВМ. М.: Советское радио, 1978, с. 191. (54) УСТРОИСТВО ДЛЯ ОБНАРУЖЕНИЯ

ОШИБОК В БЛОКАХ ПАМЯТИ ПРОГРАММ

„„SUÄÄ 1278982 (57) Устройство для обнаружения ошибок в блоках памяти программ относится к области вычислительной техники. Изобретение позволяет повысить точность контроля блоков памяти программ за счет обнаружения ошибок непосредственно в процессе работы. Обнаружение ошибок производится за счет вычисления контрольного числа совокупности считанных слов, принадлежащих контролируемому модулю памяти, и сравнения с эталонной константой. Устройство позволяет обеспечить однократный учет каждого считанного слова даже при многократном обращении к нему. Устройство содержит блок

1 памяти программ, блок 2 управления суммированием, коммутатор 3, формирователь 4 контрольных чисел, блок 5 сравнения. 2 з.п. ф-лы, 2 ил.!

?78982

Изобретение относится к вычислительной технике, а именно к устройствам контроля постоянной памяти. и может быть использовано для контроля достоверности хранения информации fl постоянных запоминающих устройствах в процессе работы.

Целью изобретения является повышение точности контроля.

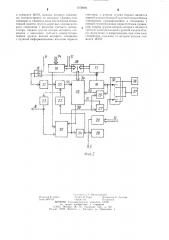

На фиг.1 представлена блок-схема устройства для обнаружения ошибок в блоках памяти программ; на фиг.2 — — блок-схема блока управления суммированием.

Устройство для обнаружения ошибок в блоках памяти программ содержит (фиг.1) блок постоянной памяти, блок 2 управления суммированием, коммутатор 3, формирователь 4 контрольных чисел, блок 5 сравH Chil 5 ., > II!) I B:I !0!I! и и с)хо>>! 6 H в ыхс)д 7 ройств, допил;!итсл)н)ый выхо;! 8 блока 2

>>>IIP3l3 IС 11ИИ C "> МЛIИРОB3iiИЕЫ, ) 1!Р3ВЛЯIОЩИЙ

Bhlxo 9 и в.од !О блока 2 управления суммирован,ем, Iicрвую дополнительную группу 11 в.<о,,ов блока 2 управления сумxIHp0B3IIHxI, первую 12, вторую 13, третью 14 и четвертукэ 1!) группы входов устройства.

Блок 2 управления суммированием содержит (фиг.2) генера" îð 16, первый счетчик !7, первый коммутатор 18, первый блок

19 сравнения, триггер 20, первый 21, второй 22, третий 23 H четвертый 24 одновибряторы, формирователь 25 считывания, элементы И,>(И 26, И 27, второй счетчик 28, BTopoЙ О,!oi< 29 сравнсllH5 втОрОи татор 30, вход 3! «Çklïècü-сч51Т1!вание» блока 32 oперативкой памяти, информационный в,0;!, 33, ядс)есныс входы 34, «ход 35 выборки с>локя 32 оперативной памяти, первый 36 и второй 37 источники напряжения, третий ком мутатор 38, H H $0p MFILL HOIIII k>I II выход 39 блока 32 оперативной II Ix!ÿTH.

Формирователь 25 считывания может быть выполнен 1!3 элементе И, если блок 32 оперативной II3«!51TH управляется нулевым логичсским ciHk!;>л!> 3 по входу 35 выборки, и на элементе ИЛИ, если — единичным.

ВлoK оliерят I!Iíîй Ilямяти дол)KåH имcTü быстродействие при обря!ненни в два раза выIIIC. 1см KOIITp0,;IHð "емь)и 0;IОК 1 посТ05пl)1ОЙ памяти.

В KB 1сствс с!)ОрмнрОватсля 4 KokITpo.3! I>ных чисел можно использовать сумматор, сумматор с различными обратными связями, параллельный сигнатурный анализатор и т. и.

Устройство работает следующим образом.

Подготовительный режим. В подоготовительном режиме во все ячейки блока 32 оперативной памяти записываются единицы признак отсутствия обращения к данной ячейке. !для этого коммутатор 38 иереключают ня прием 3,!LðåcoB от первого счетчика 17, коммутатор 18 переводят в режим прис 13 импульсов обращения от генератора 16. Второй коммутатор 30 переводят в верхнс.с (Ho фиг.2) IIO,!ожение, что обеспечивает подачу на входы генератора 16 и

1О

55 элемент ИЛИ 26 разрс шяк)щего потенциала от первого источника 36 напряжения и запирающего потенциа i;1 на вход элемента И

27 от второго источника 37 напряжения. Б результате этих переключений i;3 вход 33 о!1еративного блока 32 оперативной памяти поступает логическая единица на запись, а на вход 31 — — логический ноль, ознячяк)щий режим записи. Генератор 16 вырабатывает импульсы с определенной частотой, которые через коммута fop 18, Одновибратор

21, формирователь 25 считывания iioc-упают на вход 35 разрешения выборки оперативного блока 32 оперативной памяти. Кроме того, 0НН поступают и на вход счетчика 17, вследствие чего он последовательно меняет свое состояние, «пробегая» тем самым всю возможнУк, последовательность а.сРесов, iinступающих через ком 1уг;пс>р 38 ня BTpccHI I;входы 34 олокя 32 оперативной пямят,;.

Указанные действия приводHT Toму, что по всем адресам блока 3>2 о!!сративной !>ямяти будут записаны един>и!1!. Форxlировягl f!ü 4 контрольных чисел Обнуляетс я.

По окончании подготовительного режима второй коммутатор 30 I!BpeBOд5)г н H!«I«ICC (на фиг.2) положение. в результате чсгс> работа генератора 6 блокируется, на вход элемента ИЛ И 26 lioc гу и яс г . 10! и ч се кl>и 110 l L>, а на вход элемента И 27 — !0!.è÷åñêHå единицы. Коммутатор 38 перевод!к! на режим приема адресов из l3llci!!1.:егс> устро!1ства но дополнительной груп )с- 11 вxu!OB. Кс>мх)утатор 18 переключа)от !гя режим:>рисxld liмпульсов обращения f*,ыборки Ог входя Fj HB вход блока 19 сравнения по группе 14 входов подают ко Lhl 3,.)pccOB Hp!IIHx )язр5! !Ов, которые определяк>т 51;!рос моду.!5: !б!OK3) памяти, для KOTорс>г0 бу,ц !.;1одс ч!<ть:,ll:- 1ься контрольное число. Ня вход б.!ОKd 29 с>)с>внсния 110 группе 15 входов пода!О.I ко.с, Означающий количество п>сел,,хряняп н хсн в контролируемом модулс, ч го !>ес>1>хс.. !имо для определения конца работь. !!0 к,>kil 90.1K) выбранного модуля на, 5гги

Режим контроля. Ь IlpOH!Eссс работы к блоку 1 памяти по !ру!ше i2 вхоTOB постхпают адреса запрашиваемых чисел, 3;10 вхс>ду 6 — сил)ал !)op3l:LcIIHl!. Быбирас-;.:ые i:)ела поступают ня выход блока, гамHT!, Коды адресов поступают.-aKHKB и б.:o к управления суммирование м. Их)!!х>ль«ь! выборки 10 входу 6 постуii3Kт также в блок 2.

Если коды старших адресов, I.осту пclк>LLiHx Il0 группам 14 и 11 входов, совildi3IoT, что означает оора!цение K ко!.;-„Олир f слому модул!о памяги, то б.!Ок !9, рявщ ия вырабатывает разрсшя кнций f отс III!H!)л. поступаю!ций íà D-вход три. гер", 20. (Ь1пульс разрешения выоорки по вход, 6 ноступает через коммутатор 8 !!à вход Oдновибратора 21, кото >ый формируе.- импульс нужной д>)ителы!Ос)и д.151 обряпсени51 к блоку 32 Оперативной I амяl li, >1Ост> пя!01ци)! чс.рез формирователь 25 ня в:.Од 35 ko;.ы

1278982

ФОР.)Ц>1 а иЗООРЕтЕН<ЧЯ адресов младших разрядов B это время через коммутатор 38 поступают на вход 34. г10 входу 31 установлен режим считывания из блока 32 памяти. В результате этого по запрашиваемому адресу выбирается информация (единица или ноль). Возможны два продолжения работы блока 2:

1. Если считывается единица — признак первого обрац?ения по данному адресу, она поступает на С-вход триггера 20 и по разрешающему потенциалу на его входе (D) переводит его в единичное состояние. На выходе триггера 20 (и?!версном) появится логический ноль, который через элемент

И 27 установит ре)ким записи по входу 31 и запись логического ноля по входу 33 через элемент И.?1И 26. Однов1збратор 24 выр!оатывает rln псредне ?у (»ронтх переключения три г! Сры 20 H %1!I > . 1 I><-, ко О,) ь! и i!ocT 5 ï II< т одновибратор 22 и формиp0;!a-ель 25 на вход 35 блока 32. Это приводи", к повтор! ому обращению по дынному адресу, ио уже в режиме записи ноля. Че<)e 3 одновибра rnp 23 и.;1

2. Если считывается ноль — — приз!1ык повтор ого o()pa!lie!!H51 !0 данному адресу, то триггер 20 не c1) li)ar:»паст, ед!шица г> счетчик 28 пс до!)ы?!ляется, считываемое число через комму!àTOð 3 не поступает в фор:ирователь 4 Ho!1трол»ных чисел.

УстpoHcT!30 по 3во, Iяст таким Оорызо. 1 обеспечить oднокргп ое суммирование всех !исе;! даж(l!1)li и!10гохрытном и непостоянH()ì по частоте коли IccTBc обра?цений к отдельным словам.,1ля Определения конца проверки данного модуля необходи lo испо,1ьзовать блок 29 сравнения. В результате контроля в счет !ике 28 подсчитывается количество обра1цении, которое сравнивается с числом, IIOcT>!IIBIo!HHvi 110 груllr!F 15 входов, и в момент сравнения вырабатывается признак сравнения, который по выход; 9 поступает ны вход блока 5 сры »Iения, и la!1 1роизво?!Ится сравнение полученного контрольног0 :ис,1а с эталонным, поступы!оп.им по группе 13 входов. Приз??ык сравнения или несравнеиия вырабатываетс5! Иа вы. оде 7 устройства.,) ст )ovicT!30,?, я Обl>ы руже?! ия 01 1?<Оэок в блоках памя(и !!рог?)ымм, содержащее Олок памяти программ, группа адресных входов

КОТОРОГО ЯВ(1Я("l" H ПЕРВОЙ I)3, Ili!0)I BX!)1<)B устройства, управляю(пий вход coc;!flic:. с

>!Прав.!я!Оп ?иxI B xo;!Ox! Олокы >> и р!)влепи я "> u elèðÎâûíèåì и явля(. ся упрывляюlцим входОм устройства, формировытел» контрольным 1и15

55 сел. группа информационных выходов которого соединена с первой группой информационных входов блока сравнения, управляющий вход которого соединен с управляк);цHxl выходом блока управления суммированием, а вторая группа информационных Входов и выход блока сравнения являются соответственно второй группой входов устройства и выходом устройства, отличающ(>еся тем, что, с целью повышения точности контроля, оно содержит коммутатор, группы информационных входов которого соединены с группой информационных выходов блока памяти программ. управляющий вход — с дополнительным управляющим выходом блока управления суммированием, а группа информационных выходов коммутатора соединена с группой и?3(Ьормационных входов формирователя контрольных чисел, при этом группы адресных входов блока памяти программ соединена (первой дополнительной группой входов блока управления c óx!x!èpol)B!!Hex!, вторая и третья дополнительные группы Вх0;;оВ которого являются соответственно трет»ей и четвертой группами входов устройства.

2. Устройство пo п. 1, отличающееся тем, то блок управления суммированием содержит коммутаторы, элементы И и ИЛИ, D òðèããåð, блоки сравнения, одновибраторы. блок оперативной памяти, счетчики, источник напряжения и ге1!ерытор, выход которого соединен со входом первого счетчика и II(>pвым входом первого коммутаторы, второй вход которого является управляющим Bxo;!Ox! блока управления суммированим,,«3»!ход соединен через первый одновибратор с первым входом формирователя обрыщсllHH, в»вход которого соединен со входом разр(н10ния выборки блока оперативной памяти, ы второй вход — — с выходом второго одновибратора и входом третьего одновибратора, причех! выход третьего одновибраторы является дополнитеьным управляюц)им !3»!xu;IOv блока управления суммированием и соединен с R-входом D-триггера, D-вход которого cîcдипен с выходом первого блока сравнения.

С-!3x01? — c информ ыцHoHH»IM B»lxo, 30)

И, а через четвертый одновибратор — co входом второго одновибрыторы и входом второго счетчика, группа информационных ьыходов которого подключена к первой грхппе входов второго блока сравнения, втор;15! п)уппа входов которого являетея второй дополнительной группой входов блока уllpoB,l(Hèÿ суммированием, а выход второго блокы сравнения является управляк)!ц?1)3 выходом блока управления суммированием, при этом первый и второй источники напряжения c00— динены соответственно с группой первы, и вторых входов второго коммутаторы, первый и второй выхо;?ы которого соединены соответственно с вторыми входами элементы И

1278982

ПХ;у=

Со>гтг>ни г лв Г. Ми и>славский

Редактор В. !анко Тсхрсд И. Е!ерсс Корректс>р Сх Луговая

Заказ (>847,>5>4 ираки»45 Подписное

ВНИИПИ Государствсииг>г:> комигета СССР но делам изобретений и открытий! !3035, Москва, Ж вЂ” 35. Раушскав наб., д. 4/5

Филиал !Пг!П «Патент», г. У>к ород, ул. Проектная, 4 и элемента ИЛИ, выходы которых соединены соответственно со входами «Запись-считывание» и «Запись» кода числа блока оперативной памяти, группа а !ресных входов которого соединена с выходом третьего коммутатора, первая группа вхо !ов которого соединена с ьыходам и третьего коммутатора, первая группа входов которого соединена с группой информационных выходов первого > !/ к >т >

+ счетчика, и вторая группа входов является первой дополнительно 4 группой входов блока управления суммированием и соединена с первой группой входов первого блока сравнения, вторая группа входов которого является третьей дополнительной группой входов блока управ IcIIHF. суммированием, при этом вход генератора соединен со вторым входом элемента ИЛИ.