Аналого-цифровое множительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики. Целью и брете-. НИН является повышение точности умножения . Поставленная цель достигается за счет изменения формы представления дискретной части одного из сомножителей вместо прямого кода со знаком, использовавшегося в известном устройстве, смещенным двоичным кодом, что позволило исключить источники погрешностей, связанные с обеспечением четырехквадрантнрго режима работы - инверторы и аналоговые коммутаторы из сигнальных цепей У ;тройства. Основные конструктивные отличия состоят во введении в устройство первого, второго и третьего источников опорного напряжения и блока управления умножением на логический нуль, содержащего два элемента ШШ-НЕ и элемент И-НЕ, а также в наличии новых связей между элементами и блока ми, чем и обеспечивается достижение поставленной цели. 1 ил. i (Л С

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5114 G 06 G 7 16

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИП:

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ЬР (21) 3818899/24-24 (22) 30.11.84 (46) 30.12. 86.. Бюл. М - 48 (71) Львовский ордена Ленина политехнический институт им. Ленинского . комсомола (72) Ю. Н. Бобков, И. P. Соболевский и А. А. Третилов (53) 681 ° 3(088.8) (56) Математическое моделирование и теория электрических цепей, вып.

II. — Киев: Наукова думка, 1973, с. 157.

Авторское свидетельство СССР

Н 1215122, кл. G 06 G 7/16,. 1984. (54) АНАЛОГО-ЦИФРОВОЕ МНОЖИТЕЛЬНОЕ

УСТРОЙСТВО (57) Изобретение относится к аналоговой вычислительной технике и может быть использовано в системах и устройствах автоматики. Целью из1ббрете-.,. SU„„1280400 А 1 ния является повышение точности умножения. Поставленная цель достигается за счет изменения формы представления дискретной части одного из сомножителей вместо прямого кода со знаком, использовавшегося в известном устройстве, смещенным двоичным кодом что позволило исключить источники погрешностей, связанные с обеспечением четырехквадрантного режима работы — инверторы и аналоговые коммутаторы из сигнальных цепей у< тройства. Основные конструктивные отличия состоят во введении в устройство первого, второго и третьего источников опорного напряжения и блока управления умножением на логический нуль, содержащего два элемента ИЛИ-НЕ и элемент И-НЕ, а также в наличии новых связей между элементами и блока1 ми, чем и обеспечивается достижение поставленной цели. 1 ил.

1 2 80400

Изобретение относится к аналоговой вычислительной технике и может быть использовано в устройствах и системах автоматики.

Цель изобретения — повышение точности умножения.

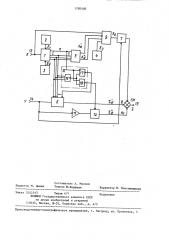

На чертеже приведена схема аналого-цифрового множительного устройства.

Множительное устройство содержит аналого-цифровой преобразователь (АЦП) 1, первый 2, второй 3 и третий

4 источники опорного напряжения (ИОН), цифроаналоговый преобразователь (ЦАП)

5, умножающий цифроаналоговый преобразователь (УЦАП) б, аналоговый перемножитель (АП) 7, сумматор 8, блок суммирования - вычитания (БСВ)

9, блок управнения (БУ) 10 умножением,на логический нуль, инвертор 11, 1 ключ 12, первый 13 и второй 14 вхо" ,ды и выход 15,устройства. Кроме того, БУ 10 содержит элементы ИЛИ-НЕ 16 и 17 и элемент И-НЕ 18. Перечислен25 ные элементы и блоки соединены по приведенной схеме.

Аналого-цифровое множительное устройство работает следующим образом.

Первый знакопеременный сомножитель Х поступает с входа 13 устройства на информационный вход АЦП 1.

К опорным входам АЦП 1 приложены опорные напряжения Е =Е Е =-Е ИОН г

35 (l ) 2 е Кап К к 9 (8)

4р где К„„ — масштабный коэффициент АП 7. п= (х+2 й+ ак), (2)

Е где d= --,- " интервал квантования; ь к — погрешность квантоваI ния, приведенная к вхо-5р ду АЦП

Кодовый сигнал и поступает на соответствукнцие разрядные входы ЦАП 5, в котором осуществляется преобразование кода п в аналоговую форму, при- 55 чем на основном выходе ЦАП 5 образуется дискретная часть х сомножителя Х, а на дополняющем выходе — ee дополнение до максимального сигнала н-i

nk2 (9)

n=2

2 и 3.

2 -2

E=2 1Х макс 9

rpe X — максимальное значение сомножителя Х9

N — - число разрядов АЦП 1.

Результат аналого-цифрового преобразования представлен параллельным смещенным двоичным кодом п: х, соответствующего значению маис 9

9i входного кода n=2 -1. Таким образом: х =k и= P"(х+2 d+ ь ); (Э) й-1 х" =х -k и=-- -"- (2 -1)dЯ Й макс иап

-х- к) (4)

Сигналы х и x d поступают соот" ветственно на инвертирующий и неинвертирующий входы блока 9, к двум другим неинвертирующим входам которого приложены сомножитель Х и смещающее напряжение Е источника 4. На выходе блока 9 образуется остаток х;: х,=k(x+x -х9+Е ). (5) Подставив в последнее соотношение выражения (3) и (4) и преобразовав, получим х =k (1-2- а"-х-2- -"-як+К -К . (6)

<1 ь ч

Й

Положив Е. =К =- получим акоп 29 х,. =-К,9 где К вЂ” масштабнйй коэффициент результата суммирования — вычитания, значение которого (с целью максимального снижения влияния погрешности

АП 7) выбирается близким к значению числа 2 -l уровней квантования АЦП 1.

Поступая далее на один их входов

АП 7, остаток х, умножается на второй сомножитель У, который подается с входа 14 устройства.

Результат перемножения равен

Одновременно дискретная часть сомножителя Х в форме двоичного смещенного кода и подается на соответствующие разрядные входы УПАП 6, причем

И-1 младших разрядов кода п поступает на УЦАП 6 непосредственно, а старший (знаковый) разряд — через

БУ 10. Логический сигнал на выходе элемента ИЛИ-НЕ 17 БУ 10, управляющий старшим разрядом УЦАП б, равен нулю для и. 2 и единице для п>2

ы-т 99-9

Соответственно сигнал на выходе УЦАП

6 определяется соотношением

К nY=--""-"- -(х+2 6+ а ) Y уцап 9

z О, 1280400

=Y п12м!. (10) t5

1

\ II о Д Д ап

+ чцаа (,(, (К я чцаа

О, Аналого-цифровое множительное устройство, содержащее аналого-циф-. 45 ровой преобразователь, цифроаналоговый преобразователь, умножающий цифроаналоговый преобразователь, аналоговый перемножитель, блок суммирования-вычитания, ключ, инвертор и 50 сумматор, выход которого является выходом устройства, а первый и второй входы соединены соответственно с вы ходом умножающего цифроаналогового преобразователя и с выходом аналогового перемножителя, подключенного одним входом к одному из информационДля исключения составляющей смещения,в результате цифроаналогового умножения используется дополнительно введенная цепь инвертор 11 — ключ 12.

Управляющий вход последнего подклю- 5 чен к выходу элемента HE БУ 10, на котором формируется логический сигN-1 нал, равный нулю, при n=2 и единице - во всех остальных случаях. Сигнал на выходе ключа 12 10

Результаты аналогового Z и дискретно-аналогового Zd умножения, а также компенсирующий сигнал Z посс1 тупают на входы сумматора 8 с коэффициентами суммирования 1/К; 1 и К„. соответственно.

На выходе сумматора 8 образуется результат перемножения Е:

-К )Y+--""--"ь„У, пФ2.

Кчца 1ч-1 25

Г"-- ° ° „„;

n = 2, Заметим, что значение п=2 сост- З0 й-1 ветствует значениям сомножителя X u результата Z равным нулю. Поэтому

z=-"- ху+(к„„г -к )Y+(— " - "—

-К,„)а„У, (12) З5

Уравняв масштабные коэффициенты умножения дискретной и аналоговой частей К „ /d=K =.К 1 и положив

1Ч-1

К an 2 -К, DQJI+vHM окончательно

Z=K,XY. 40

Формула изобретения ных входов устройства и к аналоговому входу умножающего цифроаналогового преобразователя, а другим входомк выходу блока суммирования-вычитания, цифровые входы младших разрядов умножающего цифроаналогового преобразователя подключены к соответствующим разрядным входам цифроаналогового преобразователя и к соответствующим разрядным выходам аналогоцифрового преобразователя, вход которого является другим информационным входом устройства, о т л и ч а— ю щ е е с я тем, что, с целью повышения точности, оно содержит первый, второй и третий источники опорного напряжения и блок управления умноже нием на логический нуль, выполненный в .виде двух элементов ИЛИ-НЕ и элемента И-НЕ, выход которого подключен к управляющему входу ключа, а два входа соединены соответственно с выходом первого и инвертирующим входом второго элементов ИЛИ-НЕ, группа входов первого элемента ИЛИ-НЕ блока управления умножения на логический нуль подключена к соответствующим выходам младших разрядов аналого-цифрового преобразователя, выход старшего разряда которого соединен с входом старшего разряда цифроаналогового преобразователя и с инвертирующим входом второго элемента ИЛИ вЂ , подключенного неинвертирующим входом и выходом соответственно к выходу первого элемента ИЛИ-НЕ блока управления умножением на логический нуль и к цифровому входу старшего разряда умножающего цифроаналогового преобразователя, два опорных входа аналого-цифрового преобразователя подклю" чены к выходам соответственно первого и второго источников опорных напряжений, три неинвертирующих входа блока сложения-вычитания подсоединены соответственно к информационному входу аналого-цифрового преобразователя, дополняющему выходу цифроаналогового преобразователя и к выходу гретьего источника опорного напряжения, а его инвертирующий вход соединен с основным выходом цифроаналогового преобразователя, третий вход сумматора подключен через ключ к выходу инвертора, вход которого соединен с аналоговым входом умножающего цифроаналогового преобразователя.! 280400

Составитель А. Маслов

Редактор M. Дылын Техред М.Ходанич

Корректор M. Максимишинец

Заказ 7052/43 Тираж 671

ВНИИПИ Государственного комитета СССР па делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, /