Аналоговое множительное устройство

Иллюстрации

Показать всеРеферат

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности работы. Аналоговое множительное устройство содержит первый, второй , третий и четвертый элементы с управляемой проводимостью, вьшолненные на полевых транзисторах, операционный усилитель, к инвертирующему входу операционного усилителя подключены стоки первого и третьего полевых транзисторов и первый вывод масштабного резистора, к неинвертирующему входу операционного усилителя подключены стоки второго и четвертого полевых транзисторов и первый вывод резистора смещения, выходы первого и второго сумматоров соединены с попарно соединенными затворами первого и четвертого и второго и третьего полевых транзисторов соответственно , к первым входам первого и второго сумматоров подключен выход источника напряжения смещения, второй вход второго сумматора является входом первого сигнала-сомножителя устройства и соединен с входом фазоинвертора, выход которого подключен к второму входу первого сумматора, истоки третьего и четвертого полевых транзисторов соединены и являются входом второго сигнала-сомножителя устройства, истоки первого и второго полевых транзисторов и второй вывод резистора смещения подключены к шине нулевого потенциала, второй вывод масштабного резистора соединен с выходом операционного усилителя, который является выходом устройства. Работа устройства основана на регулировке проводимости управляемых полевых транзисторов первым сигналомсомножителем в тракте передачи сигнала второго сигнала-сомножителя. 1 ил. с е (Л кэ 00

СОЮЗ СОВЕТСНИХ

СО1.1ИАЛИСТИЧЕСНИХ

РЕСПУБЛИК (so 4 С 06 С 7/16

ОПИСАНИЕ ИЗОБРЕТЕНИЯ, 3

« /

«« «

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ того полевых транзисторов и первый вывод резистора смещения, выходы первого и второго сумматоров соединены с попарно соединенными затворами первого и четвертого и второго и третьего полевых транзисторов соответственно, к первым входам первого и второго сумматоров подключен выход источника напряжения смещения, второй вход второго сумматора является входом первого сигнала-сомножителя устройства и соединен с входом фазоин— вертора, выход которого подключен к второму входу первого сумматора, истоки третьего и четвертого полевых транзисторов соединены и являются входом второго сигнала-сомножителя устройства, истоки первого и второго полевых транзисторов и второй вывод резистора смещения подключены к шине нулевого потенциала, второй вывод масштабного резистора соединен с выходом операционного усилителя, который является выходом устройства. Работа устройства основана на регулировке проводимости управляемых полевых транзисторов первым сигналомсомножителем в тракте передачи сигнала второго сигнала-сомножителя. 1 ил.

СР

4:ь

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3946595/24-24 (22) 27.08.85 (46) 30.12.86. Бюл. У 48 (72) А.А.Киселев (53) 681.335(088 ° 8) (56) Патент Франции Ф 2.386082,, кл. G 06 G 7/16, опублик. 1978.

Авторское свидетельство СССР

N- 661561, кл. С 06 С 7/16, 1977. (54) АНАЛОГОВОЕ МНОЖИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение относится к элек— трическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах. Целью изобретения является повышение точности работы. Аналоговое множительное устройство содержит первый, второй, третий и четвертый элементы с управляемой проводимостью, выполненные на полевых транзисторах, операционный усилитель, к инвертирующему входу операционного усилителя подключены стоки первого и третьего полевых транзисторов и первый вывод масштабного резистора, к неинвертирующему входу операционного усилителя подключены стоки второго и четверÄÄSUÄÄ 1280401 А 1

1280401

11 п " Йи + E hi.Их2Яа (Язу«+ /egg+.gg) где напряжение второго сигнала-сомножителя на входе 14; 40 проводимость масштабного резистора 5; проводимость резистора смещения 11; 45 проводимости каналов сток — исток © ам

U — — U U (2) 2Ь

Ьь,1(g 1 2 У

Изобретение относится к электрическим вычислительным устройствам и может быть использовано в аналоговых вычислительных машинах.

Цель изобретения — повышение точ- 5 ности работы.

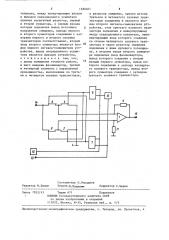

На чертеже изображена функциональная схема аналогового множительного устройства.

Схема содержит операционный усили10 тель 1, первый и второй полевые транзисторы 2 и 3, шину 4 нулевого потенциала, масштабный резистор 5, первый и второй сумматоры 6 и 7, третий и четвертый полевые транзисторы 8 и 9, фазоинвертор 10, резистор 11 смещения, источник 12 напряжения смещения, входы 13 и 14 первого и второго сигналов-сомножителей, выход 15.

Полевые транзисторы выполняют в устройстве функцию элементов с управляемой проводимостью.

Аналоговое множительное устройство работает следующим образом.

На затворы первого, второго, третьего и четвертого полевых транзисто-! первого, второго, третьего и четвертого полевых транзис- 50 торов 2,3,8 и 9 соответственно.

Если параметры первого, второго, третьего и четвертого полевых транзисторов 2,3,8 и 9 одинаковы, то вы- 55 ражение 1 примет вид ров 2,3,8 и 9 подается линейная комбинация первого сигнала-сомножителя с входа 13 и напряжения смещения от источника 12 напряжения смещения через первый и второй сумматоры 6 и 7 и фаэоинвертор 10. С входа 14 напряжения второго сигнала-сомножителя подается на истоки третьего и четвертого полевых транзисторов 8 и 9, образующих совместно с первым и вторым полевыми транзисторами 2 и 3 управляемые делители напряжения. Напряжения со стоков первого и второго полевых транзисторов 2 и 3 подаются на инвертирующий и неинвертирующий входы операционного усилителя 1. Величины этих напряжений зависят как от величины второго сигнала-сомножителя с входа 14, так и от соотношения проводимостей каналов сток — исток первого, второго, третьего и четвертого полевых транзисторов 2,3,8 и 9.

Проводимости каналов сток — исток в свою очередь определяются величиной первого сигнала-сомножителя с входа

13. В общем виде напряжение на выходе 15 равно где U — напряжение первого сигнала1 сомножителя с входа 13;

Ь вЂ” коэффициент, учитывающий параметры полевых транзисторов.

Из выражения (2) следует, что оно не зависит от напряжения смещения, что повышает точность работы устройства.

Формула изобретения

Аналоговое множительное устройство, содержащее первый и второй элементы с управляемой проводимостью, выполненные на первом и втором полевых транзисторах, операционный усилитель, инвертирующий и неинвертирующий входы которого подключены к стокам первого и второго полевых транзисторов соответственно, истоки которых соединены с шиной нулевого по1280401

Составитепь 0.0траднов

ТехРед М.Ходанич Корректор С.Черни

Редактор M.Äûëûí

Заказ 7052/43 (Тираж 67) Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Произвопственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 тенциала, между инвертирующим входом и выходом операционного усилителя включен масштабный резистор, первый и второй сумматоры, к первым входам которых подключен выход источника 5 напряжения смещения, выходы первого и второго сумматоров соединены с затворами первого и второго полевых транзисторов соответственно, второй вход второго сумматора является вхо- 1О дом первого сигнала-сомножителя устройства, выход операционного усилителя является выходом устройства, о т л и ч а ю щ е е с я тем, что, с целью повышения точности работы, в него введены фазоинвертор, третий и четвертый элементы с управляемой проводимостью, выполненные на третьем и четвертом полевых транзисторах, и резистор смещения, причем истоки третьего и четвертого полевых транзисторов соединены и являются входом второго сигнала-сомножителя устройства, сток третьего полевого транзистора подключен к инвертирующему входу операционного усилителя, неинвертирующий вход которого соединен со стоком четвертого полевого транзистора и через резистор смещения подключен к шине нулевого потенциала, к второму входу второго сумматора подключен вход фаэоинвертора, выход которого соединен с вторым входом первого сумматора, выход которого подключен к затвору четвертого полевого транзистора, выход второго сумматора соединен с затвором третьего полевого транзистора.