Модуль матричного коммутатора

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может найти применение при построении коммутационных систем многопроцессорных вычислительных структур, например систолических или матричных процессоров. Цель изобретения - расширение функциональных возможностей за счет возможности передачи информации по четьфем направлениям.Программируемый модуль матричного коммутатора содержит блок памяти коммутаций, регистр кода коммутации, генератор тактовых импульсов, четыре регистра приема, четьфе мультиплексора выдачи информации , одновибратор по фронту импульса и элемент задержки. При задании определенного кода коммутации информация с одного из четьфех входов передается на один из четырех выходов, модуля. 2 ил. (Л ю 00 о СП ф Од

СОЮЗ СОВЕТСНИХ соцИАлистичесних

РЕСПУБЛИН

„„SU„, 1280596 А1 (51)4 G 06 F 1/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3959078/24-.24 (22) 26.09.85 (46) 30.12.86..Бюл. У 48 (71) Ленинградский ордена Ленина политехнический институт им. М.И.Калинина (72) В,Н. Самошин (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 1121778, кл. G 06 F 7/00, 1983.

Авторское свидетельство СССР

N 1177804, кл. С 06 F 1/00, 1984. (54) МОДУЛЬ МАТРИЧНОГО КОММУТАТОРА (57) Изобретение относится к вычислительной технике и может найти применение при построении коммутационных систем многопроцессорных вычислительных структур, например систолических или матричных процессоров.

Цель изобретения — расширение функциональных возможностей sa счет возможности передачи информации по четырем направлениям. Программируемый модуль матричного коммутатора содержит блок памяти коммутаций, регистр кода коммутации, генератор тактовых импульсов, четыре регистра приема, четыре мультиплексора выдачи информации, одновибратор по фронту импульса и элемент задержки. При задании определенного кода коммутации информация с одного иэ четырех входов передается на один из четырех выходов. модуля. 2 ил.

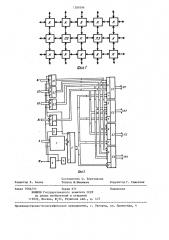

Регистр 2 кода коммутации предназначен для хранения кода коммутации алгоритма, выполнение которого происходит в вычислительном массиве, Группа из четырех регистров 3.13.4 приема служит для приема информации с четырех соответствующих сторон модуля.

ГТИ 4 служит для выдачи последовательности импульсов, которые син-. хронизируют работу модуля, Группа иэ четырех мультиплексоров

5.1-5.4 выдачи предназначена для выдачи информации с регистров 3 ° 1-3.4 по соответствующим направлениям согласно коду коммутации алгоритма, на который настроен вычислительный массив в данный момент времени.

50

128059

Изобретение относится к ьычислительной технике и может быть использовано при построении коммутационных систем многопроцессорнык вычислительных структур, например систолических 5 о или матричных процессоров.

Цель изобретения — расширение функциональных возможностей за счет возможности передачи информации по четырем направлениям.

На фиг. 1 изображена часть вычислительного регулярного массива с коммутационным полем, на фиг. 2 — функциональная схема модуля матричного коммутатора.

Вычислительный массив с коммутационным полем состоит из процессорных элементов (ПЭ) и предлагаемых программируемых модулей матричного коммутатора (К) (фиг.1).

Программируемый модуль матричного коммутатора (фиг.2) содержит блок

1 памяти коммутаций, регистр 2 кода коммутации, группу из четырех регистров

3,1-3.4 приема, генератор 4 тактовых импульсов (ГТИ), группу иэ четырех мультиплексоров 5.1-5.4 выдачи информации, одновибратор 6 по фронту импульса, элемент 7 задержки. На фиг. 2 также изображены первых четыре информационных входа 8.1-8.4 модуля, пятый информационный вход 9 модуля, вход 10 пуска модуля, информационные выходы 11,1-11.4 модуля.

Блок 1 памяти коммутаций служит для хранения кодов коммутаций, соответствующих различным алгоритмам, на которые ориентирован вычислительный массив.

6 2

Одновибратор 6 по фронту импульса предназначен для обнуления всех регистров модуля перед началом его работы.

Элемент 7 задержки служит для задержки импульса синхронизации записи в регистр 2 кода коммутации на время переходных процессов в блоке 1 памяти.

Предлагаемый модуль работает следующим образом.

Работа программируемого модуля матричного коммутатора инициируется установкой единичного уровня сигнала на входе 10 пуска модуля, который запускает ГТИ 4, а через одновибратор 6 обнуляет все регистры модуля. На входе 9 модуля устанавливается код коммутации, который сохраняет свое значение неизменным до следующего перепрограммирования коммутации в массиве. Тактовые импульсы, поступая на вход считывания блока 1 памяти коммутаций, а через элемент 7 задержки — на синхровход записи регистра 2 кода коммутации, производят запись в этот регистр кода коммутации, который определен выполняющимся алгоритмом. Код коммутации с выхода регистра 2 кода коммутации, определенным образом поступая на управляющие входы мультиплексоров 5.1-5.4, задает их работу по определенным входам и информация на выходы 11.1-11.4 модуля поступает с выходов определеннык регистров 3.1-3.4 по определенному закону коммутации, который задается алгоритмом обработки информации, Таким образом, по каждому тактовому импульсу с ГТИ 4 происходит прием информации в модуль на регистры

3.1-3 ° 4 и его настройка на дальнейшую передачу информации через мультиплексоры 5.1-5.4.

Если в ходе решения задачи необходимо произвести перекоммутацию связей между процессорными элементами в массиве, на входе 9 программируемых модулей матричного коммутатора устанавливается необходимый микрокод алгоритма и по следующему тактовому импульсу с ГТИ 4 происходит перепрограммирование структуры пространственных связей между процессорными элементами массива.

Далее функционирование устройства протекает аналогично рассмотренному.

Окончание работы программируемого модуля матричного коммутатора происхо1280596 дит по установке на входе 10 пуска модуля нулевого сигнала, который запрещает работу ГТИ 4 и всего устройства в целом.

Таким образом, программируя опре- 5 деленным образом блоки памяти коммутаций во всех модулях матричного коммутатора, с помощью подачи одного микрокода на все модули структуры можно производить перепрограммирование массива процессорных элементов на выполнение другого алгоритма, используя значительно меньшее число внешних выводов, Предлагаемый программируемый модуль матричного коммутатора может найти широкое применение в однородных коммутационных регистровых структурах при создании параллельных процессоров цифровой обработки сигналов. 2О

Формула изобретения

Модуль матричного коммутатора, со25 держащий первый и второй регистры, первый и второй мультиплексоры и блок управления, содержащий регистр кода коммутации, причем первый и второй информационные входы модуля соединены с информационными входами первого и второго регистров, выходы которых соединены с первым и вторым информационными входами первого и второго мультиплексоров, управляющие входы Ç5

Ъ которых соединены с выходом блока управления, адресные входы которого соединены с третьим информационным входом модуля, первый и второй информационные выходы которого соединены с выходами первого и второго мультиплексоров, о т л и ч а ю щ и йс я тем, что, с целью расширения функциональных возможностей за счет возможности передачи информации по четырем направлениям, модуль содержит третий и четвертый регистры, третий и четвертый мультиплексоры, а в блок управления введены генератор тактовых импульсов, элемент задержки, одновибратор и блок памяти коммутаций, причем четвертый и пятый информационные входы модуля соединены с информационными входами третьего и четвертого регистров, выход первого регистра соединен с первым информационным входом третьего мультиплексора, выход которого соединен с третьим информационным выходом моду-. ля, выход второго регистра соединен с первым информационным входом четвертого мультиплексора, второй и третий информационные входы .которого соединены с вторым и третьим информационными входами третьего мультиплексора и выходами третьего и четвертого регистров соответственно, третьи информационные входы первого и второго мультиплексоров соединены с выходом третьего и четвертого регистров соответственно, управляющие входы третьего и четвертого мультиплексоров соединены с выходом блока управления, выход четвертого мультиплексора соединен с четвертым информационным выходом модуля, вход запуска которого соединен с входом генератора тактовых импульсов, выход которого соединен с входом элемента задержки, выход которого соединен с синхровходом записи регистра кода коммутации, вход сброса которого соединен с входами сброса первого,второго, третьего, четвертого регистров и выходом одновибратора, вход которого соединен с вхбдом запуска модуля, входы записи первого, второго, третьего, четвертого регистров соединены с выходом генератора тактовых импульсов и синхровходом считывания блока памяти коммутаций, выход которого соединен с информационным входом регистра кода коммутации.

1280596

Составитель О. Березикова

Техред И.Попович

Редактор Е. Копча

Корректор Г. Решетник

Заказ 7066/53 Тираж 671

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4