Устройство для вычисления логарифмической функции

Иллюстрации

Показать всеРеферат

Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах автоматического управления и контроля, а также в устройствах аппаратной реализации средств математического обеспечения ЭВМ. Целью изобретения является повышение точности вычисления логарифмической функции. В состав устройства входят три счетчика 1-3, два импульсных сумматора 7,11, два накапливающих сумматора 4,5, схема 6 сравнения кодов и импульсный вычитатель 15. 4 ил.. I N3 00 о О5

СОК)3 COBETCHÈÕ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H A ВТОРСИОМЪ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3941616/24-24 (22) 02.08.85 (46) 30.12.86. Бюл. Р 48 (7l) Львовский ордена Ленина политехнический институт им. Ленинского комсомола (72) К.А.Глущенко, В.Б.Дудыкевич и О.Б.Котыло (53) 681.325(088.8) (56) Авторское свидетельство СССР

N - 1108441, кл. С 06 F 7/556, 1982.

Авторское свидетельство СССР

Н 1043645, кл. С (6 F 7/556, 1982.

„„Я0„„1280617 A 3 (5р 4 G 06 F 7/556, дг,-, (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИМКЧЕСКОЙ ФУНКЦИИ (57) Изобретение относится к области автоматики и вычислительной техники и может быть использовано в системах автоматического управления и контроля, а также в устройствах аппаратной реализации средств математического обеспечения 3ВМ. Целью изобретения является повьппение точности вычисления логарифмической функции. В состав устройства входят три счетчика 1-3, два импульсных сумматора 7, l1, два накапливающих сумматора 4,5, схема 6 сравнения кодов и импульсный вычитатель 15. 4 ил.

О (О

1 12806

Изобретение относится к автоматике, вычислительной технике и может быть использовано в системах автоматического управления и контроля, в микропроцессорных системах, а также в устройствах аппаратной реализации средств математического обеспечения ЭБИ.

Цель изобретения — повышение точности вычисления логарифмической Ю функции.

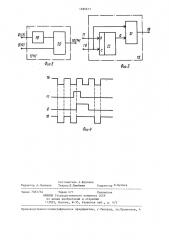

На фиг. 1 приведена структурная схема устройства для вычисления логарифмической функции; на фиг.2 — схема импульсного сумматора; на фиг.3— схема импульсного вычитателя; на фиг.4 — диаграммы, пояСняющие работу устройства.

Устройство для вычисления логариф.мической функции содержит первый, второй и третий счетчики 1,2 и 3, первый и второй накапливающие сумматоры

4 и 5, схему 6 сравнения кодов, пер-. вый импульсный сумматор 7 с входами

8 и 9 и выходом 10, второй импульсный сумматор 11 с входами 12 и 13 и выходом 14, импульсный вычитатель 15 с входами 16 и 17 и выходом 18.Импульсный сумматор содержит (фиг.2) элемент 19 задержки и элемент ЗО

ИЛИ 20.

Импульсный вычитатель содержит (фиг.3) элемент ИЛИ 21 и D-триггер 22.

Устройство работает следующим об разом. 35

Б исходном состоянии счетчики 1,2 и 3 и накапливаюшие сумматоры 4 и 5 находятся в нулевом состоянии. Приращение dx входной импульсной последоват льности х, поступающей на вход рр устройства, вызывает на выходе накап-. ливающего сумматора 4 приращение dy импульсной последовательности у и формирует в счетчике 1 текущее значе- ние числа х. Работа импульсного сум- 45 матора 7 описывается выражением

dz = dx + dy.

Накапливающий сумматор 4 использован в качестве первого управляемого 0 делителя частоты. Входом управляемого делителя частоты является тактовый вход накапливающего сумматора, группой управляющих входов управляемого делителя частоты, на которые подается код, задающий коэффициент деления, является группа информационных входов накапливающего сумматора вместе с установленным в единицу входом переноса из младшего разряда, выходом управляемого делителя частоты служит выход переноса накапливающего сумматора. Работа первого управляемого делителя частоты описывается выражением

2 - х — 1 + 1

dy

2л

dz (2)

Э где и — разрядность группы информационных входов накапливающего сумматора;

dz — приращение входной импульсной последовательности управляемого делителя частоты;

dy — приращение выходной импульсной последовательности управляемого делителя частоты.

Решая совместно (1) и (2) и интегрируя с учетом прецелов интегрирования, получим е/О = 2 4.х/,"у

z - =2 Г х.

П (3) (4) С целью уменьшения погрешности используют схему сравнения кодов, счетчики 2 и 3, накапливающий сумматор 5, импульсный вычитатель 15 и импульсный сумматор t1. Приращение dv импульсной последовательности v, поступающей на вход счетчика 3, вызывает на выходе схемы 6 сравнения кодов приращение

ds импульсной последовательности s.

Накапливающий сумматор 5 использован в качестве второго управляемого дели: теля частоты, работа которого описывается выражением

Р

Ов = ds

1 2h У (5) dv = dz — йз (6) где n — разрядность группы информационных входов накапливающего сумматора 5;

ds - приращение входной импульсной последовательности второго управляемого делителя частоты;

ds — приращение выходной импульс1 ной последовательности второго управляемого делителя частоты;

P — код, который подается на группу информационных входов накапливающего сумматора 5 (значение Р зависит от разрядности устройства)., Работа импульсного вычитателя описывается выражением

3 1280

Разрядность счетчика 3 и схемы 6 сравнения кодов равна n + 1, младший разряд (нулевой разряд) схемы сравнения кодов подключен к нулевому потенциалу, i — и разряд счетчика 1 соединен .5 с i + 1-м разрядом схемы сравнения кодов (i = 0,1,...., ), i-й разряд счетчика 3 соединен с i-м разрядом схемы сравнения кодов (= О, 1,..., n + 1). Управляющие входы счетчика 3 10 при возникновении на выходе схемы сравнения кодов импульса, устанавли — . вают счетчик 3 в состояние равное 2.

Поэтому работа счетчиков 1 и 3 и схемы 6 сравнения кодов описывается вы- 15 ражением

617 входом первого накапливающего сумматора, выход переполнения которого соединен с вторым входом первого импульсного сумматора, вход переноса первого накапливающего сумматора соединен с шиной информационной единицы устройства, выход второго импульсного сумматора соединен со счетным входом второго счетчика, информациойный вход первого накапливающего сумматора соединен с инверсным выходом первого счетчика, прямой выход которого соединен с входом старших разрядов первого информационного входа схемы сравнения, второй информационный вход которой соединен с выходом третьего счетчика, второй вход импульсного вычитателя соединен с выходом переполнения второго накапливающего сумматора, информационный вход которого соединен с установочным входом устройства, выход схемы сравнения соединен с вторым входом второго импульсного сумматора, с установочным входом третьего счетчика, с тактовым входом второго накапливающего сумматора, выход импульсного вычитателя соединен со счетным входом третьего счетчика, младший разряд первого информационного входа схемы сравнения соединен с шиной информационного нуля устройства.

ds = — -- — — dv

2х — 2 (7) 20 лучим

dz --- ds

2п .ds

2х — 2 (8) 2

2"(2. - 2) + P

Решая совместно (5), (6) и (7), по

Работа импульсного сумматора 11 описывается выражением

dr = dz + ds. (10) Решая совместно (9) и (10) получим

dr = dz +

Р

dz. (11) .(2х — 2) + г

2н

Интегрируя (11) с учетом пределов интегрирования, получим текущее значение уточненной логарифмической функции 2 4х в счетчике 2:

2 < х 40 г=2 х+ — — — — — — — . (12)

2х — 2 + ——

2" формула изобретения

Устройство для вычисления логарифмической функции, содержащее первый, второй и третий счетчики, первый и второй импульсный сумматоры, причем первый вход первого импульсного сумматора объединен со счетным входом первого счетчика, о т л и ч а ю щ ее с я тем, что, с целью повышения точности, в него введены первый и второй накапливающие сумматоры, схема сравнения и импульсный вычитатель, причем информационный вход устройства соединен с первым входом первого им- . пульсного сумматора, выход которого соединен с первым входом второго импульсного сумматора, с первым входом импульсного вычитателя и с тактовым

1280617

Составитель А.Шуляпов

Редактор А.Лежнина Техред JI.Îëåéíèê Корректор В.Бутяга

Заказ 7067/54 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Ужгород, ул.Проектная, 4