Устройство для управления памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике, а именно к управляющим устройствам памяти, может быть использовано в системах обработки данных и является усовершенствованием известного устройства для управления памятью по авт.св. № 809182. Цель изобретения - повышение надежности устройства. Устройство содержит блок памяти, блок адреса, блок записи и считывания, блок ввода данных, распределитель управляющих сигналов, счетчик адреса, блок записи адреса, регистр адреса программы, регистр адреса, блок считывания адреса, регистры данных, сумматоры, блоки сразнения и накопитель. В устройстве обеспечивается регистрация в накопителе степени заполнения блока памяти, что обеспечивает полное использование его ресурса. 2 ил. tc QO 14

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (A@4.G 06 F 9/06

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ списочник изоьгятяния к АВТорсНоМУ св детельствм " е.;,„, / (61) 809182 (21) 3919575/24-24 (22) 02,07.85 (46) 30 ° 12.86. Бюл. N - 48 (72) А.М,Корзун, Ю.И.Мосиенко, В.Н.Хотько и Г.А,Дубровская (53) 681.327 (088.8) (56) Авторское свидетельство СССР

В 809182, кл. G 06 F 9/06, 1979. (54) УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ ПАМЯТЬЮ (57) Изобретение относится к вычислительной технике, а именно к управляющим устройствам памяти, может быть использовано в системах обработки данных и является усовершенствованием

„„80„„1280626 А 2 известного устройства для управления памятью по авт.св. Ф 809182. Цель изобретения — повышение надежности устройства. Устройство содержит блок памяти, блок адреса, блок записи и считывания, блок ввода данных, распределитель управляющих сигналов, счетчик адреса, блок записи адреса, регистр адреса программы, регистр адреса, блок считывания адреса, регистры данных, сумматоры, блоки сразнения и накопитель. В устройстве обеспечивается регистрация в накопителе степени заполнения блока памяти, что обеспечивает полное использование его ресурса. 2 ил.,1280626

Изобретение относится к вычислительной технике, а именно к управляющим устройствам памяти, и может быть использовано в системах обработки данных.

I 5

Цель изобретения — повышение надежности устройства.

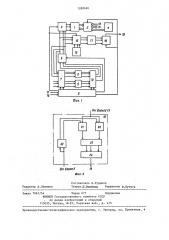

На фиг.1 показана струтурная схема устройства для управления памятью; на фиг.2 — структурная схема накопиf0 теля.

Устройство содержит (фиг.1) блок

1 памяти, блок 2 адреса, блок 3 записи и считывания, блск 4 ввода данных, распределитель 5 управляющих сигналов, счетчик 6 адреса, блок 7 записи ,адреса, "регистр 8 адреса программы,. регистр 9 адреса и блок 10 считывания адреса.

На фиг.1 обозначены вход 11 прерывания программы, вход 12 продолжения программы, информационные вход 13 и вход 14 °

Устройство также содержит блок граничных регистров 15, сумматоры .16, блоки 17 сравнения, накопитель

18, используемый в качестве блока регистрации данных, выход которого является выходом 19 устройства (на фиг.1 регистры 15, сумматоры 16, блоки 17 сравнения показаны объединенными в блоки).

Накопитель 18 содержит триггер 20, первую группу элементов И 21, вторую группу элементов И 22, группу ревер35 сивных счетчиков 23 и группу элементов ИЛИ 24.

Устройство для управления памятью работает следующим образом. 40

Рабочий объем памяти блока 1 памяти условно разделен на фиксированное число областей (зон), число которых определяется общим количеством объектов управления и объектов описания обстановки, информация по которым должна храниться в памяти. Зона памяти считывается занятой, даже если объем информационного массива, содержащийся в ней, меньше, чем объем зоны.50

Устройство может работать как в режиме считывания информации из зон, когда информационные массивы считываются из блока 1 памяти и передаются на выход 14 устройства, так и в режи-,у ме записи, когда информационные массивы, поступающие с входа 13 ус. тройства или блока 4 ввода данных, записываются в зоны блока 1 памяти.

Управляющие сигналы на входах 11 и 12 устройства формируются в устройстве управления и обмена, которое с одной стороны подключено к каналам управления и прерывания ЭВМ, а с другой — к устройствам управления внешними абонентами (не показаны). Сигнал на входах предлагаемого устройства является результатом определенных ситуаций в процессе функционирования

ЭВК, анализируемых управляющей программой, обеспечивающей организацию работы всего вычислительного комплекса, в котором используется предлагаемое устройство.

Сигнал по входу 11 устройства поступает в распределитель 5 управляющих сигналов, на одном из выходов которого появляется импульс, поступающий в блок 7 записи адреса. При этом разрешается перезапись содержимого счетчика 6 адреса в регистр 8 адреса программы. Сигнал с другого выхода распределителя 5 поступает в блок 10 считывания адреса и разрешает перезапись содержимого регистра 9 адреса в счетчик б адреса.

Затем сигналы с выхода распределителя 5 поступают в блок 2 адреса и сумматоры 16, осуществляя подачу кода адреса на адресные входы блока 1 памяти и выдачу кода, получившегося в результате суммирования в сумматорах

16, на входы блоков 17 сравнения.

В исходном состоянии в каждом из регистров 15 хранится дополнительный код, соответствующий начальному адресу каждой из зон и конечному адресу последней зоны блока 1 памяти. Количество регистров 15 на один больше, чем конечных зон (цепи, обеспечивающие предварительную запись кода, на фиг.1 не показаны) °

В процессе записи информационных массивов в сумматорах 16 осуществляется сравнение адресов, поступающих со счетчика 6 адреса с дополнительными кодами, хранящимися в регистрах

15. Количество сумматоров 16 равно количеству регистров 15.

Сигналы с выходов сумматоров 16 поступают на блоки 17 сравнения, где происходит сложение по модулю два сигналов с выходов соседних сумматоров 16, т.е. сигналы с выходов первого и второго сумматоров 16 поступают на входы первого блока 17, сигсигналы с выходов второго и третьего

1280626 сумматоров 16 — на второй блок 17 и т.д. Таким образом, если на входе какого-либо из блоков 17 указанные сигналы соседних сумматоров 16 не совпадают„ на выходе соответствующего бло- 5 ка 17 сравнения появляется сигнал, определяющий, в какую иэ зон блока 1 памяти происходит запись информации.

Этот сигнал поступает в накопитель

18, где через соответствующий элемент!0

И 21, открытый высоким уровнем с единичного выхода триггера 20, поступает на суммирующий вход соответствующего реверсивного счетчика 23, записывая в него единицу. Выходы каждого 15 реверсивного счетчика 23 объединены через группу элементов ИЛИ 24, наличие или отсутствие сигнала на выходе которых определяет, занята или свободна соответствующая зона блока 1 20 памяти, Триггер 20 устанавливается в единичное состояние сигналом с соответ. ствующего выхода распределителя 5 управляющих сигналов.

Количество блоков 17 сравнения и реверсивных счетчиков 23 равно количеству зон блока 1 памяти.

По окончании записи информации в блок 1 памяти по входу 12 устройства поступает сигнал в распределитель 5 управляющих сигналов. Блок 3 записи и считывания устанавливается в режим считывания.

Формирование управляющих сигналов 35 в распределителе 5 управляющих сигналов в режиме считывания информации аналогично режиму записи. На выходе распределителя 5 появляется сигнал, который подается в блок 7 записи ад- 40 реса и разрешает запись содержимого счетчика 6 адреса в регистр 9 адреса.

На другом выходе распределителя 5 появляется сигнал, который подается в блок 10 считывания адреса и разрешает 5 запись содержимого регистра 8 адреса программы в счетчик 6 адреса. В результате обеспечивается запоминание в регистре 9 адреса кода адреса, на ко- тором закончена запись информационных $p массивов в блок 1 памяти, и установка в счетчик 6 адреса кода адреса, содержащегося в регистре 8 адреса.программы, на котором ранее было осуществлено прерывание программы.

Код адреса со счетчика 6 адреса, поступающий на адресные входы блока

1 памяти, поступает и на входы сумматоров 16, где осуществляется его сложение с дополнительными кодами начальных адресов эон, хранящимися в ререгистрах 15. В случае несравнения сигналов с выходов сумматоров 16 на выходе соответствующего блока 17 сравнения появляется сигнал, который поступает в накопитель 18 на соответствующий элемент И 22, открытый высоким уровнем с нулевого выхода триггера

20. Последний устанавливается в нулевое состояние с соответствующего выхода распределителя 5. Сигнал с выхода элемента И 22 поступает на вычитающий вход соответствующего реверсивного счетчика 23, уменьшая его содержимое на единицу. Выходы счетчика

23 объединены через элемент ИЛИ 24, наличие на выходе которого определяет, занята или свободна зона.

При поступлении очередного сигнала на вход 11 устройство переходит из режима считывания в режим записи начиная с адреса, хранящегося в регистре 9 адреса, и работа устройства повторяется.

Формула и з о б р е т е н и я

Устройство для управления памятью по авт ° св. N- 880099118822, о т л и ч а ю— щ е е с я тем, что, с целью повышения надежности устройства, в него введены блок граничных регистров, блоки сравнения, накопитель и сумматоры, информационные входы которых подключены соответственно к выходам счетчика адреса и блоку граничных регистров, управляющие входы — к одному из выходов распределителя управляющих сигналов, выходы сумматоров соединены с входами блоков сравнения, выходы которых подключены к одним из входов накопителя, другой вход которого соединен с другим выходом распределителя управляющих сигналов, а выход является одним из выходов устройства.

1280626

gm Ж каХ

Фие. 2

Составитель В.Рудаков

Техред Л.Олейник Корректор В.Бутяга

Редактор А.Лежнина

Заказ 7067/54 Тираж 671 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4