Устройство для отладки программ

Иллюстрации

Показать всеРеферат

Изобретение относится к области :цифровой вычислительной техники и может быть использовано при отладке программ ЭВМ, в состав которых входят штатные блоки постоянной памяти с рабочими программами. Цель изобретения - сокращение аппаратурных затрат. Устройство для отладки программ содержит элемент И 1, группу регистров 2 установки, дешифратор 3 сигналов управления, схему 4 сравнения , распределитель 5.импульсов, шифратор 6 адреса, элемент ИЛИ 7, элемент НЕ 8, регистр 9 ввода, элементы И 10 и 11, схему 12 сравнения, запоминающий блок 13 без разрушения информации , блок 14 постоянной памяти. Данное устройство обеспечивает эффективную отладку программ за счет подмены участка памяти блока постоянной памяти зоной памяти блока без разрушед ния информации. 1 ил. (Л

СОЮЗ СОВЕТСНИХ соцИАЯ к,тичесних

РЕСПУБЛИН (19) (11) (gI) 4 G 06 F 11/28

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

19

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

flO ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

К A8TOPCHOMV СВИДЕТЕЛЬСТВУ (21) 3878221/24-24 (22) 27.03.85 (46) 30.12.86. Бюл. N - 48 (72) Т.Ф. Аверьянова, В.Т. Гулько, В.И. Пономарчук, Б.С. Севериновский и А.Ф. Соколенко (53) 681.3(088.8) (56) Авторское свидетельство СССР

Ф 1001099, кл. С 06 F 9/06, 1981..

Авторское свидетельство СССР

В 943726, кл. G 06 F 9/06, 1979. (54) УСТРОЙСТВО ДЛЯ ОТЛАДКИ ПРОГРАММ (57) Изобретение относится к области цифровой вычислительной техники и может быть использовано при отладке программ 3ВМ, в состав которых входят штатные блоки постоянной памяти с рабочими программами. Цель изобретения — сокращение аппаратурных затрат. Устройство для отладки программ содержит элемент И 1, группу регистров 2 установки, дешифратор 3 сигналов управления, схему 4 сравнения, распределитель 5.импульсов, шифратор 6 адреса, элемент ИЛИ 7, элемент HE 8, регистр 9 ввода, элементы

И 10 и 11, схему 12 сравнения, запоминающий блок 13 без разрушения информации, блок 14 постоянной памяти.

Данное устройство обеспечивает эффективную отладку программ за счет подмены участка памяти блока постоянной

C памяти зоной памяти блока без разруше- щ ния информации. 1 ил.

1280637

55

Изобретение относится к цифровой вычислительной технике и может быть использовако при отладке программ

ЭВМ, в состав которых входят штатные блоки постоянной памяти с рабочими 5 программами.

Цель изобретения — сокращение аппаратуркых затрат.

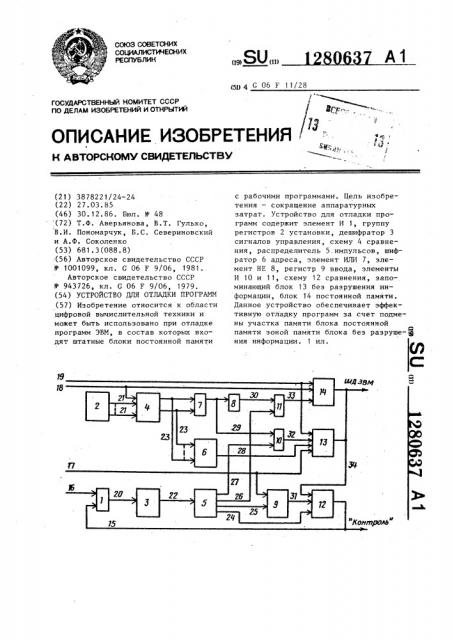

На чертеже приведена блок-схема устройства для отладки программ.

Устройство для отладки программ содержит элемент И 1, группу регистров 2 установки, дешифратор 3 сигналов управления, схему 4 сравнения, распределитель 5 импульсов, шифратор

6 адреса, элемент ИЛИ 7, элемент

НЕ 8, регистр 9 ввода, элементы И 10 и 11, схему !2 сравнения, запоминающий блок 13 без разрушения информации, блок 14 постоянной памяти

20 (БПП). На схеме показано;, выход устройства 15 "Контроль", вход 16 кода команды устройства, вход 17 информационный, первый 18 и второй 19 адресные входы устройства, выход 20 элемента И 1, выходы 21 группы регистров 2 установки, выход 22 дешифратора 3, выходы 23 схемы 4 сравнения, выходы 24-27 распределителя 5, которые обеспечивают соответственно стробирование,схемы 12, разрешение приема данных, разрешение записи-считывания, разрешение считывания, адресную шину 28 старших разрядов блока

13, выход 29 шифратора адреса, выход

30 сигнала несравнекия элемента НЕ 8, выход 31 регистра ввода, выход 32 элемента И 10, выход 33 элемента

И 11, выход 34 блока 13, являющийся информационным выходом устройства.

Устройство работает в двух режимах: полуавтоматическом, когда выполняется ввод-контроль отлаживаемых команд в блоке !3 и в автоматическом, когда устройство работает в составе

3ЕМ в качестве штатного блока (или

его части) постояккой памяти.

В полуавтоматическом режиме устройство работает следующим образом.

Предварительно выполняется занесение массивов команд в блок 13 из внешнего устройства. По входу 17 ка регистр 9 ввода и на вход блока

13 поступает информация, а по входу

16 — код команды, которая через элемент И 1 поступает на дешифратор 3 сигналов управления, с выхода которого сигналы управления поступают

2 на распределитель 5. С выхода распределителя 5 на элемент И 10 выдается сигнал записи информации в блок 13.

По адресным входам 18 и 19 из внешних устройств поступает код адреса, по которому выполняется запись в блоке 13, причем, если разрядная сетка отлаживаемого блока постоянной памяти не превышает разрядную сетку блока 13, то по адресным входам 18 поступает нулевой адрес и так как регистр 2 находится в нулевом состоянии, то с первой схемы 4 сравнения всегда выдается сигнал сравнения, который через элемент ИЛИ 7 и элемент И 10 разрешает обращение к блоку 13. Сигнал записи информации через элемент И 10 поступает в блок 13 и информация записывается в нем по адресу, поступающему по адресному входу 19. После записи информации в блок 13 выполняется контрольное считывание из блока 13 на схему 12 сравнения, где выполняется сравнение считанной информации с информацией, хранимой в регистре 9 ввода. При несравнении с приходом с распределителя 5 с выхода 24 сигнала строба схемы сравнения схема 12 сравнения выдает на выход 15 "Контроль" запрет на элемент И 1 о прохождении кода команды по входу 16 и сигнал "Контроль на выход устройства.

В том случае, когда объем отлаживаемой памяти БПП 14 превышает объем памяти блока 13 или же отлад- ка программ выполняется отдельными массивами, на регистрах 2 устанавливается адрес зоны БПП 14, которую необходимо заменить памятью блока 13.

Количество регистров 2 определяется размером зоны памяти отлаживаемого

БПП 14. Например, если объем отлаживаемого БПП 14 соответствует и-16 разрядам, а объем памяти блока 13 соответствующим m=13 разрядам адреса, размер зоны памяти выбран соответствующим k-9 разрядам адреса, тогда количество регистров 2 равно 2 =16.

Шифратор 6 адреса выполняет преобразование и — k=7 старших разрядов адреса отлаживаемого БПП 14 в m-k=4 старших разрядов блока 13. По входу 18 на схему 4 сравнения поступают старшие разряды кода адреса (в данном примере 7 старших разрядов) отлаживаемоro БПП 14. Тогда запись информации выполняется только в зону блока 13, 1280637

50

ВНИИПИ Заказ 7068/55 Тираж 671 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4 определяемую регистрами 2 и шифратором 6 адреса.

В автоматическом режиме устройство отладки работает в комплексе с

3ВМ в качестве штатного БПП или его части.

Адреса заменяемых зон БПП 14 памятью блока 13 устанавливаются на регистрах 2. Старшие разряды адреса по адресному входу 18 поступают на схему 4 сравнения, где сравниваются с кодом адреса, установленным на регистрах 2. Младшие разряды кода адреса по адресному входу 19 поступают непосредственно на БПП 14 и блок 13.

По входу 16 из 3ВМ через элемент И 1 дешифратор 3 сигналов управления вы дается команда считывания информации, по которой из распределителя 5 на элементы И 10 и 11 вьдаются сигналы считывания информации. Если на одной из схем 4 сравнения есть сигнал сравнения, то он через элемент ИЛИ 7 выдается на элемент И 10, и "". блок 13 вьдается сигнал считывания информа— ции, которая по выходу 34 поступает на выход устройства. Если нет сигнала сравнения ни на одной из схем сравнения, то сигнал считывания с распределителя 5 поступает через элемент И 11 на БПП 14, и информация считывается из отлаживаемого БПП 14 и через выход

34 выдается на выход устройства.

Формула изобретения

Устройство для отладки программ, содержащее распределитель импульсов, три элемента И, группу регистров установки, дешифратор сигналов управления, первую схему сравнения, элемент ИЛИ, элемент НЕ, запоминающий блок без разрушения информации и блок постоянной памяти, причем вход кода команды устройства соединен с первым входом первого элемента И, выход которого соединен с информационным входом дешифратора сигналов управления, выход которого соединен с входом запуска распределителя импульсов, первый и второй выходы которого соединены с первыми входами второго и третьего элементов И соответственно, выходы второго и третьего элементов

И соединены соответственно с входом записи запоминающего блока без разрушения информации и с входом считывания блока постоянной памяти, выходы регистров установки группы соединены с первым входом первой схемы сравнения, первый адресный вход устройства соединен с вторым входом первой схемы сравнения и с адресными входами старших разрядов блока постоянной памяти, выходы равенства схемы сравнения соединены с соответствующими входами элемента ИЛИ, выход которого соединен с вторым входом второго элемента И и через элемент НŠ— с вторым входом, третьего элемента И, информационный вход устройства соединен с информационным входом запоминающего блока без разрушения информации, второй адресный вход устройства соединен с адресными входами младших разрядов адреса блока постоянной памяти и запоминающего блока без разрушения информации, о т л и ч а ю щ е е с я тем, что, с целью сокращения аппаратурных затрат, в устройство введены шифратор адреса, регистр ввода, вторая схема сравнения, причем выходы равенства первой схемы сравнения соединены с соответствующими входами шифратора адреса, выходы которого соединены с адресными входами старших разрядов запоминающего блока без разрушения информации, третий и четвертый выходы распределителя импульсов соединены соответственно с входом стробирования второй схемы сравнения и входом записи регистра ввода, ин-.. формационный вход устройства соединен с информационным входом регистра ввода, выход которого соединен с первым информационным входом второй схемы сравнения, информационные выходы блока постоянной памяти и запоминающего устройства без разрушения информации соединены с вторым информационным входом второй схемы сравнения и являются информационным выходом устройства, выход неравенства второй схемы сравнения соединен с вторым входом первого элемента И и является выходом контроля устройства.