Преобразователь последовательного кода переменной длины в параллельный

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может , быть использовано в системах обмена данными по цифровьм ка:налам связи для преобразования последовательного кода переменной длины в параллельный . Целью изобретения является расширение области применения преобразователя за счет возможности приема кодовых посылок различной длины и его функциональных возможностей за счет контроля принимаемой информации. Поставленная цель достигается тем, что в известньй преобразователь введены второй сдвигающий регистр, дешифратор, первая и вторая группы элементов И, элементы ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, элемент НЕ, элементы И, второй триггер и н : первый сдвигающий регистр введен (п+2)-й разряд. Возможность приема кодовых посыпок различной длины обеспечивается за счет того, что начальная часть принимаемой кодовой посылки , содержащая код формата, принимается во второй сдвигающий регистр и управляет дешифратором, подключающим к триггеру режима один из разрядов первого сдвигового , Одновременно осуществляется контроль принимаемой информации по четности, 1 ил. о СЛ

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕСПУБЛИК (19) (11) (51) 4 Н 03 М 9/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ 13, H ABTOPCHOMY СВИДЕТЕЛЬСТВУ

ЫЦ6 ч:

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3955395/24-24 (22) 16.09.85 (46) 30.12.86.Бюл. ))- 48 (71) Львовский ордена Ленина политехнический институт им.Ленинского комсомола (72) Е.И.Подобаный, И.Н.Леськив, Н.М.111упляк, О.N. Öåïàê и О.С.Скальская (53) 621.394 (088.8) (56) Авторское свидетельство СССР

11 924696, кл. G 06 F 5/04, 1982.

Авторское свидетельство СССР

N 809160, кл. G 06 F 5/04, 1981. (54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА ПЕРЕМЕННОЙ ДЛИНЫ В ПАРАЛЛЕЛЬНЫЙ (57) Изобретение относится к автоматике и вычислительной технике и может,быть использовано в системах обмена данными по цифровым каналам связи для преобразования последовательного кода переменной длины в параллельный. 11елью изобретения является расширение области применения преобразователя за счет возможности приема кодовых посылок различной длины и его функциональных возможностей за счет контроля принимаемой информации. Поставленная цель достигается тем, что в известный преобразователь введены второй сдвигающий регистр, дешифратор, первая и вторая группы элементов И, элементы ИЛИ, элемент ИСКЗЮЧА10ЩЕЕ ИЛИ, элемент

НЕ, элементы И, второй триггер и т первый сдвигающий регистр введен (п+2)-й разряд. Возможность приема кодовых посыпок различной длины обес..печивается за счет того, что начальная часть принимаемой кодовой посылки, содержащая код формата, принимается во второй сдвигающий регистр и управляет дешифратором, подключающим к триггеру режима один из разрядов первого сдвигового региСтра.

Одновременно осуществляется контроль принимаемой информации по четности.

1 ил.

35! 128

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обмена данными по цифровым каналам связи для преобразования последовательного кода переменной длины в параллельHbIA .

Цель изобретения - расширение области применения преобразователя .за счет возможности приема кодовых посылок различной длины и его функциональных возможностей sa счет контроля принимаемой информации.

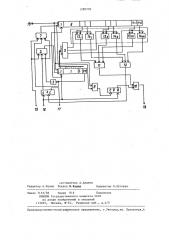

На чертеже изображена структурная схема предлагаемого преобразователя..

Преобразователь последовательного кода переменной длины в параллельный содержит (9+1)-разрядный сдвигающий регистр 1, элемент И 2, элемент

НЕ 3, первый триггер 4.режима, дешифратор 5 длины принимаемого слова, (n+2) разрядный сдвигающий регистр 6, элемент И 7, второй триггер 8, эле.мент И 9, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 10, элементы ИЛИ 11 и 12, первую группу

13 элементов И, вторую группу 14 элементов И. На чертеже также обозна чены тактовый вход 15, вход 16 "Начало сообщения", выходы 17 "Готов" и

l8 "Достоверность" и информационный вход 19.

Преобразователь работает следующим образом.

На вход 16 поступает сигнал, который записывает логическую "1" в первые разряды регистров 1 и 6, обнуляя остальные разряды. Одновременно этот сигнал поступает на установоч. ные входы триггеров 4 и 8, устанавливая первый в состояние логической

"1", а второй в состояние логического "0". При этом триггер 4 разрешает прохождение синхроимпульсов со входа 15, сопровождающих информационные биты, через элемент И 2 на тактовый вход регистра 1, на информацион ный вход которого поступает последовательный разрядный код формата принимаемой кодовой посылки. Накапливание информации в регистре 1 продолжается до тех пор, пока логическая "I",çànèñàííàÿ в младший разряд по сигналу "Начало сообщения", не продвинется в (1+1)-й разряд. Сигнал с выхода (I?+I)-го разряда поступает на элемент И 7, разрешая прохождение синхроимпульсов со входа 15 на элемент И 9 и тактовый вход регист0703 2 ра 6. Этот же сигнал, инвертируясь на элементе НЕ 3, запрещает прохождение синхроимпульсов на тактовый вход регистра 1, сохраняя, таким образом, в нем код формата принимаемой кодовой посылки. Этот код поступает на дешифратор 5, который в соответствии с ним открывает по одному элементу И из каждой группы 13, 14, разрешая поступление на тактовый вход триггера 4 через элемент ИЛИ 12 одного из разрядов регистра 6, а также. разрешает прохождение на вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ IO через элемент ИЛИ 11 предыдущего разряда регистра 6. По синхроимпульсам,.поступающим через элемент И 7 на регистр 6, производится запись поступающей кодовой посылки," при20 чем первым принимается контрольный разряд по четности. Одновременно синхроимпульсы, сопровождающие биты логической "1", выделяются элемен25 том И 9, поступают на вход"счетного триггера 8 и переключают его каждый раз в противоположное состояние.

Прием информации в сдвигающий регистр 6 производится до тех пор, пока логическая "1", записанная в младший разряд по сигналу "Начало сообщения", не продвинется в разряд, соединенный с открытым элементом И второй группы 14 и определяемый кодом формата принимаемой кодовой посилки. Сигнал этой логической "1", пройдя через открытый элемент группы 14 и через элемент ИЛИ 12, поступает на тактовый вход триггера

4 и устанавливает его в состояние логического "0". Одновременно контрольный разряд по четности с предыдущего разряда регистра 6, пройдя через открытый элемент И группы 13, сравнивается на элементе ИСКЛЮЧАЮ45 ЩЕЕ ИЛИ 10 с состоянием триггера 8, и в случае совпадения этих сигналов на выходе 18 преобразователя появляется сигнал "0", что сигнализирует о достоверности принятой информа50 ции.

В результате перехода триггера 4 в состояние логического "0" на выходе 17 преобразователя появится логическая "1", сигнализирующая об

55 окончании приема кодовой посылки, при этом сигнал с прямого выхода триггера

4 блокирует поступление синхроимпуль сов через элементы И 7 и 2 на регист703 з 1280 ры и 6, что приводит к сохранению принятой информации до следующего импульса "Начало сообщения". Формула изобретения .5

Преобразователь последовательного кода переменной длины в параллельный, содержащий первый (и+1)-разрядный сдвигающий регистр, где n — длина принимаемой кодовой посылки, первый 10 триггер, вход установки которого объединен с входом установки первого сдвигающего регистра и является входом "Начало сообщения" преобразователя, отличающийся 15 тем, что, с целью расширения области его примненения за счет возможности приема кодовых посылок различной длины и расширения его функциональных возможностей за счет контроля прини- 20 маемой информации, в преобразователь введены второй (1+1)-разрядный сдвигающий регистр, где à — длина кода формата принимаемой кодовой посылки, дешифратор, первая и вторая группы элементов И, элементы ИЛИ, элемент

ИСКЛИЧАНМ1ЕЕ ИЛИ, элементы И, второй триггер, и в первый сдвигающий регистр введен (и+2)-й разряд, информационный вход первого сдвигающего регистра объединен с информационным входом второго сдвигающего регистра и первым входом первого элемента И и является информационным входом преобразователя, выходы первых 1 раз- 35 рядов второго сдвигающего регистра соединены с соответствующими входами дешифратора, выходы которого соединейы с объединенными первыми:входами соответствующих элементов И пер- 40 .вой и второй групп, вторые входы соответствующих элементов И первой и второй групп соединены с выходами двух любых соседних разрядов первого сдвигающего регистра, выходы элементов И первой группы соединены с соответствующими входами первого элемента ИЛИ,.выход которого соединен с первым входом элемента ИСКЛИЧАЯЩЕЕ ИЛИ, выходы элементов И второй группы соединены с соответствующими входами второго элемента ИЛИ, выход

<оторого соединен с TGKToBblM входом первого триггера, инверсный выход которого является выходом Тотов" преобразователя, прямой выход первого триггера соединен с объединенными первыми входами второго и третьего элементов И, вторые входы которых объединены и являются тактовым входом устройства, выход (1+1)-го-. разряда второго сдвигающего регистра соединен с третьим входом второго элемента И непосредственно и с третьим входом третьего элемента И через элемент НЕ, выход третьего элемента

И соединен с тактовым входом второго сдвигающего регистра, выход второго элемента И соединен с тактовым входом первого сдвигающего регистра и вторым входом первого элемента И, выход которого соединен с тактовым входом второго триггера, вход установки которого объединен с входом установки второго сдвигающего регистра и подключен ко входу "Начало сообщения" преобразователя, инверсный выход второго триггера соединен с вторым входом элемента

ИСКЛЛЧА10ЩЕЕ ИЛИ, выход которого является выходом "Достоверность" преобразователя.

1280703

15 16

Составитель А.Авдеев

Редактор А.Ревин Техред В.Кадар Корректор О.Луговая

Заказ 7133/58 Тираж 816 Подписное

ВИИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35,- Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.ужгород,ул. Проектная,4