Устройство для возведения в степень

Иллюстрации

Показать всеРеферат

Изобретение отнЬсится к цифровой измерительной и вычислительной технике . Цель изобретения - повьшение функциональных возможностей устройства за счет одновременной реализации преобразований вида у k х и z п I .,« Устройство содержит генератор 15 образцовой частоты, первый блок 7 сложения.и вычитания частот, блок управления 13, счетчики 1, 2, группы 3, 4 элементов И, элементы ИЛИ 5, 6, делители частоты, формирователь импульсов. Новым в устройстве является введение элемента И 12, элемента 2-2И-ШШ 11 и второго блока 8 сложения и вычитания частот. 2 ил. &

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИК

А1

„„Я0„„12 211 (51) 4 С 06 F 7 552

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

H АBTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 374913-5/24-24 (22) 29 ° 05.84 (46) 07,01, 87. Бюл. Н - 1 (71) Физико-механический институт им. Г.В.Карпенко (72) Р.А.Воробель .и Я.В.Гапонюк (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф 454552, кл. G 06 F 7/552, 1972.

Авторское свидетельство СССР

В 553623, кл. G 06 F 15/31, 1975. (54) УСТРОЙСТВО ДЛЯ ВОЗВЕДЕНИЯ В

СТЕПЕНЬ (57) Изобретение относится к цифровой измерительной и вычислительной технике. Цель иэобретения — повьппение функциональных воэможностей устройства эа счет одновременной реализации преобразований вида у = k х и z

= k x . Устройство содержит генеZ ратор 15 образцовой частоты, первый блок 7 сложения и вычитания частот, блок управления 13, счетчики 1, 2, группы 3, 4 элементов И, элементы

ИЛИ 5, 6, делители частоты, формирователь импульсов. Новым в устройстве является введение элемента И 12, элемента 2-2И-ИЛИ 11 и второго блока 8 сложения и вычитания частот. 2 ил.

9 2 вход блока 13, вследствие чего на его втором выходе устанавливается низкий потенциал, а на первом — высокий. Поэтому доступ импульсов частоты f на вход счетчика 1 прекращается и разрешается поступление импульсов с выхода блока 8. В этот же момент времени t высокий потенциал с первого выхода блока 13 открывает элемент

И 12 и импульсы с выхода блока 7 начинают поступать на вход счетчика 2.

В момент времени t на четвертом вы< ходе блока 13 также появляется импульс, который устанавливает начальные значения N,,и N в счетчиках

1 и 2 соответственно. Ймпульсы с выходов счетчика 2 через элементы И 3, управляемые кодом числа N записанного в счетчике 1, элемент ИЛИ и делитель 9 поступают на вычитающий вход блока 7. Импульсы с выходов разрядов счетчика 1 через элементы И 4, управляемые кодом числа N1, записанного в счетчике 2, элемент ИЛИ 6 и делитель

10 поступают на вычитающий вход блока 8.

Процесс преобразования заканчивается в момент времени t8 = Т„ прихода заднего фронта импульса на выход формирователя 14, который устанавливает на первом выходе блока 13 низкий потенциал и тем самым прекращает поступление импульсов на входы счетчиков

1 и 2. В этот момент времени в счетчиках 1 и 2 формируются результаты преобразования чисел импульсов N,è И1 соответственно.

С момента времени t в счетчиках

< и 2 формируются коды чисел N и И1 оответственно =у

<< (1)

4.Т<

1 02

t< де f« и f< — средние частоты импульов на выходах элементов 2-2И-ИЛИ 11

12 соответственно, которые описыаются уравнениями разом. ! 1

Пусть, например, реверсивный счетчик 2 работает в режиме суммирования. 40

Перед началом преобразования на всех выходах блока 13 имеются низкие потенциалы. Формирователь 14, на вход которого .поступает преобразуемая час= тота Й<<, формирует импульсы длитель- 45 . ностью Т = 1И передние фронты ког х -х с торых поступают на первый вход блока и

13, вследствие чего на третьем выходе блока 13 появляется импульс, который в устанавливает счетчик 1 в исходное нулевое состояние. Одновременно на втором выходе блока 13 появляется высокий потенциал, который разрешает прохождение импульсов частоты f<1через элемент 2-2И-ИЛИ 11 на вход счет- 55 . чика 1. В некоторый момент времени й, в счетчике 1 формируется число N(„,1 =

2, и с выхода Р-ro разряда счет.чика 1 поступает импульс на второй

=f =f -f +f. °

7 о 9 7 1 (2) « где f u! 128211

Изобретение относится к цифровой измерительной.и вычислительной технике и может использоваться в качестве функционального преобразователя час-. тоты следования импульсов в код. 5

Цель изобретения — расширение функциональных возможностей устройства за счет одновременной реализации преобразований вида у = k

« r«

<- «)и< 10

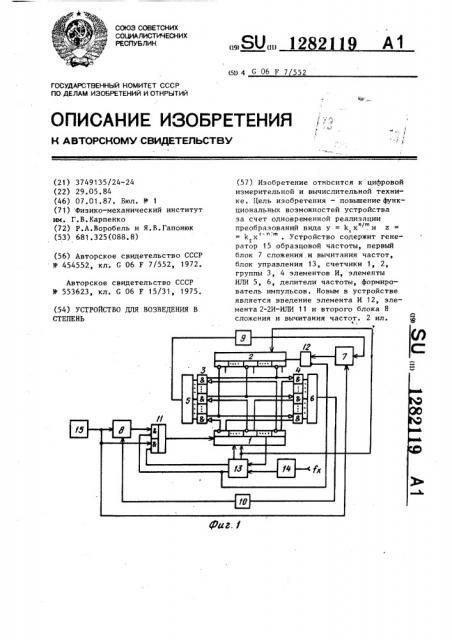

На фиг.1 показана функциональная схема устройства; на фиг.2 — функциональная схема блока управления.

Устройство содержит суммирующий счетчик 1, реверсивный счетчик 2, группы элементов И 3 и 4, элементы

ИЛИ 5 и 6, блоки 7 и 8 сложения и вычитания частот, делители 9 и 10 частоты, элемент 2-2И-ИЛИ 11, элемент И

12, блок 13 управления, формирователь 14 импульсов, генератор 15 образцовой частоты.

Блок 13 управления содержит триггеры 16 и 17, элемент 18 запрета, элементы И 19-21, элементы НЕ 22 и

23, элементы 24 и 25 задержки, формирователи 26-28 импульсов (дифференцирующие цепочки).

Блоки 7 и 8 сложения и вычитания частот выполнены аналогично,известному устройству.

Суммирующий счетчик 1 и реверсивный счетчик 2 выполнены двоичными, и-разрядными с коэффициентом пересчетаМ„,=2 35

Устройство работает следующим об а fo о + f8 — средние частоты импуль8 сов на выходах блоков

7 и 8 соответственно — частота на выходе генератора 15;

f — усредненные выходные частоты делителей 9 и

12821 и = f9/Ь;

dNz Nl

dt ЬN (3) <а ь /а <

f иЙ-се

dN<

Разделим ние (12) (13) (14) (15) 35

dN<

f.

dt (6) 40

9 а <о = а ° (8) 45

/Ь вЂ” < (9) 55

fyN<

«с

N„o (10) (а+Ь) NN» й

No< !!а2 то уравнение (19) т.е. N = — — — -QO)

< < о< Not (a+ Ь) И приобретает вид

f<< <<2 а. М<„

10 частоты с коэффициентами деления Ь и ц соответственно где р дние частоты на выходах элементов ИЛИ 5 и 6 соответственно.

Счетчик 1.с группой элементов И 4 и элементом ИЛИ 6 представляет собой двоичный умножитель частоты К« = Й на код числа N счетчика 2. Поэтому среднее значение частоты f<; на выходе !5 элемента ИЛИ 6, являющегося выходом двоичного умножителя, определяется выражением

< В «2 (4) 20

6 где N — коэффициент пересчета используемых счетчиков.

Счетчик 2 с группой элементов И 3 и элементом ИЛИ 5 представляет собой двоичный умножитель частоты f,z = Е на код числа N счетчика 1.

Поэтому среднее значение частоты

f на выходе элемента ИЛИ 5, являющегося выходом двоичного умножителя, определяется выражением

3. » < < (5)

Продифференцируем уравнения (1).

Получим

dN2 (7)

<2 д

Упростим систему уравнения (2).

Получим

В уравнения (8) подставим уравнения (3) 6/а о

Учитывая уравнения (4) и (5) имеем

19 4 то ° подставляя в уравнения (1О) уравнения (6) и (7), имеем — — -=f

Nz (12) а N уравнение (11) на уравнеdN2 N„а к2 dN< ь

Разделив переменные, имеем а Щ dN<

Проинтегрируем уравнение (14) н Ni а <И <2 (dN< а N, — lп N /N =1п — —.

Ь pz

Определим число N, а/Ъ м = я (— - -) о< аг

Продифференцируем уравнение (15)

pl

dN, = — — - (— — ) dN, . (16) а N, Nz ъ

N oz < < ог

Подставим уравнение (16) в уравнение (12) а

-" N (— — ) dN = f aN dt. (17) а. Nz ь

o< N 2 а «< аг

Проинтегрируем уравнение (17) а, 2 t-т»

Определим число N<

N N (— — ) -1 =f (а+Ь) х

N ь

0< 02 N аг о

x N (с — г.,); а (Ng ) b+ (a+b)N(N, — Nw ) () и а< . аг

< где N» = fpt = f«>x i !<1„, = fpt, количества импульсов, которые поступают на вход устройства в моменты времени т» и t соответственно. (a + b) N N» (а + Ь)!<1„,!

Если выполняется условие

1S (26) <1 12 с «» 2 °

dt зМ а с ф 55

=N (— Х-) 1(30) х

c-a (1 1« )о

2 02 Я

5 12821 ь

N = N (— --) . (21)

Nх а+Ъ о2

Подставив уравнение (21) в уравнение (15), получим

3 a!Ь а/b N а+Ь о+Ь о N

02 21 отсюда а о

Nx aib (22) gp «1

Если реверсивный счетчик 2 работает в режиме вычитания, то число N, соответствующее его коду, определяется уравнением

1 Т„

N2 N02 й1 dt . (23) Ь, Поэтому уравнение (7) в данном случае принимает вид

dN2 (24)

dt

Соответственно уравнение (11) принимает вид

dNÿ И<

dt bN (25)

Введем обозначение Ь = -s.

Тогда система уравнений (11) и (12) принимает вид

dN) N< — — - — — -=К (»)

dt a N

Система уравнений (11) и (r2) име- 35 ет решение вида (21) и (22). Очевидно, что решение системы уравнений (26) и (27) можно получить из уравнен««й (21) и (22) путем замены параметра Ъ на параметр з = -Ь.

4Р

Произведя эту замену имеем

-b о-Ь

N = N (— -); (28)

2 о2 а

a-b 45

N, = Яо, (— "-) . (29)

2t

Пусть коэффициент деления первого делителя равен Ь = (а — с /

Если 1) а > с, то Ь = а - с; если 2) а с с, то Ь = с — а.

5Р

В первом случае уравнения (28) и (29) имеют вид ц a(c

И = N (— «-) (31)

«1

19 6

Во втором случае уравнения (21) и (22) имеют вид (— x-) с = N (— -") (32)

2 о2 N< o2 (И«) с (33) к

При использовании устройства для преобразования высоких частот следования входных импульсов частота fx с выхода формирователя 14 подается на суммирующий вход блока 8 сложениявычитания, а частота f с выхода генератора 15 — на первый вход блока 13.

В этом случае количества входных импульсов N> и М« определяются не по формуле (18), а согласно выражению х = fxt,; 1 „= fxt5 = -xTo (34)

Уравнения (30) — (33) показывают, что устройство позволяет одновременно вычислять функции вида у = k, x о(в

t- n1м и z = k х для любого соотношения значений параметров и и m.

Формула изобретения

Устройство для возведения в степень, содержащее генератор образцовой частоты, суммирующий и реверсивный счетчики, первую и вторую группы элементов И, первый и второй элементы

ИЛИ, первый и вторбй делители частоты, первый блок сложения и вычитания частот, формирователь импульсов и . блок управления, первый вход которого подключен к выходу формирователя импульсов, вход которого соединен с . входом устройства, второй вход блока управления соединен с прямым выходом р-го разряда суммирующего счетчика (р йп, п — разрядность суммирующего счетчика), инверсные вьиоды разрядов суммирующего счетчика соединены с первыми входами соответствующих элементов И первой группы, вторые входы которых соединены с инверсными выходами соответствующих разрядов реверсивного счетчика, а выходы соединены с входами первого элемента ИЛИ, инверсные вьиоды разрядов реверсивного счетчика соединены с первыми входами соответствующих элементов И второй группы, вторые входы которьи соединены с прямыми. выходами соответствующих разрядов суммирующего счетчика, а выходы подключены к входам второго элемента ИЛИ, выходы первого и второ7 12821

rn элементов ИЛИ соединены с входами соответственно первого и второго делителей частоты, выход первого делителя частоты подключен к вычитающему входу первого блока сложения и вычитания частот, о т л и ч а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет одновре- . менной реализации преобразований вида

k)х 2 = k x устройство 10

tl/ m <- il >

-, содержит элемент И, элемент 2-2И-ИЛИ и второй блок сложения и вычитания

1 частот, суммирующий вход которого соединен с выходом генератора образцовой частоты и суммирующим входом пер- 15 вого блока сложения и вычитания частот, вычитающий вход второго блока сложения и вычитания частот соединен с выходом второго делителя частоты, а выход — с первым входом первой 20 группы элемента 2-2И-ИЛИ, первый. вход второй группы которого соединен с выходом генератора образцовой частоты, второй вход первой группы элемента

2-2И-ИЛИ соединен с первым выходом блока управления и первым входом элемента И, второй вход второй группы элемента 2-2И-ИЛИ соединен с вторым .выходом блока управления, третий выход которого подключен к входу обну" 30 ления суммирующего счетчика, а четвертый — к установочному входу суммирующего и реверсивного счетчиков, выход первого блока сложения и вычитания частот соединен с вторым входом элемента И, выход которого соединен с информационным входом реверсивного счетчика, информационный вход

19 суммирующего счетчика соединен с выходом элемента 2-2И-ИЛИ, при этом блок управления содержит два триггера, два элемента задержки, три элемента И, два элемента НЕ, элемент запрета и три формирователя импульсов, причем первый вход блока управления через первый элемент задержки соединен с первым информационным входом элемента запрета и R-входом первого триггера, прямой выход которого соединен с управляющим входом элемента запрета и первыми входами первого и второго элементов И, первый вход, блока управления через первый формирователь импульсов соединен с входами первого элемента НЕ и второго элемента задержки, второй вход блока управления через второй формирователь импульсов и второй элемент НЕ соединен с S-входом первого триггера, выход первого элемента НЕ соединен с S-входом второго триггера, прямой выход которого соединен с вторым информационным входом элемента запрета, вторым входом первого элемента И и первым входом третьего элемента И, второй вход которого подключен к выходу второго элемента задержки, прямой выход первого триггера через третий формирователь импульсов соединен с вторым входом второго элемента И, выходы первого элемента И, элемента запрета, третьего и четвертого элементов И соединены соответственно с первым, вторым, третьим и четвертью выходами блока управления.

1282119

Корректор С.Шекмар

Техред Л.Сердюкова

Редактор О.Бугир

Заказ 7267/47 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4