Устройство для распределения заданий между эвм

Иллюстрации

Показать всеРеферат

Изобретение относится к автоматике и вычислительной технике и может быть использовано в системах обмена и обработки данных в качестве распределяклдего устройства. Цель изобретения - сокращение времени ожидания задач. Устройство содержит три канала, каждый из которых содержит два блока регистров, накапливающий сумматор, коммутатор, схему сравнения, группу схем сравнения, блок элемента И, первый и второй элементы И. элемент ИЛИ. Новыми в устройстве являются блоки регистров, накапливающий сумматор, коммутатор и -элемент И. В устройстве происходит распределение задач между ЭВМ в соответствии с суммарным временем решения задач в машинах. 2 ил. а 9 (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (so 4 G 06 F 9 4 6

Э а

) !

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3931236/24 — 24 (22) 12.07.85 (46) 07.01.87. Бкл. и 1 (72) Г.Н. Тимонькин, В.П. Улитенко, С.H. Ткаченко, В.С. Харченко, Д.В. Дмитров и Б.О. Сперанский (53) 681.325(088.8) (56) Авторское свидетельство СССР

У 857993, кл. G 06 F 9/00, 1981.

Авторское свидетельство СССР

Р 1111163, кл. G 06 F 9/46, 1983. (54) УСТРОЙСТВО ДЛЯ РАСПРЕДЕЛЕНИЯ

ЗАДАНИЙ МЕЖДУ ЭВМ (57) Изобретение относится к автоматике и вычислительной технике и

ÄÄSUÄÄ 1282129 А1 может быть использовано в системах обмена и обработки данных в качестве распределяющего устройства. Цель изобретения — сокращение времени ожидания задач. Устройство содержит три канала, каждый из которых содержит два блока регистров, накапливающий сумматор, коммутатор, схему сравнения, группу схем сравнения, блок элемента И, первый и второй элементы И элемент ИЛИ. Новыми в устройстве являются блоки регистров, накапливающий сумматор, коммутатор и -элемент И. В устройстве происходит распределение задач между ЗВМ в соответствии с суммарным временем решения задач в машинах. 2 ил.

1282129

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных и распределяющих устройств и систем. 5

Цель иэ обр ете ния — сокращение времени ожидания задач.

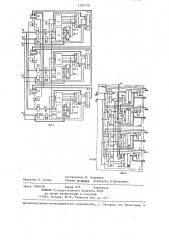

На фиг. 1 приведена функциональная схема устройства; на фиг..2 функциональная схема первого и второго блоков регистров.

Устройство для распределения заданий между ЭВМ (фиг .1) содержит три канала, а каждый канал включает блоки 1 и 2 регистров, накапливающий сумматор 3, коммутатор 4, схему

5,сравнения, группу схем 6 сравнения, блок 7 элементов И, первый 8 и второй 9 элементы И, элемент ИЛИ

10, кодовые входы 11 устройства.

Устройство имеет также информационные входы 12, синхронизирующие входы 13 и 14 в каждом канале выход 15 накапливающего сумматора, вы ход 16 коммутатора 4, выход 17 бло-, ка 7 элементов И, выход 18 элемента

И 9, выходы 19 схем 6 сравнения 6.

Блоки 1 и 2 регистров (фиг.2) по своей структуре и входам — выходам являются идентичными и содержало каналы, а каждый канал содержит регистр

20, блок 21 элементов ИЛИ, элементы

И 22 и 23, элементы ИЛИ 24 и 25 (последний канал не содержит блок элементов ИЛИ 21).

Устройство работает следующим образом.

В исходном состоянии все ЭВМ свободны и находятся в работоспособном состоянии, блоки 1.1-1.3, 2.1-2.3 регистров и сумматоры 3.1-3.3 установлены в нулевое состояние (входы начальной установки не показаны).

Равенство содержимого сумматоров 3.13.3 обуславливает выдачу с выходов

"Меньше-равно" схем 5. 1-5. 3, сравнения единичных сигналов. Поэтому на выходе элемента И 8.1 присутствует единичный сигнал, который открывает блок 7. 1 элементов И для переда50 чи кода задачи и кода времени ее выполнения в .первый канал.

Блоки 7.2 и 7.3 элементов И закрыты нулевыми сигналами с выходов соответствующих элементов И 8.2 и

8.3. Поэтому код задачи и код времени ее решения с входа 12 устройства через блок 7.1 элементов И поступает в первый канал. Причем код задачи поступает на информационные входы блока 2.1 регистров и непосредственно в ЭВМ для решения.

Код времени решения задачи поступает на информационные входы блока

1.1 регистров и на суммирующие входы сумматора 3.1. По синхроимпульсу с входа 13 устройства осуществляется запись кодов задачи и времени ее решения в первые регистры блоков 1.2 и 1. 1 соответственно. Кроме того, к содержимому сумматора 3.1 прибавля-. ется код времени решения данной задачи.

Код второй задачи и код времени ее решения поступают во второй канал, поскольку на выходе "Больше" схемы

5.2 сравнения н на выходе "Меньшеравно" схемы 5.3 сравнения присутствуют единичные сигналы. Запись кода задачи и кода времени ее решения происходят по описанному алгоритму.

Код третьей задачи и код времени ее решения аналогично описанному поступают в третий канал.

После этого на входы элементов

5.2-5.3 сравнения поступают коды времени задач, находящихся в сумматорах

3.1-3.3 и соответствующих времени решения той или иной задачи.

Таким образом, следующую задачу, код которой поступает на вход 12, необходимо направить в ту ЭВМ, в которой код суммарного времени решения ранее поступивших задач минимален.

Допустим, что такой код записан в сумматоре 3.2.

Тогда на выходе "Больше" схемы 5 ° 2 сравнения и на выходе "Меньше-равно схемы 5.3 сравнения присутствуют единичные сигналы. Поэтому единичный сигнал с выхода элемента И 8.2 открывает блок 7.2 элементов И для пере= дачи кода очередной задачи и кода .времени ее решения во вторую ЭВМ.

Через блок 7.2 элементов И код задачи и код времени ее решения по синхроимпульсу с входа 13 заносится в блоки 2.2 и 1.2 регистров соответственно. Кроме того, код времени решения поступает на суммирующий вход накапливающего сумматора 3.2. По тому же синхроимпульсу, по которому произошла запись в блоки 2.2 и 2.1, происходит приращение содержимого сумматора 3.2. Таким образом, в сум маторе 3.2 накапливается суммарное время решения двух задач.

Аналогичным образом следующий код очередной задачи и код времени ее решения поступают в канал. При этом в соответствующем сумматоре

3.1-3.3 канала код суммарного времени решения задач минимальный.

После завершения выполнения задачи ЗВМ выдает код этой задачи на соответствующий вход 11, который поступает на входы соответствующих схем 6 сравнения. При этом на выходе соответствующей схему 6, вторые входы которой подключены к выходам регистра, хранящего код данной задачи, выдается единичный сигнал.

Зтот сигнал открывает коммутатор 4 для передачи кода времени решения данной задачи, так как адреса записи кода задачи в блоке 2 и кода времени ее решения в блоке 1 равны. Код времени решения задачи с выхода коммутатора 4 поступает на вычитающий вход сумматора 3. Код задачи с входа 11 через элемент ИЛИ 10 открывает элемент И 9. Поэтому синхронизирующий сигнал с входа 14 поступает на входы блоков 1.1 и 2.1 регистров и на синхронизирующий вход сумматора

3. По этому сигналу из содержимого сумматора 3 вычитается код времени выполненной задачи.

82129

4 ственно, выход Меньше-равно" схемы сравнения третьего канала подключен к второму входу первого элемента И второго канала, выход Больше" схемы сравнения первого канала к второму входу первого элемента И третьего канала, в каждом канале выход первого элемента И подключен к входу блока элементов И, группа выходов каждого из которых является соответствующей группой выходов устройства, о т л и ч а ю щ е е с я тем, что, с целью сокращения времени ожидания задач, в каждый канал дополнительно введены первый и второй блоки регист10

25 ров, накапливающий сумматор, коммутатор, второй элемент И и группа схем сравнения, причем в каждом канале выходы блока элементов И подключены к информационным входам первых и вторых блоков регистров и к суммирующим входам накапливающих сумматоров всех каналов, выходы каждого сумматора подключены к первым входам схем сравнения своего и соседнего каналов, причем для первого канала соседним является второй, для второго — третий, для третьего — первый, каждая группа кодовых входов устройства подключена в одноименном канале к входам элемента ИЛИ, выход которого подключен в данном канале к первому входу второго элемента И, выход которого подключен к первым синхроИнформация на входах 11 должна появляться только после импульса с входа 13, но до прихода импульса с входа 14, и, кроме того, должна быть снята до прихода очередного импульса с входа 13.

Формула изобретения

Устройство для распределения заданий между ЗВМ, содержащее три канала и в каждом иэ них схему сравнения, блок элементов И, первый элемент И и элемент ИЛИ, группа информационных входов устройства подключена к группе входов блоков элементов И всех каналов, выходы "Меньшеравно" схем сравнения первого и второго каналов подключены к входам первогб элемента И первого канала, выходы "Больше" схем сравнения второго и третьего каналов подключены к первым входам первых элементов И второго и третьего каналов соответ50 рого блоков регистров и к управляющим входам коммутатора, каждая группа кодовых входов устройства подключена в одноименном канале к вторым входам схем сравнения группы, первый вход синхронизации устройства подключен к вторым синхронизирующим входам блоков регистров и накапливающего сумматора всех каналов, второй вход синхронизации устройства — к вторым входам вторых элементов И всех каналов.

35, низирующим входам блоков Регистров и накапливающего сумматора своего канала, выходы первого блока регистров подключены в своем канале к соответствующим информационным входам коммутатора, выходы которого подключены к вычитающим входам накапливающего сумматора, выходы втоРого блока регистров подключены в своем канале к первым входам соответствующих схем сравнения группы, вы-. ходы которых подключены в своем канале к управляющим входам первого и вто1282129

Фиг./

Составитель M. Кудряшов

Текред 3,Кадар Корректор Л.Пилипенко

Редактор О. Бугир

Заказ 7268/48 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб.,д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4