Буферное запоминающее устройство

Иллюстрации

Показать всеРеферат

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК..SU„„1282141

А1 (51)4 G 06 F 13 00

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ,:

И АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ

"! .: ..

Агась (21) 3773812/24-24 (22) 27.07.84 (46) 07.01.87. Бюл. 9 1 (72) В.А. Антонов и P.È. Гальпер (53) 681.327(088,8) . (56) Авторское свидетельство СССР .В 548889, кл. G 11 С 11/00, 1974.

Патент США М -3992699, кл. 365/36, опублик. 1976. (54) БУФЕРНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО (57) Изобретение относится к вычислительной технике и предназначено для использования в тех случаях, когда информация с выхода буферноro запоминающего устройства должна считываться в том же порядке, в каком она поступает на вход. Цель изобретения — повышение надежности и быстродействия устройства. Устройство содержит регистры 1, первый и второй счетчики 5 и 6, блоки 3 управления записью, коммутатор 7 адресов, коммутатор 2 данных, дешифратор 4, формирователь 9 импульсов и элемент ИЛИ 8. Коммутатор 7 содержит элементы И 10 и 11 (в каждом разряде), элемент ИЛИ 12 и элемент

НЕ 13. Коммутатор 2 содержит элементы И 14, элемент ИЛИ 15. 1 ил.

1282141

ВНИИПИ Заказ 7268/48

Тираж 670 Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

Изобретение относится к вычислительной технике и предназначено для использования в тех случаях, когда информация с выхода буферного запоминающего устройства должна считываться в том же порядке, в каком она поступает на вход.

Цель изобретения — повышение надежности и быстродействия устройства.

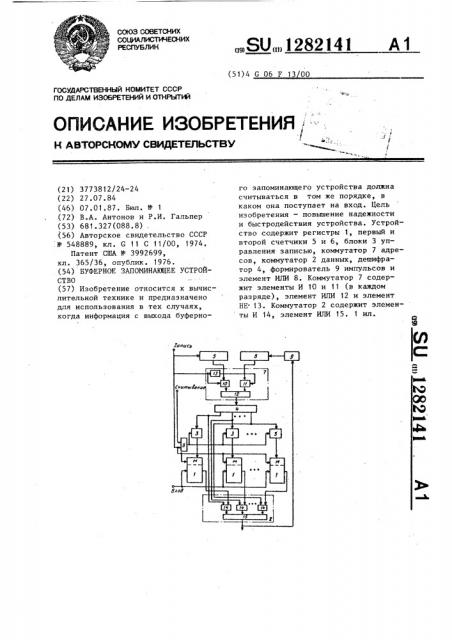

На чертеже приведена структурная схема буферного запоминающего устройства.

Устройство содержит регистры 1, коммутатор 2 данных, блоки 3 управления записью, дешифратор 4, первый

5 и второй 6 счетчики, коммутатор 7 адресов, элемент ИЛИ 8 и формирователь 9 импульсов.

Коммутатор 7 содержит элементы

И 10 и 11 (в каждом разряде), элемент ИЛИ 12 и элемент HF. 13.

Коммутатор 2 содержит элементы

И 14 и элемент ИЛИ 15.

Один иэ разрядов каждого регистра 1 используется в качестве маркерного. В качестве блоков 3 могут быть использованы элементы И.

Устройство работает следующим образом.

Записываемая информация в виде параллельного кода поступает на входы всех регистров 1. При появлении импульса на входе пЗапись" устройства происходит подключение выходов счетчика 5 через коммутатор 7 к входам дешифратора 4, который подает разрешающий потенциал на соответствующий блок 3. Происходит запись входного слова в соответствующий регистр 1, маркерный разряд которого устанавливается в "1".

Появление импульса на входе Считывание" устройства свидетельствует о том, что произошел съем информации с коммутатора 2 и необходимо извлечь информацию из следующего регистра 1.

Этот импульс, пройдя через элемент

ИЛИ 8 и соответствующий блок 3, запишет "0" в маркерный разряд соответствующего регистра 1. Этот "0" через коммутатор 2 поступает на вход формирователя 9 и отпирает его.

Непрерывная последовательность импульсов с выхода формирователя 9 поступает на счетный вход счетчика

6, который считает до тех пор, пока к коммутатору 2 не окажется подключен регистр 1, имеющий "1" в маркерном разряде. При этом формирова.тель 9 окажется запертым.

5 Если информация записана в несколько регистров 1, то с приходом импульса считывания на выходе формирователя 9 появится только один импульс.

Если в регистрах 1 нет информации, то формирователь 9 вырабатывает непрерывную последовательность импульсов.

Т аким обр аз ом, . по ступающая на вход устройства информация записывается в регистры 1, а на выход устройства поступает в той же последовательности, что и на вход.

Формула изобретения

Буферное запоминающее устройство, содержащее регистры, первый и второй счетчики, блоки управления записью, выходы которых соединены с управляю- щими входами соответствующих регистров, формирователь импульсов и эле30 мент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения надежности и быстродействия устройства, в него введены коммутатор адресов, дешифратор и коммутатор данных, информационные входы которого подключены к выходам регистров, один из выходов соединен с входом формирователя им пульсов, выход которого. подключен к счетному входу второго счетчика, вы ходы коммутатора данных являются вы40 ходами устройства, выходы коммутатора адресов через дешифратор подключены к управляющим входам коммутатора данных и первым входам блоков управления записью, вторые вхо- .

45 ды которых соединены с выходом элемента ИЛИ, первый вход которого, счетный вход первого счетчика и управляющий вход коммутатора адресов являются входом записи устройства, 5О входом считывания которого является второй вход элемента ИЛИ, выходы счетчиков подключены к информационным входам коммутатора адресов, информационные входы регистров поразрядно

55 соединены и являются информационными входами устройства.