Устройство для ввода информации

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано при передаче информации от одной ЭВМ в другую. Цель изобретения - расширение функциональных возможностей за счет выделения адресной ;информации из входного потока данных. Устройство содержит три счетуика, дешифратор , преобразователь кода, три триггера, семь элементов И, пять элементов ИЛИ, регистр и элемент задержки Устройство работает в двух-режимах: передает весь вводимый поток данных или часть массива данных, длину и адрес которого задают на счетчиках . 1 ил.

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

„„SU„„1282143 А1 (5D 4 G 06 F 13/РО!

< т с ! М

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н A ВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3919993/24-24 (22) 05.05.85 (46) 07.01.87. Бюл. Ф 1 (72) В.Д.Великан и В.И.Язневич (53) 681.3 (088.8) (56) Авторское свидетельство СССР

Ф 723561, кл. G 06 F 3/04, 1978.

Авторское свидетельство СССР к- 752317, кл. G 06 Р 13/00, 1978 ° (54) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ (57) Изобретение относится к области вычислительной техники и может быть использовано при передаче информации от одной ЭВМ в другую. Цель изобретения — расширение функциональных возможностей за счет выделения адреснбй ,:информации из входного потока данных.

Устройство содержит три счетчика„ дешифратор, преобразователь кода, три триггера, семь элементов И, пять элементов ИЛИ, регистр и элемент задержки, Устройство работает в двух -режимах: передает весь вводимый поток данных или часть массива данных, длину и адрес которого задают на счетчиках. 1 ил.

1282143

Изобретение относится к вычисЛительной технике и может быть использовано при передаче информации от одной ЭВМ в другую.

Цель изобретения — расширение 5 функциональных возможностей за счет вьделения адресуемой информации из входного потока данных.

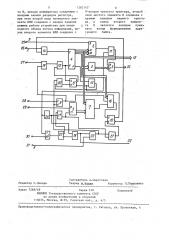

На чертеже представлена структурная схема устройства.

f0

Устройство содержит преобразователь 1 параллельного кода в последовательный, дешифратор 2, регистр 3, счетчик 4 адреса, счетчик 5 длины

15 массива, счетчик 6 числа переданных байтов, схему 7 сравнения, триггеры

8-10 элемент И 11 выходы 12 адреса вводимых данных, элементы И 13-18, элементы ИЛИ 19-22, повторитель 23, 20 элемент 24 задержки, информационный вход 25, тактовый вход 26, вход 27 задания режима работы устройства при вводе полного объема потока информации, вход 28 задания режима передачи вьделенной адресуемой информации, шину 29 задания длины массива вьданной информации, вход 30 задания числа передаваемых байтов, вход 31 сброса, информационный выход 32 и выход

33 признака конца формирования вводимого байта.

Устройство работает следующим образом.

Перед началом использования триггеры 9-10 должны быть в нулевом состоянии, Это достигается после подачи на вход 31 единичного сигнала "Сброс", Устройство может работать в одном из двух режимов передачи полного массива данных или заданного потока.

Первый режим задается подачей на вход 27 единичного импульса. По сигналу с входа 27 через элементы ИЛИ

19 и И 15 осуществляется установка

45 триггера 8 и обнуление счетчика 4.

Поступающие на вход 25 данные в параллельном коде под управлением сигналов от счетчика 4 преобразуются в преобразователе 1 в последовательный код, поступающий через открытый элемент И 11 на информационные входы триггеров регистра 3. На входы записи триггеров-регистра 3 поступают разрешающие сигналы с выходов дешифратора 2, 55 на входы которого поступают сигналы от счетчика 4, задающие номер з аписывае.".ього бита регистра 3. Изменение значения счетчика 4 осуществляется по сигналу, поступающему на тактовый вход 26. По сигналу переполнения счетчика 4 с выхода элемента И 13 через элемент ИЛИ 20 происходит сброс триггера 8. Например, если для задания номера бита поступающих на вход

25 данных необходимо до двенадцати двоичных цифр, то счетчик 4 должен иметь не менее двенадцати разрядов, при этом на входы адреса .преобразователя подаются разряды 1-12, на дешифратор — 10-12, на выходы адреса и схему сравнения — 1-9..

Передача состояния части данных осуществляется следующим образом. Номер начального бита подается на вход

29 и записывается в счетчик 5. Количество передаваемых байтов подается на вход 30 и записывается в счетчик

6. После этого второй режим задается подачей на вход 28 сигнала, по которому триггер 9 устанавливается в единичное состояние, и через элементы

ИЛИ 19 и И 15,,осуществляется установка триггера 8 и сброс счетчика 4. Поступающие на вход 26 тактовые сигналы через элемент И 14 увеличивают значение счетчика 4. На схеме 7 сравнения происходит сравнение значений счетчиков 4 и 5. В момент, когда содержимое разрядов счетчика 4, соответствующих адресу байта, равно содержимому счетчика 5, что определяется единичным значением на выходе "Равно" схемы 7 сравнения, с -выхода элемента И 16 поступает сигнал, по которому осуществляется установка триггера 10. Отсутствие сигнала на инверсном выходе триггера 10 через элемент И 14 блокирует изменение счетчика 4 по сигналу с тактового входа 26,.по сигналу прямого выхода 10 происходит уменьшение значения счетчика 6 на единицу. Сигнал с прямого выхода триггера 10 поступает также на вход элемента задержки, Величина задержки должна быть не меньшей, чем время приема байта информации во внешнее устройство ° С выхода элемента 24 задержки поступает сигнал, по которому через элемент И

17 (если значение счетчика 6 не равно нулю, что определяется на прямом выходе повторителя 23) осуществляется увеличение счетчика 5 на единицу и через элемент ИЛИ 21 — сброс триггера

10-. После этого на регистре 3 формируется очередной байт передаваемых! 282143 данных, завершение формирования которого вновь фиксируется установкой триггера 10. Если по сигналу с прямого выхода три-гера 10 на счетчике 6 установится нулевое значение, с ин- 5 версного выхода повторителя 23 поступает сигнал на вход элемента И 18, на выходе которого после поступления сигнала с выхода элемента 24 задержки формируется сигнал, указывающий. что осуществлена передача во внешнее устройство всей затребованной адресной информации. При этом через элемент ИЛИ 22 осуществляется сброс триггера 9, через элемент ИЛИ 20 — 15 сброс триггера 8 и через элемент ИЛИ

21 — сброс триггера 10.

Формула и з обретения

Устройство для ввода информации, содержащее пять элементов И, четыре элемента ИЛИ, счетчик адреса, счетчик длины массива, три триггера, регистр, причем первый вход первого элемента 25

И соединен с тактовым входом устройства, первый вход первого элемента

ИЛИ соединен с выходом второго элемента И, прямой выход первого триггера соединен с первым входом третьего 30 элемента И, прямой выход второго триггера соединен с первым входом четвертого элемента И, о т л и ч а— ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет выделения адресуемоч информации из входного потока данных, оно содержит шестой и седьмой элементы И, счетчик числа переданных байтов, дешифратор, схему сравнения, повтори- 40 тель, элемент задержки и преобразователь параллельного кода в последовательный, причем информационный вход преобразователя параллельного кода в последовательный соединен с информа- 45 ционным входом устройства, вход сброса которого соединен с вторым входом первого элемента ИЛИ, выход которого соединен с первым входом второго элемента ИЛИ, входом R второго триггера 50 и первым входом третьего элемента

ИЛИ, выход которого соединен с R-входом первого триггера, S âõîä которого соединен с выходом пятого элемента И и входом сброса счетчика адреса, вы- 55 ход переполнения которого соединен с вторым входом третьего элемента И, выход которого соединен с вторым входом третьего элемента И!И, выход преобразователя параллельного кода в последовательный соединен с первым входом шестого элемента И, вых . д которого соединен с информационными входами всех разрядов регистра, выходы которого являются выходами устройства, вход задания числа передаваемых байтов устройства соединен с информационным входом счетчика числа переданных байтов, выход заема которого соединен с входом повторителя, прямой и инверсный выходы которого соединены с первыми входами седьмого и второго элементов И соответственно, второй вход второго элемента И соединен с выходом элемента задержки и вторым входом седьмого элемента И, выход которого соединен с вторым входом второго элемента ИЛИ и счетным входом счетчика длины массива, группа разрядных выходов которого соединена с первой группой входов схемы сравнения, выход "Равно" которой соединен с вторым входом четвертого элемента

И, выход которого соединен с S-входом третьего триггера, прямой выход которого соединен с входом элемента задержки и вычитающим входом счетчика числа переданных байтов, инверсный вь1ход первого триггера соединен с первым входом пятого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, первый вход которого соединен с прямым выходом второго триггера, S-вход которого соединен с входом задания режима передачи выделенной адресуемой информации устройства, к шине задания длины массива выделенной информации устройства подключены информационные входы счетчика длины массива, инверсный выход третьего триггера соединен с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика адреса, первая группа разрядных выходов которого соединена с первой группой адресных входов преобразователя параллельного кода в последовательный, выходами адреса вводимого байта устройства и с второй группой входов схемы сравнения, вторая группа разрядных выходов счетчика адреса соединена с второй группой адресных входов преобразователя, с информационными входами дешифратора параллельного кода в последовательный и с группой входов четвертого элемен1282143

Составитель А.Сиротская

Техред В.Кадар. Корректор Л.Пилипенко

Редактор С.Пекарь

Заказ 7268/48 Тираж б70

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5 б

Подписное

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4 та И, выходы дешифратора соединеиы с входами записи разрядов регистра, при этом второй вход четвертого элемента ИЛИ соединен с входом задания режима работы устройства при вводе полного объема потока информации, выход второго элемента ИЛИ соединен с

R-входом третьего триггера, второй вход шестого элемента И соединен с прямым выходом первого триггера а выход второго элемен-, I та И являетс я выходом приз нака конца формирования адресуемого байта.