Многоканальное устройство для вычисления структурной функции

Иллюстрации

Показать всеРеферат

.Изобретение относится к вычислительной технике. Цель изобретения - повышение быстродействия устройств а. Сущность предложенного решения заключается в том, что коды отсчетов входного процесса преобразуются в позиционные коды, запоминаются и сравниваются с кодами текущих отсчетов. Устройство содержит аналого-цифровой преобразователь, регистры сдвига, синхронизатор, элементы ИСКЛЮЧАЮЩЕЕ ИЖ, элементы ИЛИ, блоки памяти, накопители . 1 ил.

СООЭ СОВЕТСНИХ

РЕСПУБЛИК ае (10

10 А1 (щ 4 G 06 F 15/36

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ

К АВТОРСКОМ,Ф СВИДЕТЕЛЬСТВУ (21) 3921849/24-24 (22) 02.07.85 (46) 07.01.87. Бюл. И 1 (7 1) Ивано-Франковский институт нефти и газа (72) Я.Н.Николайчук (53) 681, 3 (088. 8) (56) Авторское свидетельство СССР

У 337784, кл. G 06 F 15/336, 1970.

Авторское- свидетельство СССР

Ф 1115062, кл. G 06 F 15/36, 1982.

Авторское свидетельство СССР

9 840924, кл. G 06 F 15/36, 1977. (54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ДЛЯ вычисления стРуктуРнОЙ Функции (57) Изобретение относится к вычислительной технике. Цель изобретенияповышение быстродействия устройства.

Сущность предложенного решения заключается в том, что коды отсчетов входного процесса преобразуются в позиционные коды, запоминаются и сравниваются с кодами текущих отсчетов. Устройство содержит аналого-цифровой преобразователь, регистры сдвига, синхронизатор, элементы ИСКЛЮЧАЮЩЕЕ

ИЛИ, элементы ИЛИ, блоки памяти, накопители. 1 ил.

Формула из обретения налов, каждый из которых состоит из регистра и накопителя, группу из (N-1)-ro элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, синхронизатор, аналого-цифровой преобразователь> информационный вход ко товым входом аналого-цифрового преобразователя и входом разрешения ход накопителя каждого канала является соответствующим выходом значения структурной функции устройства, о тдый канал устройства введены группа из N элементов ИЛИ и блок памяти, причем первый вход каждого элемента

ИСКЛЮЧАКЩЕЕ ИЛИ группы соединен с выходом соответствующего разряда аналого-цифрового преобразователя, второй вход каждого i-го (i = 1...N-1) элемента ИСКЛЮЧАКЩЕЕ ИЛИ -руппы соединен с выходом (i+1)-го разряда аналогоцифрового преобразователя, выходы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ группы соединены с входами соответствующих разрядов регистра первого канала и первыми входами соответствующих элементов ИЛИ группы каждого канала, выход последнего разряда аналогоI цифрового преобразователя соединен с первого канала и с первым входом последнего элемента ИЛИ группы каждого, канала, выход каждого разряда регистра канала соединен с вторым входом соответствующего элемента ИЛИ группы того же .канала и с входом с одноименного разряда регистра следующего кака ла,выходы элементов ИЛИ группы каждого канала соединены с группой адресных входов блока памяти, выход которого соединен с входом накопителя, входы разрешения считывания блоков памяти являются входом задания выбора режима вычислений устройства.

1 1282160 2

Изобретение относится к вычисли- устройства на выходах накопителей 8 тельной технике, предназначено для сформируются двоичные коды значений статического анализа случайных про- структурной или модульной функции. цессов путем вычисления структурной функции и может быть использовано для корреляционной обработки сигнатов в реальном масштабе времени.

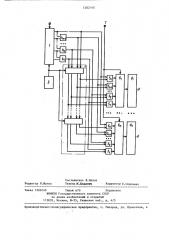

Цель изобретения — повышение быс- Иногоканальное устройство для вытродействия устройства. числения структурной функции, содерНа чертеже представлена структур- 1О жащее N (N — натуральное число) каная схема предлагаемого устройства.

Иногоканальное устройство для вычисления структурной функции содержит аналого-цифровой преобразователь

1, регистр 2 сдвига, синхронизатор 3; 15 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 4, элементы торого является входом устройства, ИЛИ 5, блоки 6 памяти, вход 7 зада- выход синхронизатора соединен с такния выбора режима вычислений и накопитель 8.

Устройство работает следующим об- 20 сдвига регистра каждого канала, выразом, В исходном состоянии накопителя 8 всех каналов устройства находятся в нулевом состоянии. Процесс вычисления л и ч а ю щ е е с я тем, что, с цезначений структурной или модульной лью повышения быстродействия, в кажфункции осуществляется за ш-циклов.

В начале каждого цикла на выходе синхронизатора 3 формируется импульс, который осуществляет запуск аналогоцифрового преобразователя 1 и сдвиг ЗО информации в регистре 2 сдвига, Вкаждом цикле на выходах преобразователя

1 формируется параллельный код отсчета входного процесса, который элементами ИСКЛЮЧАЮЩЕЕ ИЛИ 4 преобразу- 35 ется в позиционный. код, Полученный позиционный код с выходов элементов

ИСКЛЮЧИОЩЕЕ ИЛИ 4 одновременно посту- пает на информационные входы первого регистра 2 сдвига и вторые входы эле- 40 ментов ИЛИ 5, На первые входы элементов ИЛИ 5 при этом подаются коды задержанных отсчетов, хранимые в регис- входом одноименного разряда регистра тре 2 сдвига. На выходах логических элементов ИЛИ- 5 одновременно во всех каналах устройства формируются разрядно-позиционные коды модульных разностей текущего и задержанного отсчетов входного процесса, которые поступают на адресные входы блока 6 памя- 50 ти.,В зависимости от двоичного значения сигнала на входе 7 с выхода блока 6 памяти в накопители поступают параллельные двоичные коды квад.рата разности или модульной разности 55 текущих и задержанных отсчетов. В ре" зультате в конце m-ro цикла работы

1282160

Составитель В.Орлов

Техред M. Ходанич

Редактор И.Шулла. Корректор Е.Сирохман

Заказ 7269/49 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4!5

ПроизводСтвенно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4