Способ управления тиристорным регулятором

Иллюстрации

Показать всеРеферат

-Изобретение относится к области электротехники и может быть использовано в системах управления тиристорными регуляторами переменного напряжения, работающими на нелинейную нагрузку типа инфракрасных кварцевых нагревателей. Цель изобретения - повьппение надежности тиристорного регулятора в работе на нелинейную ка-г грузку. Цель изобретения достигается тем, что импульсы отпирания тиристоров регулятора 1 формируют путем сочетания фазового и число-импульсного управления согласно логической операции совпадения, осуществляемой элементом 9 совпадения. При этом сигналу задания U д соответствует частота следования импульсов отпирания, а фазу отпирания тиристоров регулятора 1 корректируют пропорционально сигналу, получаемому в результате интегрирования интегратором 12 разности , определяемой сумматором 5, между полученным с помощью шунта 3 и датчика тока 4 сигналом, пропорциональным максимальному мгновенному значению тока в нагрузке 2, и сигналом , пропорциональным допустимому току тиристоров, Ug .. Интегрирование производится в течение паузы между двумя соседними импульсами отпирания , на время следования которых интегратор 12 переводится в режим запоминания, а за сигнал управления фазой отпирания тиристоров принимают последовательность импульсов, длительность которых пропорциональна величине вькодного сигнала интегратора 12, сформированную преобразователем 7 напряжения во временной интервал . 2 ил. (Л го 00 ю ts9 00

СОЮЗ СОВЕТСНИХ

СОЦИАЛ ИСТИЧЕСНИХ

РЕаЪБЛИН (др 4:Н 02.М 5/257

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ.СВИДЕТЕЛЬСТВУ

° \

° а

° а

Риа t (21) 3841070/24-07 (22) 11,01.85 (46) 07,01.87. Бюл,9 1 (72) Э.И,Анисимов, В.А.Мартынов, Л.Л.Рыженков и В.В.Епифанов (53) 621,316,727(088,8) (56) Авторское свидетельство СССР

У 708480, кл, Н 02 М 5/257, 7/00, 1980, Скаржена В.А., Шелехов К.В.

Цифровое управление тиристорными преобразователями, Энергоатомиздат, 1984, с.8, (54) СПОСОБ УПРАВЛЕНИЯ ТИРИСТОРНЬМ

РЕГУЛЯТОРОМ (57) Изобретение относится к области электротехники и может быть использовано в системах управления тиристорными регуляторами переменного напряжения, работающими на нелинейную нагрузку типа инфракраснык кварцевых

1 нагревателей. Цель изобретения — по" вышение надежности тиристорного регулятора в работе на нелинейную на-, грузку. Цель изобретения достигается тем, что импульсы отпирания тиристоров регулятора 1 формируют путем сочетания фазового и число-импульсно„„5U„„1282287 A 1 го управления согласно логической операции совпадения, осуществляемой элементом 9 совпадения. При этом сигналу задания U g соответствует частота следования импульсов отпирания, а фазу отпирания тиристоров регулятора 1 корректируют пропорционально сигналу, получаемому в результате интегрирования интегратором 12 разности, определяемой сумматором 5, между полученным с помощью шунта 3 и датчика тока 4 сигналом, пропорциональным максимальному мгновенному значению тока в нагрузке 2, и сигналом, пропорциональным допустимому току тиристоров, U> „,. Интегрирование производится в течение паузы между двумя соседними импульсами отпирания, на время следования которых интегратор 12 переводится в режим запоминания, а за сигнал управления фазой отпирания тиристоров принимают последовательность импульсов, длительность которых пропорциональна величине выходного сигнала интегратора 12, сформированную преобразователем 7 напряжения во временной интервал, 2 ил.

1282287

1О

Изобретение относится к области электротехники и может быть использовано в тиристорных регуляторах перемепного напряжения, работающих на нелинейную нагрузку в виде инфракрасных кварцевых нагревателей.

Цель изобретения — повышение надежности тиристорного регулятора в .! работе на нелинейную нагрузку.

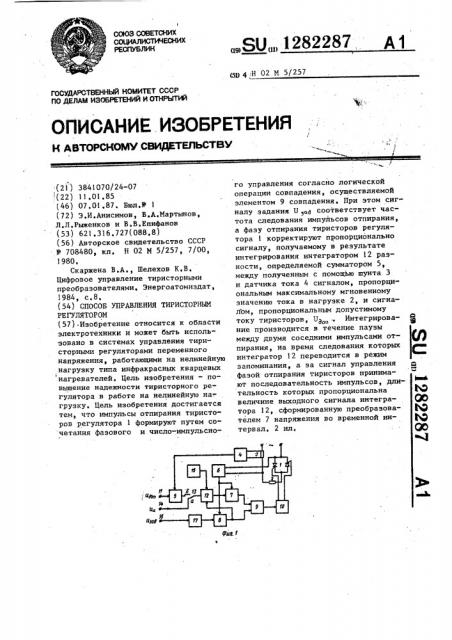

На фиг,1 показана устройство, реализующее предлагаемый способ; на фиг,2 — временные диаграммы работы устройства.

Устройство содержит силовой блок

1 регулятора с двумя встречно-параллельно включенными тиристорами и нагрузкой 2, последовательно с шунтом 3, у которого выход через датчик

4 тока подключен к первому входу сумматора 5. Вход блока 6 синхронизации присоединен к питающей сети, а его выход — к первым входам преобразователя 7 напряжения во временной интервал и управляемого коцом делителя 8 частоты, выходы которых обьединены элементом 9 совпадения, связанным через блок 1О формирования импульсов открытия с управляющими элек,тродами тпристоров силового блока 1, Второй вход сумматора 5 соедшЯн с клеммой 11 сигнала максимально допустимого значения тока тиристоров, Первый вход интегратора 12 соединен через переключатель 13 с выходом сумматора 5 и клеммой !4 сигнала инициации работы регулятора.

Второй sxop, регулятора подключен к блоку 15 пуска, а третий вход перевода интегратора в режим запоминания — к вьгходу делителя 8 частоты, Выход интегратора 12 связан с вторым

1 входом, преобразователя 7 напряжения во временной ин ;ервал, 1(лемма 16 сигнала задания частоты через аналого-цифровой преобразователь 17 соединена с вторым входом управляемого кодом делителя 8 частоты.

Способ управления состоит в том, что формирование импульсов отпирания тиристоров осуществляют путем сочетания фазового и число-импульсного управления согласно логической операции совпадения. При этом сигналу задания сботнетствует частота следования импульсов управления, а фазу отпирания тиристоров корректируют пропорционально сигналу, получаемому в результате интегрирования разности между максимальным мгновен,ным значением тока в нагрузке и допустимым током тиристоров в течение времени паузы между двумя соседними импульсами управления, Устройство, реализующее способ управления тиристорным регулятором, работает следующим образом.

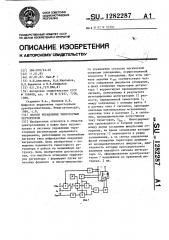

В исходном состоянии переключатель !3 находится в положении q (фиг.1). Пуск устройства осуществляется снятием сигнала блокировки, поступающего на интегратор 12 с блока 15 пуска.. При этом с клеммы 14 через замкнутый контакт переключателя 13 на вход интегратора 12 поступает сигнал U = U„ инициации рабо г ты регулятора (фиг. 2 ) .

Выходной сигнал U интегратора 12 подается на второй вход преобразователя 7 напряжения во временной интервал, на выходе которого формируются импульсы с длительностью, определяемой величиной сигнала U<< .

Одновременно с этим с клеммы 16 на второй вход делителя 8 частоты поступает преобразованный аналогоцифровым преобразователем 17 в код сигнал U

7 напряжения во временной интервал и делителя 8 частоты по питающему напряжению U„ сети осуществляется с помощью коротких импульсов U, поступающих с выхода блока 6 синхронизации. Сигнал с выхода элемента 9 совпадения поступает на вход формирователя 10 импульсов открытия, который вырабатывает импульсы отпирания тиристоров, осуществляя подачу в нагрузку 2 усеченных полуволн синусоиды импульсного напряжения U и про2 текание в ней тока 1 . При этом с шунта 3 преобразованный и усиленный датчиком 4 тока сигнал U<, соответствующий максимальному выбросу тока нагрузки, поступает на первый вход сумматора 5, на второй вход которого с противоположным знаком подается

1282287 4 пульсного управления, не подвергая искажению полуволны синусоиды напря жения, пропускаемые в нагрузку. сигнал U>., соответствующий допус оп тимому значению тока тиристоров I

on

На выходе сумматора 5 получается сигнал У разности У

В момент времени С после начала протекания тока I в нагрузке 2 осуществляют подключение переключателем !3 первого входа интегратора 12 к выходу сумматора 5.

В,положении S переключателя 13 t0 на первый вход интегратора 12 поступает сигнал д у = Ug „ - U, который интегрируется в течение времени

t>-С4. Выходной сигнал U, интегратора с помощью преобразователя 7 напряжения во временной интервал преобразуют Во временной интервал, соответствующий фазе отпирания тиристоров, и подают на первый вход элемен1 та 9 совпадения. По приходу на второй вход элемента 9 совпадения разре,t шающего сигнала Б с выхода делителя

8 частоты на выходе элемента 9 совпадения появляется сигнал U в виде парных импульсов для управления встречно-параллельно включенными тиристорами, фаза которых соответствует сигналу U„ на выходе интегратора, а частота их следования соответствует сигналу U > задания. При т этом в нагрузку будут пропускаться пары импульсов Uz положительной и отрицательной полярности, Далее процесс управления протекает аналогичным образом. Чтобы исключить ошибочную 35 работу интегратора на время t „ „—1.п H t, — протекания переходного процесса изменения тока в нагрузке 2, его переводят в режим запоминания.

Коррекцию фазы импульсов U с посте- 40 пенным уменьшением задержки углов отпирания тиристоров производят до тех пор, пока сопротивление нагревателей нагрузки 2 не перестанет меняться с ростом температуры. При 45 этом с выхода интегратора 12 через элемент 9 совпадения на блок 10 начнет поступать максимальный сигнал, при котором фаза отпирания тиристоров имеет минимальное значение, 50 близкое к нулю. В дальнейшем формирование импульсов отпирания тиристоров осуществляется путем число-имТаким образом, при комбинированном способе управления одновременно осуществляется регулирование частоты и коррекция фазы открытия тиристоров, кроме того, он позволяет избежать черезмерных бросков тока на начальных участках вольт-амперной характеристики кварцевого нагревателя, сопротивление которого существенно зависит от температуры, Так как частота пропускаемых в нагрузку импульсов тока меньше частоты сети, в паузах между ними, сетевое напряжение не имеет искажений, кроме того, автоматический переход на числоимпульсное управление исключает отказы регулятора от сбоев в блоке синхронизации.

Формула изобретения

Способ управления тиристорным регулятором, заключающийся в том, что импульсы отпирания тиристоров формируют.с частотой, меньшей частоты сети и пропорциональной сигналу управления частотой, о т л и ч аю шийся тем, что, с целью повьппения надежности регулятора в работе на нелинейную нагрузку,корректируют фазу импульсов отпирания, для чего измеряют мгновенное максимальное значение выброса тока нагрузки, определяют разность между допустимым значением тока тиристоров и мгновенным максимальным значением выброса тока нагрузки каждого преды" дущего включения, интегрируют эту разность в паузе между двумя соседними включениями, конечный резуль тат интегрирования на каждом интервале запоминают на время отпирания тиристоров и на следующем интервале интегрирование начинают с запом-. ненного значения, причем эа. сигнал управления фазой принимают последовательность импульсов, длительность которых пропорциональна величине результата интегрирования, 1 282287

Риг. 2

Составитель А,Меркулова

Редактор С,Патрушева ТехредВ.Кадар Корректор Л. Пилипенко

Заказ 7283/56

Тираж 661 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г,Ужгород, ул.Проектная,4