Аналого-цифровой преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к технике аналого-цифрового преобразования сигналов и может быть использовано в быстродействующих информационноизмерительных системах, где находят применение цифровые методы обработки аналоговой информации. Целью изобретения является упрощение конструкции и повышение быстродействия аналого-цифрового преобразователя параллельно-последовательного типа за счет уменьшения количества применяемых параллельных преобразователей с четырех до трех и применения более простых устройств и за счет выполнения коррекции погрешностей старших разрядов (результата первой ступени преобразования) одновременно с процессом преобразования во второй ступени без дополнительных затрат времени . Устройство содержит параллельные преобразователи 1-3, ЦАП 4, усилитель 5 разностного сигнала, счетчик 6, компаратор 7, триггер 8, усилитель 9 разностного сигнала, устройство 10 кодирующей логики с элементами И 11, 12, ИЛИ 13, выходной регистр 14. 1 з.п. ф-лы, 3 ил. / с €

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН (51) 4 Н 03 М 1/38

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ

ОПИСАНИЕ ИЗОБРЕТЕНИЯ й

f0 (21.) 3708990/24-24 (22) 11.03.84 (46) 07.01,87. Бюл. № 1 (72) В.З.Найдеров и 3.Ф.Юсупов (53) 681.325 (088.8) (56) Кондалев А.И. и др. Преобразователи формы информации для малых

ЭВМ. Киев: Наукова думка, 1982, с. 48-49, рис. З,б.

Электроника, 1982, № 9, с. 59, рис, 3. (54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к технике аналого-цифрового преобразования сигналов и может быть использовано в быстродействующих информационноизмерительных системах, где находят применение цифровые методы обработки аналоговой информации. Целью изоб„„SU,» 1282327 А1 ретения является упрощение конструкции и повышение быстродействия аналого-цифрового преобразователя параллельно-последовательного типа за счет уменьшения количества применяемых параллельных преобразователей с четырех до трех и применения более простых устройств и за счет, выполнения коррекции погрешностей старших разрядов (результата первой ступени преобразования) одновременно с процессом преобразования во второй ступени без дополнительных затрат времени. Устройство содержит параллельные преобразователи 1-3, ЦАП 4, усилитель 5 разностного сигнала, счетчик 6, компаратор 7, триггер 8, усилитель 9 разностного сигнала, устройство 10 кодирующей логики с элементами И 11, 12, ИЛИ 13, выходной регистр 14. 1 з.п. ф-лы, 3 ил. преобразователей 2 и 3 и выбора правильного кода на выходе одного из них. Задачу выбора правильного кода

55 второй ступени преобразования реша1 128232

Изобретение относится к технике аналого-цифрового преобразования сигналов и может быть использовано в быстродействующих информационноизмерительных системах, где находят применение цифровые методы обработки аналоговой информации.

Цель изобретения — повышение надежности за счет упрощения преобразователя и повышение быстродействия, 10

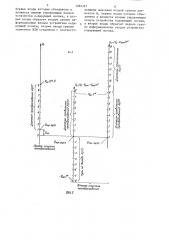

На фиг.1 показана функциональная схема преобразователя; на фиг.2 шкалы первой и второй ступеней преобразований (с целью упрощения рисунка количество разрядов используемых параллельных АЦП полагается рав-. ным трем — N = 3); на фиг.3 — временная диаграмма работы аналого-цифрового преобразователя.

Устройство содержит преобразователи 1-3 напряжения в код, цифроаналоговый преобразователь (ЦАП) 4, первый усилитель 5 разностного сигнала, счетчик 6, компаратор 7, триггер 8, второй усилитель 9 разностного сигнала, устройство 10 кодирующей логики, состоящее из первой 11 и второй 12 групп элементов И, группы элементов ИЛИ 13 и 2 N-разрядный выходной регистр 14. Ввведение указанных узлов позволило исключить из схемы преобразователя (фиг.1), кроме одного N-разрядного АЦП во второй ступени, сумматор дополнительного кода. Кроме того, введение новых эле- 35 ментов и связей между ними дало возможность осуществлять коррекцию погрешностей в коде первой ступени преобразования одновременно с процессом преобразования во второй ступени без 40 дополнительных затрат времени, что повысило быстродействие преобразователя.

Устройство работает следующим образом. 45

В начале каждого цикла работы осуществляется..грубое N-разрядное преобразование входного напряжения

U „ с помощью первого преобразователя 1 (первая ступень преобразова- 50 ния ). Результат грубого преобразования (выходной код первой ступени преобразования) с помощью высокоточного ЦАП 4 преобразуется в аналоговый сигнал U, „.

В отличие от известного устройства в преложенном разность напряжений U, и Б„, „ всегда имеет одну и

7 ? ту же полярность т.е. (Н -li ) >О. ч п

Для обеспечения этого условия на вход "Аналоговый нуль" преобразователя 1 подается начальное смешение, равное U„„, = Н,, где Ii„квант преобразователя (фиг.2) . В результате этого код первой ступени преобразования иа выходе всегда или не имеет погрешностей, или в нем отсутствует единица младшего разряда.

Эчо обеспечивает выполнение условия (U „— U,„ä„) > О, При этом, если в процессе преобразования в коде первой ступени имеется потеря единицы младшего разряда, то выходное напряжение усилителя 5 будет превышать уровень U„, 2, т.е. U

=IU, — U „„1 2 > U,„2 — напряжение U лежит в пределах диапазона переполнения преобразователя ? (фиг.2). В этом случае на выходе усилителя 9 будет такое напряжение, которое было бы на выходе усилителя

5 при отсутствии потери единицы младшего разряда, и выполняется уснапряжение U имеет значения нахо 3

2 дящиеся внутри диапазона правильных преобразований преобразователя

3 (фиг.2).

Если же в процессе преобразования в коде первой ступени погрешности отсутствуют, то напряжение Н „ будет иметь значения, находящиеся внутри диапазона от нуля до U 2 (диапаMP зон правильных преобразований преобразователя 2 на фиг.- ).

Таким образом, если в процессе .преобразования в коде первой ступени погрешности отсутствуют, то правильное значение усиленного разностного напряжения имеет место на выходе усилителя 5, а если в коде первой ступени имеется потеря единицы младшего разряда, то на выходе усилителя 9. Поэтому получение правильного кода второй ступени преобразования в предлагаемом устройстве заключается в одновременном (параллельном) преобразовании напряжений обоих усилителей 5 и 9 соответственно с помощью ют компаратор 7, триггер 8, первая

11 и вторая 12 группы элементов И, группа элементов ИЛИ 13.

1282327

Вторая ступень преобразования начинается с момента подачи на входы управления преобразователей 2 и 3 управляющего напряжения. Этот момент соответствует времени, равному

1 (время преобразования преобразователя 1) + t (время цифроаналогового

1 преобразования ЦАП 4) + t, t (вреMR,çàòðÿ÷èâàåìoå усилителями 5 и 9 на усиление разностного входного 10 сигнала до достижения установившегося выходного напряжения) от начала преобразования (фиг.3).

Компаратор 7 путем сравнения выходного напряжения усипителя 5, рав- 15 ного (U „— U„A„) 2, с. пороговым напряжением, равным U 2, вырабатыН вает управляющий сигнал, который через триггер 8 подается на входы первой 11 и второй 12 групп элементов 20

И для осуществления выбора правильного кода второй ступени преобразования, а также на суммирующий вход счетчика 6 для коррекции погрешности кода первой ступени. Причем коррекция осуществляется в счетчике одновременно с выполнением второй ступени преобразования путем добавления единицы младшего разряда к коду первой ступени (фиг.3). 30

Откорректированный код первой ступени с выхода счетчика 6 подается на выходной регистр 14 и образует в нем старшие N разрядов выходного . кода преобразователя. Выбранный правильный код второй ступени с выхода группы элементов ИЛИ 13 подает, ся на соответствующие входы выходного регистра и образует младшие

N разрядов выходного кода преобра- <0 зователя.

К моменту окончания процесса преобразования на выходе устройства (в выходном регистре) формируется

2 N-разрядный выходной код. На этом один цикл преобразования заканчивается. Общее время преобразования предложенного устройства меньше общего времени преобразования,известного практически на время выполне- 50 ния суммирования 2N-разрядного двоичного кода в сумматоре дополнительного кода. Это обстоятельство приводит к увеличению быстродействия преобразователя. 55

Фо р мула и з о бр е т е ни я

1. Аналого-цифровой преобразователь, содержащий первый преобразова- тель напряжения в код, выходы которого через цифроаналоговый преобразователь соединены с первым входом первого усилителя разностного сигнала, второй вход которого объединен со входом первого преобразователя напряжения в код и является входной шиной, а выход подключен ко входу второго преобразователя напряжения в код, выходы которого соответственно соединены с первой группой информационных входов устройства кодирующей логики, вторая группа информационных входов которого соединена с выходами третьего преобразователя напряжения в код, о т л и— ч а ю шийся тем, что, с целью повышения надежности за счет упрощения преобразователя и повышения быстродействия, в него введены компаратор, триггер, второй усилитель разностного сигнала, выходной регистр и счетчик, цифровые входы которого соединены соответственно с выходами первого преобразователя напряжения в код, выходы подключены к входам старших разрядов выходного регистра, а счетный вход объединен с первым управляющим входом устройства кодирующей логики и соединен с прямым выходом триггера, инверсный выход которого подключен к второму управляющему входу устройства кодирующей логики, а вход соединен с выходом компаратора, первый вход которого подключен к шине порогового напряжения, второй вход соединен с выходом первого усилителя разностного сигнала, с первым и вторым входами которого объединены соответственно первый и второй входы второго усилителя разностного сигнала, третий вход которого является шиной эталонного сигнала, а выход подключен ко входу третьего преобразователя напряжения в код, причем выходы устройства кодирующей логики соединены со входами соответственно младших разрядов выходного регистра.

2. Преобразователь по п.1, о т— л и ч а ю шийся тем, что в нем устройство кодирующей логики выполнено на первой и второй группе элементов И и группе элементов ИЛИ, выходы которых являются выходами устройства кодирующей логики, первые входы соединены с соответствующими выходами первой группы элементов И, 12823 у (-

Kitzp.

ПерЮ псе

Ы?дну слулегц лреодрюоАжцо первые входы которых объединены и являются первым управляющим входом устройства кодирующей логики, а вторые входы образуют вторую группу информационных входов устройства кодирующей логики, вторые входы группы элементов ИЛИ соединены с соответст27 6 вующими выходами второй группы злементов И, первые входы которых объединены и являются вторым управляющим входом устройства кодирующей логики, а вторые входы образуют первую группу информационных входов устройства коцирующей логики.

1?823? 7 аременноя диагранна рабаты аредлагаеного АЦ77

Начало лреоброзобания

1йжла &юрай @&наг стуаени лреофая

Юре чя н4 - ареодразодани

) 7 ореня задержки комлоратора 7

) ) в) я) годержки 7риггеро Р

) ) ) ф ареня сидора арабильного кода сличали И и ИЯи 1О, 1112 т — —

)1 брейся су ю ироаания

) ) 1 - а ФЛ ииноч сиетиике Ю

-f (Риг т

Составитель В.Махнанов

Техред М.Ходанич Корректор Л.Пилипенко

Редактор В,Данко

Заказ 7286/58 Тираж 899 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r.Óæãàðoä, ул.Проектная,4 ар етая арьев

1)4 -лреоб- ) ЦА- преад, розо5ания рагоаанил

Ж/ 11 1 @Ый орем ус-

) танааления) нноаряжения на Ь.юг

) усилителей 1

fuJ вв

Окончание 7реофааааанил у