Устройство для формирования биимпульсного сигнала

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи . Цель изобретения - фop мpoвa- ние сигнала узкого спектра. Устр-во содержит источник . 1 цифрового сигнала , два сумматора 2 и 4 по модулю два, триггер 3, два инвертора 5 и 11, блок ключей (ВК) 6, диф. у-ль 7, RC- фильтр 8, согласующий блок 9, источник 10 синхросигнала, регистр сдвига (PC) 12 и резисторный делитель (РД) 13 .Сформированнаяимпульсная последовательность биимпульсного относительно-, го сигнала, снимаемая с выхода сумматора 4Р поступает непосредственно и через инвертор 5 на входы управления БК 6. Б БК 6 происходит коммутатщя входного сигнала, поступающего с РД 13 на один из выходов БК 6 в зависимости от сигналов управления. Далее с помощью диф. у-ля 7, RC-фильтра 8 и согласующего блока 9 обеспечивается неискаясенность сформированного сиг- .нала, фильтрация ВЧ-составляющих и симметрия выхода данного устр-ва. Цель достигается введением сумматоров 2 и 4, БК 6, диф. у-ля 7, инвертора 11, PC 12 и РД 13. 1 ил. I (Л с

(51)4 Н 04 L 5/04

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3887345/24-09 (22) 22.04.85 (46) 07.01.87. Бюл. У 1

{72) В.Я.Середкин, Э.П.Лонч, Л.А.Кузнецов и Е.А.Колганов (53) 621.394.61 (088.8) (56) Авторское свидетельство СССР

N 93644?, кл. Н 04 L 5/04, 1982, (54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ

БИИМПУЛЬСНОГО СИГНАЛА (57) Изобретение относится к электросвязи. Цель изобретения — формирование сигнала узкого спектра. Устр-во содержит источник, 1 цифрового сигнала, два сумматора 2 и 4 по модулю два, триггер 3, два инвертора 5 и 11, блок ключей (БК) 6, диф. у-ль 7, RCфильтр 8, согласующий блок 9, источ„ЯИ.„1282345 А 1 ник 10 синхросигнала, регистр сдвига (PC) 12 и резисторный делитель (РД)

13.Сформированнаяимпульсная последо- вательность биимпульсного относительно-, го сигнала, снимаемая с выхода сумматора

4",поступаетнепосредственно и через инвертор 5 на входы управления БК 6.

В БК 6 происходит коммутация входного сигнала, поступающего с РД 13 на один из выходов БК 6 в зависимости от сигналов управления. Далее с помощью диф. у-ля 7, КС-фильтра 8 и согласующего блока 9 обеспечивается неискаженность сформированного сиг.нала, фильтрация ВЧ-составляющих и симметрия выхода данного устр-ва.

Цель достигается введением сумматоров 2 и 4, БК 6, диф. у-ля 7, йнвертора 11, PC 12 и РД 13. 1 ил.

1 128234

Изобретение относится к электросвязи и может использоваться в цифровых системах передачи, а также при построении передающих устройств, входящих в состав устройств преобразований сигналов, работающих по симметричным металлическим парам.

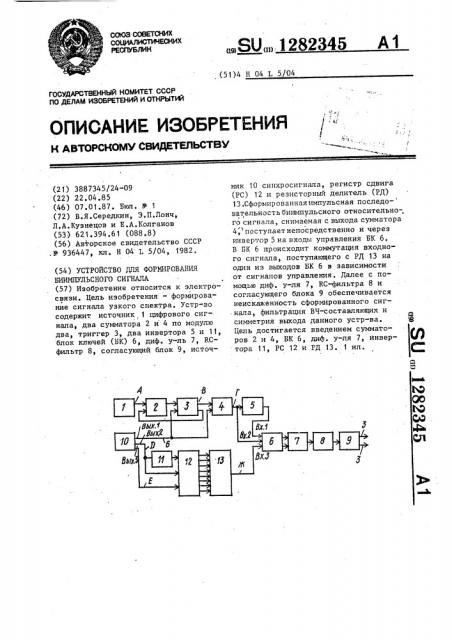

Цель изобретения — формирование сигнала узкого спектра, На чертеже изображена структурная 10 электрическая схема предлагаемого устройства.

Устройство для формирования биимпульсного сигнала содержит источник 1 цифрового сигнала, сумматор 2 15 по модулю два, триггер 3, сумматор 4 по модулю два, первый инвертор 5,блок

6 ключей, дифференциальный усилитель

7, КС-фильтр 8, согласующий блок 9, источник 10 синхросигнала, второй ин- 20 вертор 11, регистр 12 сдвига, резисторный делитель 13.

Устройство работает следующим образом.

Цифровой сигнал источника 1 поступает на первый вход сумматора 2 по модулю два, выходной сигнал которого приходит на D-вход триггера 3. При 0 цифрового сигнала сигнал на D-входе триггера 3 соответствует сигналу на инверсном выходе триггера 3, при этом триггер 3 работает в счетном режиме, переход из одного устойчивого состояния в другое происходит по положител -ьным .фронтам сигнала тональной 35 частоты (ТЧ) источника 10 синхросигнала.

При 1 цифрового сигнала триггер 3 сохраняет предыдущее состояние, так как сигнал íà D-входе триггера 3 на- 40 ходится в противофазе с сигналом на инверсном выходе триггера 3.

Сложение сигналов с прямого выхода триггера 3 и %актовой частоты в сумматоре -4.по модулю два обеспечива- "5 ет формирование относительного биимпульсного сигнала.

При таком формировании относитель ного биимпульсного сигнала устраняется эффект "обратной работы", харак- 50 терный для абсолютного биимпульсного сигнала, при котором смена символа, вызванная помехой, ведет не к единичной ошибке, повторяемой до следующей помехи, т.е. в интервале времени меж- 55 ду помехами принятые символы будут инверсны по отношению к переданным.

Импульсная последовательность биимпульсного относительного сигнала, 5 2 снимаемая с выхода сумматора 4 по модулю два, поступает на вход управления блока 6 ключей и через инвертор

5 — на другой вход управления блока

6 ключей.

Одновременно с выхода источника

10 синхросигнала, сигнал 32 ТЧ поступает на вход синхронизации регистра

12 сдвига, а сигнал 2 ТЧ вЂ” на вход установки режима регистра 12 сдвига и через инвертор 11 — на входы первого и восьмого разрядов регистра

12 сдвига.

Когда на входе установки режима присутствует низкий уровень напряжения, а на входе первого разряда высокий уровень напряжения, регистр

12 сдвига устанавливается в режим

"Сдвиг вправо", при этом происходит продвижен. е единицы с первого разряда на восьмой за восемь периодов сигнала 32 ТЧ. При изменении с низкого на высокий уровень напряжения на входе установки режима регистра 12 сдвига и присутствии на входе восьмого разряда низкого уровня напряжения регистр 12 сдвига устанавливается в режим "Сдвиг влево", при этом в регистре 12 сдвига происходит продвижение нуля с последнего разряда к первому за восемь периодов сигнала 32 ТЧ.

В этом случае обеспечивается формирование на выходе резисторного делителя 18 величины потенциала (ступеньки), зависящего от номинала резистора. Номиналы резисторов подобраны так, что реализуют функцию синуса за полутактовый период.

Это напряжение с выхода резистор- . ного делителя 13 поступает на вход блока 6 ключей.

В блоке 6 ключей происходит коммутация входного сигнала, поступающего с резисторного делителя 13 на один из выходов, в зависимости от сигналов управления.

При поступлении на входы один и два блока 6 ключей соответственно высокого и низкого уровней напряжений входной сигнал коммутируется на инверсный вход дифференциального усилителя 7, а при низком и высоком уровнях соответственно на входах один и два блока 6 входной сигнал коммутируется на прямой вход дифференциального усилителя 7, при этом инверсный вход дифференциального

Составитель Н.Лазарева

Редактор Н.Егорова Техред М.Коданич Корректор Т.Колб

Заказ 7287/58 Тираж 637 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, r.ужгород, ул.Проектная,4

3 128234 усилителя 7 соединяется с общим проводом.

Входной сигнал с выхода дифференциального усилителя 7 поступает через ВС-фильтр 8 на вход согласующего блока 9.

Частота среза КС-фильтра 8, определяющего границу пропускания фильтра, выбрана в два раза больше тактовой частоты, чем обеспечивается не- 10 искаженность сформированного сигнала и фильтрация высокочастотных составляющих

В согласующем блоке 9 двухтактный усилитель и согласующий трансформа- 15 тор обеспечивают как симметрию выхода данного устройства, так и согласование с линией по сопротивлению и установку заданного напряжения в линии. 20

Формула изобретения

Устройство для формирования биимпульсного сигнала, содержащее источник синхросигнала, источник цифрового сигнала, триггер, первый инвертор,, КС-фильтр и согласующий блок, о т— л и ч а ю щ е е с я тем, что, с целью формирования сигнала узкого спектра, в него введены регистр сдвига, резисторный делитель, блок ключей, 30 дифференциальный усилитель, два сумматора по модулю два и второй инвертор, причем выход источника цифрового сигнала через последовательно включенные первый сумматор по модулю два, триггер, второй сумматор по модулю два и первый инвертор соединен с первым входом блока ключей, выходы которого подключены к дифференциальному усилителю, выход которого через КС-фильтр соединен с входом согласующего блока, выходы которого являются выходами устройства, второй вход блока ключей соединен с выходом второго сумматора по модулю два, второй вход которого и второй вход триггера объединены и соединены с первым выходом источника синхросигнала,второй выход которого соединен первым входом регистра сдвига и через второй инвертор с вторым входом регистра сдвига, третий вход которого соединен с третьим выходом источника синхросигнапа, третий вход блока ключей соединен с выходом резисторного делителя, входы которого соеди иены с соответствующими выходами регистра сдвига, второй вход первого сумматора.по модулю два соединен с вторым выходом триггера.