Устройство для контроля последовательности чередования фаз напряжения трехфазной сети

Иллюстрации

Показать всеРеферат

Изобретение относится к измерительной технике и может быть использовано в различных системах автоматического контроля и управления. Цель изобретения - упрощение технической реализации устройства и повышение надежности его работы. Для достижения поставленной цели в устройство, содержащее формирователи I, 2 и 3 импульс ов, элементы И 6, 7, дополнительно введены элементы ИЛИ 4, 5 и элементы И 8, 9. В удтройстве исключены элементы долговременной памяти - триггеры, подверженные воздействию импульсных помех. 2 ил. (Л

QPl03 СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (51)4 С 01 R 29/18 фиг. 1

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3947045/24-21 (22) 25.05.85 (46) 15.01.87. Бюл. У 2 (71) Украинский государственный проектный и проектно-конструкторский институт "Металлургавтоматика" (72) Г.И. Лошкарев, В.А. Супруненко и В.С. Вакула (53) 621.317.72(088.8) (56) Авторское свидетельство СССР

9 750395, кл. G 01 R 29/18, 1979.

Авторское свидетельство СССР

N 851287, кл. G 01 R 29/18, 1980.

Авторское свидетельство СССР

N - 983588, кл. G 01 R 29/18, 1981.

„„ЯО„„1283674 А I (54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПОСЛЕДОВАТЕЛЬНОСТИ ЧЕРЕДОВАНИЯ ФАЗ НАПРЯЖЕНИЯ ТРЕХФАЗНОЙ СЕТИ (57) Изобретение относится к измерительной технике и может быть использовано в различных системах автоматического контроля и управления. Цель изобретения — упрощение технической реализации устройства и повышение надежности его работы. Для достижения поставленной цели в устройство, содержащее формирователи I, 2 и 3 импульсов, элементы И 6, 7, дополнительно введены элементы ИЛИ 4, 5 и элементы И 8, 9. В устройстве исклю- а чены элементы долговременной памяти—

С> триггеры, подверженные воздействию импульсных помех ° 2 ил.

С:

1283674

Изобретение относится к измерительной технике и может быть использовано в различных системах автоматического контроля и управления.

Целью изобретения является упрощение технической реализации устройства и повышение надежности его работы путем исключения элементов долговременной памяти — триггеров, подверженных воздействию импульсных по- 10 мех.

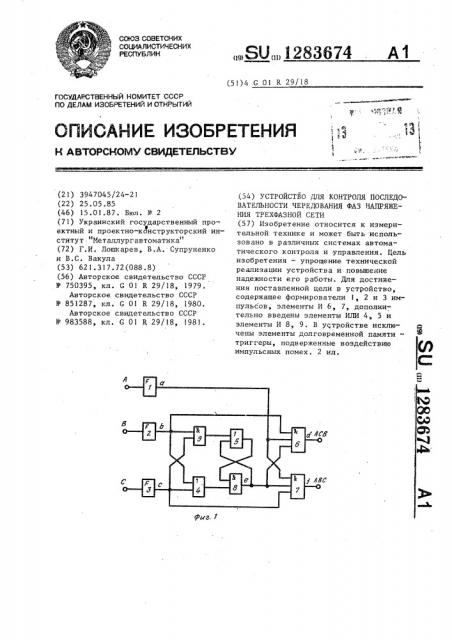

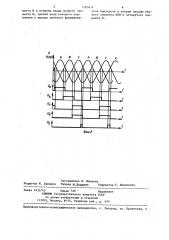

На фиг, 1 приведена функциональная схема устройства; на фиг. 2 временные диаграммы его работы (для случая прямой последовательности фаз

А-В-С-А-В...).

Устройство содержит три формирователя 1-3 импульсов, два элемента .ИЛИ 4 и 5 и четыре элемента И 6-9, причем входы ;формирователей 1-3 связаны с входными клеммами, выход пер вого формирователя 1 импульсов подключен к первым входам первого 6 и второго 7 элементов И, выходы кото25 рых являются выходами устройства, выход второго формирователя 2 импульсов подключен к второму входу первого элемента И 6 непосредственно, к первому входу третьего элемента И 8— через первый элемент ИЛИ 4, а к второму входу третьего элемента И 8 через последовательно соединенные четвертый элемент И 9 и второй элемент ИЛИ 5, второй вход которого соединен с входом третьего элемента И 8, 35 третьим входом первого элемента И 6 и вторым входом второго элемента И 7, третий вход которого подключен к выходу третьего формирователя 3 импульсов и вторым входам первого элемен- 40 та ИЛИ 4 и четвертого элемента И 9.

Устройство работает следующим образом.

На вход формирователя 1 прямоугольных импульсов подается фаза А 45 контролируемого напряжения, на вход формирователя 2 прямоугольных импульсов — фаза В, сдвинутая на 120 относительно фазы А, на вход формирователя 3 прямоугольных импульсов — 50 фаза С, сдвинутая на 240 относительно фазы А. Формирователи 1-3 преобразуют синусоидальное напряжение в последовательность прямоугольных.импульсов, причем длительность их вы- 55 бирается таким образом, чтобы обеспечивалось попарное перекрытие импульсов с выходов формирователей 1 и

2, 2 и 3 и 3 и 1 (см. фиг. 2).

При чередовании фаз АВС совпадение во времени сигналов на выходах формирователей 2 (V ) и 3 -(V ) приводит к появлению единичного сигнала на выходе четвертого элемента И 9 и затем на выходе третьего элемента И 8, причем сигнал на выходе третьего элемента И 8 будет удерживаться все время, пока на выходе первого элемента ИЛИ 4 будет присутствовать единичный сигнал (в рассматриваемом нами случае это обеспечивается импульсом с выхода формирователя 3).

При последующем появлении сигнала на выходе формирователя 1 (7„) на всех трех входах элемента И 7 присутст- вуют единичные сигналы и сигнал с его выхода (V ) будет сигнализировать о прямой последовательности чередования фаз (АВС).

При другой последовательности фаз

АСВ единичный сигнал будет периодически формироваться на выходе первого элемента И 6.

При обрыве хотя бы одной из фаз В и/или С не сработает первый элемент

И 6, а следовательно, не сработает элемент И 8, и условия для срабатывания выходных элементов 6 и 7 И выполняться не будут. Обрыв фазы А также полностью исключает формирование сигналов на выходных шинах.

Формула и з о б р е т е н и я

Устройство для контроля последовательности чередования фаз напряжения трехфазной сети, содержащее три формирователя импульсов, входы которых соединены с входными шинами, и два элемента И, первые входы которых соединены с выходом первого формирователя, а выходы — с выходными шинами, отличающееся тем, что, с целью упрощения и повышения надежности работы, в него введены третий и четвертый элементы И и два элемента ИЛИ, при этом выход второго формирователя импульсов подключен к второму входу первого элемента И непосредственно, к первому входу третьего элемента И вЂ” через первый элемент ИЛИ и к второму входу третьего элемента — через последовательно соединенные четвертый элемент И и второй элемент ИЛИ, второй вход которого подключен к выходу третьего элемента И, третьему входу первого эле1283674 ие

Составитель Н. Михалев

Редактор М. Бандура Техред М.Коданич Корректор Л. Пилипенко

Заказ 7433/43 Тираж 730 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 мента И и второму входу второго элемента И, третий вход которого подключен к выходу третьего формироваU (АДС теля импульсов и вторым входам первого элемента ИЛИ и четвертого элемента И.