Устройство для умножения

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах. Целью изобретения является повьшание быстродействия устройства умножения. Поставленная цель достигается тем, что в устройство для умножения, содержащее регистры первого и второго операндов, регистр результата, сумматор, два коммутатора и дополнительный регистр, введены блок определения меньшего операнда и блок определения большего операнда , блок управле - ния , третий коммутатор и вы - читатель . Результат умножения представлен двоично -К -и записью. 2 ил. о «е

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК (19) (11) Ai (511 4 G 06 F 7 49

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЯТЕПЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21 ) 3919654/24-24 (22) 01.07.85 (46) 15.01.87. Бюл, Ф 2 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) И.А.Дичка, В.И.Корнейчук, В.П.Тарасенко (80) и Заир Хаддад (02) (53) 681.325(088.8) (56) Авторское свидетельство СССР

Ф 383044, кл. G 06 F 7/52, 1970.

Авторское свидетельство СССР

1005035, кл. G 06 F 7/49, 1981. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ (57) Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах. Целью изобретения явля е т ся по вышени е быс тр оде йс твия ус тройства умножения..Поставленная цель достигается тем, что в устройство для умножения, содержащее регистры первого и второго операндов, регистр результата, сумматор, два коммутатора и дополнительный регистр, введены блок определения меньшего операнда и блок определения большего операнда, блок управления, третий коммутатор и вычитатель . Результат умножения представлен двоично — К вЂ” и записью.

2 ил.

1283750

Изобретение относится к вычислительной технике и может быть использовано в арифметико-логических устройствах, Целью изобретения является повышение быстродействия устройства.

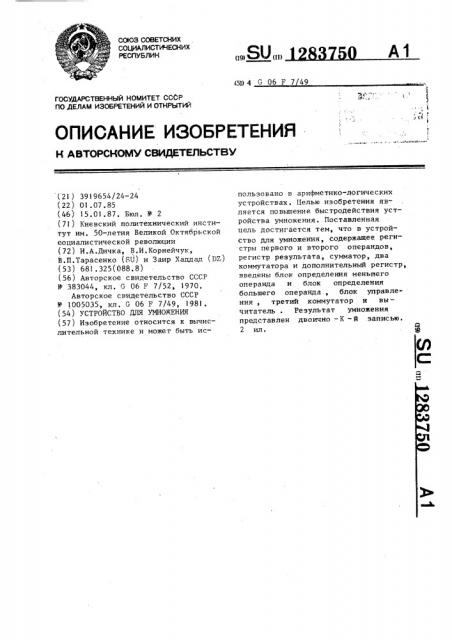

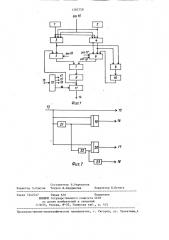

На фиг. 1 приведена структурная схема устройства; на фиг. 2 — блок управления, Устройство содержит регистр 1 10 множимого, регистр 2 множителя, блок

3 определения меньшего числа, блок

4 определения большего числа, первый 5 и второй 6 коммутаторы, сумматор 7, вычитатель 8, регистр 9 ре- 15 эультата, дополнительный регистр 10, третий коммутатор ll, блок 12 управления, вход 13 запуска, выход 14 результата, выходы 15 — 18 блока 12 управления. 20

Блок 12 управления содержит первый 19 и второй 20 RS-триггеры и первый, второй и третий элементы 21-23 задержки.

Блок 3 определения меньшего числа и блок 4 определения большего числа представляют собой схему сравнения кодов. Регистры 2 первого и второго сомножителей хранят и-разрядные двоичные числа. Сумматор 7-2п-разряд- 30 ный. Коммутатор 11 состоит из 2Пдвухвходових элементов И. Устройство осуществляет умножение двух чисел х и у в системе счисления с переменHbIM основанием k, т.е. формирует произведение z=jx yj„, Основание системы счисления выбирается равным 1смакс(х,у)+!, где макс (х; у) — больший из операндов х, у.Предположим, что х + у. Тогда: . 40

z = fx Л к = (X (k-1 )1 „= fkx-õ) „=

= fkx-x+k-К1, = fk(х-1 ) +(k-x)) „, Рассмотрим теперь выражение

Если рассматривать выражения (1) и (2) как запись чисел z u z в k-ой системе счисления, то легко заметить, что цифра числа z имеющая вес Х совпадает с цифрой числа z, имеюI ,щей вес k, а цифра числа z с весом совпадает с цифрой

I 1

coM k, Следовательно, произведение

Ф

1 х у1 в системе счисления с основанием k может быть получено в соответствии с выражением (2) с последу. = (x+y+k(y-x)3„= fx+y+ky-kx / „=

= jx+(k-1) +k(k-1) -kxj „+(k-x) +(x-1 юшей перестановкой цифр в k-й записи ! числа z

В устройстве вычисляется величина

I е = (х+у+К (y-х )j „= (мин +макс+К (мркс— мин )) „, где мин = нин (х,у) — меньший из операндов х, у, макс =макс x,y) . Если операн( ды х и у представлены в двоичном виt де, то z можно получить в двоичноk-ом виде:

f и

z =мин+Макс+2 (макс — мин )+D, и где D — коррекция, D=2 -k=2 -(макс+

+1)= макс(прибавление D обеспечивает получение результата по основанию k) т п — длина операндов, Тогда z, z будет представлять собой двоично-k-ю запись числа z результата умножения, Устройство умножения работает следующим образом.

По сигналу начала операпии, поступающего на вход 13 блока 12 управления, содержимое регистров первого и второго сомножителей поступают в блоки 3 и 4, где производится определение соответственно меньшего и большего чисел из участвующей в умножении пары операндов х и у. При этом триггеры !9-20 устанавливаются в состояние "1". Коммутатор 5 по сигналу с выхода 16 выдает на первый вход сумматора 7 меньший из операндов, а коммутатор 6 по сигналам

"!" "1" с выходов 16 и 17 — больший из операндов (прямой выход блока 4 определения большего операнда). Результат сложения мин +макс=х+у запоминается в 2п-разрядном регистре 9 результата, суммирование осуществляется по правилам двоичной арифмети— ки. Одновременно вичитатель 8 производит вычитание макс -мин, результат которого поступает в регистр 10.

Затем триггер 19 устанавливается в

"0", коммутатор 5 выдает в сумма— тор 7 содержимое регистра 9 результата, а коммутатор 6 по сигналу "0"

"1" с выходов !6 и 17 — содержимое регистра 10, причем содержимое регистра 10 выдается со сдвигом íà и разрядов влево (это осуществляется подачей кода в старшие разряды сумматора 7), Результат суммирования фиксируется в регистре 9 результата.

Затем триггер 20 устанавливается в

"0", и сумматор 7 осуществляет суммирование содержимого регистра 9 ре1 283750 зультата, выдаваемого коммутатором

5 по сигналу "0" с выхода 16 на первый вход сумматора 7, и величины макс, представляющей собой коррекции и выдаваемой коммутатором 6 по сигналам "0" "0" с выходов 16 и 17 с инверсного выхода блока 4 определения большего операнда, Результат и суммирования х+у+2 (ьакс -мин )+ макс поступает в регистр 9 результата. IO

По сигналу с выхода 18 блока 12 управления содержимое регистра 9 через коммутатор 11 поступает на выход 14 результата. Выдача содержимого ре— гистра 9 происходит таким образом, 15 что младшие и разрядов регистра становятся старшими разрядами, а старшие и разрядов регистра — младшими разрядами кода результата (выдача с перестановкой). 20

Формула изобретения

Устройство для умножения, содержащее регистры множимого, множителя и результата, два коммутатора, сум- 25 матор и дополнительный регистр, причем выход сумматора соединен с ин— формационным входом регистра реэуль— тата, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродейст— вия, в него введены блок определения больп|его числа, блок определения меньшего числа, третий коммутатор, вычитатель, блок управления, содержащий два RH триггера H три asIe 35 мента задержки, причем вход запуска устройства соединен с S-входами первого и второго RS-триггеров, входом первого элемента задержки и входами разрешения сравнения блоков опреде- 40 пения меньшего и большего чисел,первые и вторые информационные входы которых соединены соответственно с выходами регистров множимого и множителя, выход блока определения меньшеГ го числа соединен с первым информационным входом первого коммутатора и входом вычитаемого вычитателя,вход уменьшаемого которого соединен с прямым выходом блока определения большего числа и первым информационным входом второго коммутатора, второй информационный вход которого соединен с выходом дополнительного регистра, информационный вход которого соединен с выходом вычитателя, инверсный выход блока определения большего числа соединен с третьим информационным входом второго коммутатора, выход которого соединен с входом старших разрядов сумматора, вход младших разрядов которого соединен с выходом первого коммутатора, второй информационный вход которого соединен с выходом регистра результата и информационным входом третьего коммутатора, выход которого является выходом результата устройства, выход первого элемента задержки соединен с R-входом первого RS-триггера и входом второго элемента задержки, выход которого соединен с

R — входом второго RS-триггера и входом третьего элемента задержки, выход которого соединен с входом управления третьего коммутатора, выход первого RS-триггера соединен с входом управления первого коммутатора и первым входом управления второго коммутатора, второй вход управления которого соединен с вь1ходом второго

PS-триггера.

Составитель Н.Маркелова

Редактор Э.Слиган Техред Л.Сердюкова Корректор В.Бутяга

Заказ 7442/47 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, r, Ужгород, ул, Проектная,4