Устройство для вычисления суммы произведений

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники и может быть использовано в специализированных устройствах цифровой обработки информации . Устройство предназначено для вычисления суммы попарных произведений вида. Цепью изобретения является повьшение быстродействия. Поставленная цель достигается тем, что устройство, содержащее группу блоков прометку точных вычислений, каждый из которых содержит два регистра , сумматор и два элемента ИЛИj содержит многовходовой сумматор , регистры коэффициента и результата , а каждый блок промежуточных вычислений содержит дополнительно четыре группы мультиплексоров, квадратор и группу элементов запрета с соответствующими связями. 2 ил. о 9 (Л С

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

119) (11) (51) 4 G 06 F 7 544 15/347

OllHCAHHE ИЗОБРЕТЕНИЯ

Н АВТОРСНОМУ СВИДЕТЕЛЬСТВУ с

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3909038/24-24 (22) 11.06.85 (46) 15.01. 87. Бюл. Ф 2 (71) Киевский политехнический институт им. 50-летия Великой Октябрьской социалистической революции (72) В. И. Жабин, В. И, Корнейчук, В, В. Кротов, В. В, Макарон, В, П, Тарасенко и В, В. Ткаченко (53) 681.325(088.8) (56) Авторское свидетельство СССР

В 1072039, кл, G 06 F 7 49, 1981.

Авторское свидетельство СССР

11- 788105, кл. G 06 F. 7/38, 1976. (54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ СУММЫ

ПРОИЗВЕДЕНИЙ (57) Изобретение относится к области вычислительной техники и может быть использовано в специализированных устройствах цифровой обработки информации. Устройство предназначено

1 для вычисления суммы попарных произведений вида. Целью изобретения является повыщение быстродействия.

Поставленная цель достигается тем, что устройство, содержащее группу блоков промежуточных вычислений, каждай из которых содержит два регистра, сумматор и два элемента

ИЛИ; содержит многовходовой сумматор, регистры коэффициента и результата, а каждый блок промежуточных вычислений содержит дополнительно четыре группы мультиплексоров, квадратор и группу элементов запрета с соответствующими связями. 2 ил, 1283754 и 2 где K--,2 :, Х - .

,.1

Устройство для вычисления суммы произведений работает следующим образомм.

При наличии Х,...,, Х и на входах IS по сигналу на входе 13 информация через мультиплексоры 2 записывается в регистры 7 каждого блока 1 соответственно, После этого по сигналу на входе 14 мультиплексоры 11 создают цепь, по которой информация с выхода регистров 7 поступает на входы квадраторов 10 соответственно.

С их выходов квадраты поступивших .величин поступают через мультиплекS5

Изобретение относится к области вычислительной техники и может быть использовано в арифметических устройствах цифровых вычислительных машин °

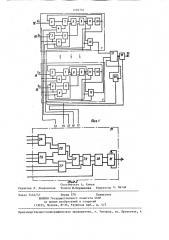

Цель изобретения — повышение быст- 5 родействия, На фиr. 1 представлена структурная схема устройства для вычисления суммы произведений; на фиг, 2 — схема многовходового сумматора (при

n=S; п " количество пар сомножителей).

Устройство для вычисления суммы произведений состоит из группы блоков 1 промежуточных вычислений, каждый из которых содержит группы мультиплексоров 2 и 3, элементы ИЛИ 4 и 5, регистры 6 и 7, группу элементов 8 запрета, сумматор 9, квадратор

10 и группы мультиплексоров 11 и 12, установочного входа 13, тактовых входов 14 — 17, групп информационных входов 18 и 19, регистра 20 коэффициента, многовходовоro сумматора 21, регистра 22 результата и выход 23 устройства.

Многоразрядный сумматор 21 содержит сумматоры 24 — 30 с сохранением переносов и сумматор 31 с распро"

30 странением переносов, Квадраторы 10 могут быть реализованы на ПЗУ.

Устройство для вычисления суммы произведений значение и

Z= «Х;У; 1 определяет согласно следующей формуле

Т> 2 2. 40

<х +т,) — Y;) -

7-1

У

2 сары 12 на сумматор 21, где npoucz ходит . сложение Х, И по заднему фронту сигнала на входе 14 устройства сумма запись)вается в регистр

20 коэффициента, Таким образом, за один такт прои сходит вычи сление и запись величины К. После вычисления

К при наличии на информационных входах 19 Y< ...,, .< „по сигналу на входе 13 происходит запись значений через мультиплексоры 3 в регистры 6 блоков 1 соответственно, После этого по сигналу на входе 15 на сумматорах 9 происходит алгебраическое сложение величин, которые хранились в регистрах 6 и 7 каждого блока 1, Полученные на сумматорах 9 значения сумм поступают через. соответствующие мультиплексоры 11 на входы квадраторов 10, где вычисля2 ются значения (Х;,+Y; ), Полученные результаты с выходов квадраторов

10 заносятся в соответствующие регистры 7 по заднему фронту сигнала на входе 15 устройства, В следующем такте по сигналу на входе 16 устройства закрываются элеменTbl 8 запрета, Информация, хранимая в регистрах 6, поступает через соответствующие сумматоры 9 (суммируясь с нулем) и мультиплексоры 11 на входы квадра Z торов 10. С их выходов значения Y через мультиплексоры 3 соответственно записываются в регистры 6 по заднему фронту сигнала на входе 16 в обратном коде.

В следующем такте (сигнал на входе 17) на сумматорах 9 складывается содержимое первых и вторых регистров

6 и 7 и результаты суммирования (Х ° +Y,) "Y через мультиплексоры 12

1 1 1 поступают на входы многоразрядного сумматора 21, где суммируются с ве- личиной -К, поступающей с инверсного выхода регистра 20 коэффициента.

По заднему фронту сигнала на входе

17 устройства результат вычислений заносится со сдвигом на один разряд вправо в регистр 22 результата, с которого поступает на выход 23 устройства, Формула изобретения

Устройство для вычисления суммы произведений, содержащее группу блоков промежуточных вычислений, каждый из которых содержит два регистра, I 283754 сумматор и два элемента ИЛИ, причем выход первого регистра соединен с входом первого слагаемого сумматора, о т л и ч а ю щ е,е с я тем, что, с целью повышения быстродействия, оно содержит многовходовый сумматор, регистр коэффициента, регистр результата, а каждый блок промежуточных вычислений группы содержит дополнительно квадратор, группу элементов запрета и четыре группы мультиплексоров, причем установочный вход устройства соединен с первыми входами первого и второго элементов ИЛИ и управляющими входами мультиплексоров первой и второй групп каждого блока промежуточных вычислений группы, первый тактовый вход устройства соединен с входом разрешения приема регистра коэффициента.и управляющими 20 входами мультиплексоров третьей и четвертой групп каждого блока промежуточных вычислений группы, второй и третий тактовые входы устройства соединены соответственно со вторыми входами первого и второго элементов ИЛИ каждого блока промежуточных вычислений группы, четвертый тактовый вход устройства соединен с входом разрешения приема регистра ре- ЗО эультата, выход которого является выходом устройства, информационные входы первой и второй групп устройства соединены соответственно с первыми информационными входами муль- 35 типлексоров первой и второй групп соответственно блока промежуточных вычислений группы, выходы мультиплексоров четвертой группы блоков промежуточных вычислений группы и инверсный выход регистра коэффициента соединены соответственно с входами слагаемых многовходового сумматора, выход которого соединен с информационным входом регистра коэффициента и со сдвигом на один разряд вправо с информационным входом регистра результата, а также в каждом блоке промежуточных вычислений группы выходы мультиплексоров первой и второй групп соединены соответственно с информационными входами второго и первого регистров, входы разрешения приема которых соединены соответственно с выходами первого и второго элементов ИЛИ, второй вход второго элемента ИЛИ соединен с управляющими входами элементов запрета группы, информационные входы которых соединены с выходом второго регистра и первыми информационными входами мультиплексоров третьей группы, выходы которых соединены с входом квадратора, выход которого соединен с вторыми информационными входами мультиплексоров первой группы, инверсными вторыми информационными входами мультиплексоров второй группы и первыми информационными входами мультиплексоров четвертой группы, вторые информационные входы которых соединены с вторыми ифнормационными входами мультиплексоров третьей группы и выходом сумматора, вход второго слагаемого которого соединен с выходами элементов запрета группы.

1283754

Ц 14 15 f6 17

Cps/М,Л

Составитель A. Клюев

Редактор Л, Пчелинская Техред Л.Сердюкова Корректор Л

Заказ 7442/47 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д, 4/5

Производственно-полиграФическое предприятие, r. Ужгород, ул, Проектная, 4