Вычислительное устройство

Иллюстрации

Показать всеРеферат

Изобретение может быть применено автономно в специализированных вычислителях или в составе больших ЭВМ в качестве функциональных расширителей арифметических операций. Целью изобретения является расширение класса решаемых задач за.счет возможности вычислений значений квадратного корня, прямых и обратных тригонометрических функций. Устройство содержит тригонометрический преобразователь 1, регистр аргумента 6, буферный регистр 9, первый сумматор 2, второй сумматор 3, блок деления 4, группу элементов ИЛИ 5, первую группу элементов И 10, вторую группу элементов И 11, умножитель 7, блок управления 8. Вычисление основано на итерационном процессе вычисления обратного косинуса и синуса в блоке 1 и использовании известного соотношения для вычисления квадратного корня, 2 ил. Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК др 4 С 06 Р 7/544

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3918769/24 — 24 (22) 28,06.85 (46) 15.01,87. Бюл. Ф 2 (72) Л. П, Лобанов, П. Б, Пучков, В. А. Терсков и Г. С. Тимофеев

° ° ° ° °

53) 681. 325 (088. 8)

56) Авторское свидетельство СССР

11 832555, кл, G 06 F 7/548, 1980.

Авторское свидетельство СССР

Ф 1062692, кл. G 06 F 7/552, 1982.

Устройство для извлечения квадратного корня с помощью значений синусов, хранящихся в блоке памяти.

Электроника, 1975, Р 23, с. 62-63. (54) ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО (57) Изобретение может быть применено автономно в специализированных вычислителях или в составе больших

ЭВМ в качестве функциональных расширителей арифметических операций, Целью изобретения является расширение класса решаемых задач за счет возможности вычислений значений квадратного корня, прямых и обратных тригонометрических функций, Устройство содержит тригонометрический преобразователь 1, регистр аргумента 6, буферный регистр 9, первый сумматор 2, второй сумматор 3, блок деления 4, группу элементов ИЛИ 5, первую группу элементов И 10, вторую группу элементов И 11 умножитель 7, блок управления 8. Вычисление основано на итерационном процессе вычисления обратного косинуса и синуса в блоке 1 и использовании известного соотношения для вычисления квадратного корня, 2 ил.

l а

2 2

11- е.1

2 агссоз а

2 2

-З0 деления производится вычисление косинуса угла

У=1а=(- + -)здп

2 2!

1 — aI

1 12837

Изобретение относится к вычислительной технике и может быть исполь" зовано как автономно, так и в состаВе больших ЭВМ в качестве функциональных расширителей арифметических операций.

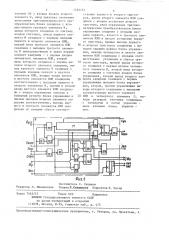

Цель изобретения — расширение класса решаемых задач путем обеспечения возможности вычисления значений квадратного корня, прямых и об- 10 ратных тригонометрических функций, На фиг. 1 представлена функциональная схема устройства; на фиг, 2функциональная схема блока управления, 15

Вычислительное устройство содержит тригонометрический преобразователь 1, первый 2 и второй 3 сумматоры, блок 4 деления, группу элементов

ИЛИ 5, регистр 6 аргумента, умножи- 20 тель 7, блок 8 управления, буферный регистр 9, первую 10 и вторую 11 группы элементов И.

Блок 8 управления образуют шесть элементов ИЛИ 12,1 — 12,6, "три триггера 13.1 - 13.3, счетчик 14, четыре элемента И 15,1 — 15.4, элементы 16 и 17 задержки и элемент НЕ 18, Устройство реализует выражение: тригонометрического преобразователя

1, настраивая его на вычисление обратных -три гонометрических функций, С регистра 6 обратный код аргумента а поступает на вход первого

cqaraeMoro сумматора 2, а код аргумента а сдвинутый на один разряд впр аво, поступает на вход первого слагаемого сумматора 3, По сигналу с первого тактирующего выхода блока 8 управления в сумматоре 2 обратный код числа ja) „Бр преобразуется в дополнительный код путем сложения (а) с единицей младшего

n-ro разряда (1- a =faj „=) ) +2

Во втором сумматоре 3 вычисляется выражение:

В первом сумматоре 2 результат со сдвигом на один разряд вправо, !

1-а/ т.е. ††вЂ, подается на вход делимого блока 4 деления, на вход делителя которого подается результат с второго сумматора 3 ° В блоке 4

Устройство работает следующим . образом.

В начальный момент времени на вход задания режима блока 8 подается код единицы, устанавливающий режим вычисления квадратного корня, на входы вторых. слагаемых сумматоров 3 и 2 подаются соответственно коды единицы младшего и-го и старшего первого разряда, в тригонометрическом преобразователе осуществляются начальные установки, на вход блока 8 управления и стробирующий вход регистра 6 аргумента поступает сигнал "Пуск", По этому сигналу в регистр 6 аргумента производится запись аргумента а и в блоке 8 управления происходит отключение входа (тактового) блока 8 управления от аналогичного входа (тактового) тригонометрического преобразователя 1 на время выполнения дперации сложения и деления, а также производится переключение триггеров

l3,1 и 13.2, управляющих работой

2 созМ = — — —— а

2 2 результат которого через группу элементов ИЛИ 5 по команде с второго тактирующего выхода блока 8 управления записывается в буферный регистр 9. К тригонометрическому преобразователю 1 подключается тактовый вход устройства„ В преобразова-. теле 1 производится вычисление ве4 5 личины

/1- — a I

c6 = arccos — — ——

1 а

2 2

50 за пятнадцать тактов, С приходом шестнадцатого импульса в блок 8 управленя выдается сигнал окончания вычислений, в соответствии с которым происходит отключение тактового входа от тригонометрического преобразователя на время передачи кода <6 в буферный регистр 9 через группу элементов И 10 по команде с четвертого

1283755 вымя входами элементов ИЛИ группы, вторые входы которых соединены с входами аргумента тригонометрической функции устройства, выходы элементов ИЛИ группы соединены с информационными входами буферного регистра, выходы которого соединены с входами аргумента тригонометрического преобразователя, выходы значения обратной функции которого соединены с первыми входами элементов И первой группы и выходом значения обратной функции устройства, выходы элементов И первой группы соединены с третьими входами элементов ИЛИ группы, выход значения прямой функции тригонометрического преобразователя соединен с одноименным выходом уст" ройства и первыми входами элементов

И второй группы, выходы которых соединены с входом второго сомножителя умножителя, выход которого соединен с выходом значения квадратного корня устройства, стробирующие входы первого и второго сумматоров, буферного регистра, тригонометрического преобразователя, элементов

И первой и второй групп соединены с упр авляющими выходами блока управлеФ о р м у л а и з о б р е т е н и я З0 ния с первого по пятый соответственно, выход задания режима блока управления соединен с одноименным входом тригонометрического преобразователя, вход запуска устройства соединен с входом разрешения записи регистра аргумента и входом запуска блока управления, тактовый вход устройства, входы задания режима, упр авления, тригонометрическим преобразователем, управления записью в буферный регистр устройства соедине" входном третьего элемента И и через тактирующе го выхода блока 8 управления, а т акже о суще ствля ется пер еключение каналов коммутатора в тригонометрическом преобразователе 1 на вычисление прямых тригонометрических функций, При подключении тактового

l входа в тригонометрическом, преобразователе 1 происходит вычисление величины s n g з а пятнадцать тактов, С приходом шестнадцатого импульса тактовый вход тригонометрического преобразователя 1 отключается и с пятого тактирующего выхода блока 8 управления на вход второй группы элементов И 11 по ступает си гнал, 15 по которому на первый вход умножителя 7 поступает код sineL а на с второй вход — значение — + — с вто2 2 рого сумматора 3, На выходе умножителя 7 формируется результат вычисления квадратного корня по формуле (I), При вычислении тригонометрических функций на вход заданий блока 8 управления подается сигнал нуля и работа тригонометрического преобразователя 1 происходит автономно.

Вычислительное устройство, содержащее регистр аргумента, первый сумматор, блок деления, умножитель, причем вход аргумента устройства соеди- 35 нен с информационным входом регистра аргумента, выход которого соединен с входом первого слагаемого первого сумматора, выход которого соединен с входом делимого блока деления, 40 о т л и ч а ю щ е е с я тем, что, с целью расширения класса решаемых задач путем обеспечения возможности вычисления значений квадратного корня, прямых и обратных тригонометри- 45 ческих функций, в него дополнительно введены второй сумматор, буферный регистр, группа элементов ИЛИ, две группы элементов И, тригонометрический преобразователь и блок уп- 50 равления, причем разрядные выходы регистра аргумента соединены со сдвигом на один разряд в сторону младших разрядов с входами первого слагаемого второго сумматора, выход которого соединен с входом первого сомножителя умножителя и входом делителя блока деления, выходы частного блока деления соединены с перны с одноименными входами блока управления, первый и второй входы коррекции аргумента устройства соединены с входами вторых слагаемых первого и второго сумматоров, выход признака окончания вычисления тригонометрического преобразователя соединен с одноименным входом блока управления, содержащего счетчик, три триггера, шесть элементов ИЛИ, четыре элемента И, элемент НЕ, два элемента задержки, причем вход запуска блока управления соединен с первыми входами первого и второго элементов И, вход задания режима блока управления соединен с вторым входом первого элемента И, первым

1283755

Составитель С, Куликов

Редактор Л, Пчелинская Техред Л.Сердюкова Корректор Л. Патай

Заказ 7442/47 Тираж 670 Подпи сно е

ВНИИПИ Госуцарственного комитета СССР по делам изобретений и открытий

113035, Москва, 3(-35, Раушская наб., д, 4/5

Производственно-голиграфическое предприятие, г. Ужгород, ул. Проектная, 4 элемент HE c вторым входом второго элемента И, вход признака окончания вычисления тригонометрического преобразователя блока соединен с вторым входом третьего элемента И, выход которого соединен со счетным входом счетчика выхоц первого элемента И соединен с первыми входами первого и второго элементов ИЛИ, первый вход третьего элемента ИЛИ соединен с выходом третьего элемента И непосредственно и через первый элемент задержки — с первым входом четвертого элемента NJTH второй вход которого соединен с первым выходом второго элемента задержки„ выход третьего элемента И соединен с первыьж входами первого и шестого элементов ИЛИ, вторые входы пятого и шестого элементов ИЛИ соединены соответственно с выходами первого и второго элементов И, третий и второй входы шестого элемента ИЛИ соединены с входом управления записью в буферный регистр блока управления и первым выходом второго элемента задержки соответственно, выходы первого и третьего элементов ИЛИ соединены со входами сброса соответственно первого и второго триггеров, выход второго элемента ИЛИ соединен с входом установки второго триггера, вход управления тригонометрическим преобразователем блока управления соединен с вторыми вхо-. дами первого, второго и третьего элементов ИЛИ и входом установки первого триггера, прямые выходы первого 0 и второго триггеров соединены с выходом задания режима блока управления, выходы четвертого и пятого элементов ИЛИ соединены с входами соответственно установки и сброса третьего триггера, прямой выход которого соединен с первым входом четвертого элемента И, второй вход которого соединен с тактовым входом блока управления, второй выход второго элемента задержки соединен с первым управляющим выходом блока управления, второй, третий управляющие выходы которого соединены с выходами соответственно шестого элемента

25 ИЛИ и четвертого элемента И, выходы разрядов счетчика соединены с четвертым и пятым управляю щими входами блока управле ния.