Логический анализатор

Иллюстрации

Показать всеРеферат

Изобретение относится к области .вычислительной техники, а именно к устройствам контроля и диагностики ЭВМ. Цель изобретения - расширение области применения. Сущность изобретения состоит в том, что в известное устройство, содержащее генератор тактовых импульсов, регистр, первый, второй, третий счетчики, блок памяти , элемент НЕ, элемент И и элемент задержки, дополнительно введены мультиплексор, делитель частоты, D- триггер, два элемента И-НЕ, элемент И, формирователь импульсов, элемент ИЛИ и три элемента задержки. 4 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1 (5р 4 G 06 F 11/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3941255/24-24 (22) 31.07.85 (46) 15.01.87. Бюл. 9 2 (72) А.Н .Бучнев, Е .И.Карпунин и В.И.Песоченко (53) 661.3 (088.8) (56) Авторское свидетельство СССР

В 608126, кл. С 05 В 23/02, 1978.

Патент США Р 4373193, г кл. G 06 F 3/05, 1983. (54) ЛОГИЧЕСКИЙ АНАЛИЗАТОР (57) Изобретение относится к области вычислительной техники, а именно к

„„Я0„„12 771 устройствам контроля и диагностики

ЗВИ. Цель изобретения — распирение области применения. Сущность изобретения состоит в том, что в известное устройство, содержащее генератор тактовых импульсов, регистр, первый, второй, третий счетчики, блок памяти, элемент НЕ, элемент И и элемент задержки, дополнительно введены мультиплексор, делитель частоты, Dтриггер, два элемента И-НЕ, элемент

И, формирователь импульсов, элемент

ИЛИ и три элемента задержки. 4 ил.

1 283771 2

Изобретение относится к вычислительной технике, а именно к устройствам контроля и диагностики ЭВИ.

Цель изобретения — расширение области применения путем обеспечения возможности анализа информации с асинхронным периодом поступления.

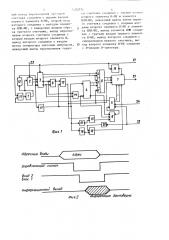

На фиг.1 приведена блок-схема устройства для логического анализа; на фиг,2 — временная диаграмма считывания накопленной в устройстве информации; на фиг.3 — временная диаграмма работы устройства в режиме сбора информации; на фиг. 4— формат представления информации в блоке памя ти .

Устройство содержит генератор 1 тактовых импульсов, регистр 2 сдвига, счетчики 3-5, коммутатор 6, блок 7 памяти, элементы И-НЕ 8 и 9, элементы И 10 и 11, делитель 12 частоты, элемент ИЛИ 13, элемент ИПИНЕ 14, 0-триггер 15, элемент НЕ 16, элементы 17-20 задержки, вход 21 задания режима работы, информационный вход 22, вход 23 пуска, адресные входы 24 и выходы 25 устройства.

Устройство работает следующим образом.

В зависимости от значения сигнала режима работы на входе 21 различаются два режима работы устройства: сбор поступающей с объекта информации; — анализ накопленной информации °

Переход сигнала режима работы на входе 21 из состояния "0" в состояние "1" означает сбор информации устройством. Устройство работает в режиме сбора поступающей с входа 22 через регистр 2 сдвига информации и ее запоминания в блоке 7 памяти до наступления момента переполнения и до момента отключения действия сигнала режима работы. Наличие сигнала переполнения с инверсного выхода счетчика 5 и "0" на входе 21 блокируют работу генератора 1 тактовых импульсов через элемент И 11.

Работа устройства в режиме сбора поступающей с объекта информации поясняется временной диаграммой на фиг.3 ° После запуска генератор 1 тактовых импульсов вырабатывает синхросигнал, который сдвигает поступающую входную информацию в регистре 2 и является входным сигнаf0

35 лом для делителя 12 частоты. Накоп— ленная в регистре 2 сдвига информация переписывается в счетчик 3 фрон— том сигнала, поступающего с делителя 12 частоты. В зависимости от переписанной в первый счетчик информации различаются два формата записи (сброса) информации: — формат 0 константы типа "0"

1 константы типа "1" — формат 1 смешанной информации. °

Форма заполнения блока 7 памяти информацией, поступающей с входа у стр ой ств а, прив едена на фиг. 4.

При записи информации в формате 0 возможны два варианта: счетчик 3 заполнен по всем разрядам "0 и "1", Эти два варианта отличаются друг от друга тем, что в (1+1)-й разряд блока памяти 7 (1 — длина массива анализируемой информации) заносится признак наличия "0" и "1", т.е. признак константы. Присутствие низкого уровня на одном из входов элемента И-HE 8 поддерживает высокий уровень на D-входе D-триггера 15, который по фронту сигнала с выхода делителя 12 частоты через элемент

17 задержки ставит триггер 15 в "1".

Значение сигнала с выхода D-триггера 15 записывается в (1+2)-й разряд блока памяти 7. Сигнал "1" на выходе D-триггера 15 блокирует про— хождение стробирующего сигнала через элемент ИЛИ 13 и переводит ком— мутатор 6 в состояние коммутации выходов счетчика 4 на информационные

1 входы блока 7 памяти. Элемент ИЛИНЕ 14 с динамическими входами отслеживает появление фронта сигнала, переход из состояния "1" в состояние

"0" на любом из его входов и формирует сигнал низкого уровня, который обнуляет счетчик 4 и через элемент

И-HE 9 поступает на тактирующий вход счетчика 5 и прибавляет единицу.

Элемент ИЛИ вЂ 14 исключает запись в блок памяти по одному и тому же адресу при сборе инфорьации формата

0 отличающихся значений констант в каждом собранном такте. При длительном сборе сигнала типа "константа 0" или "константа 1" значение счетчика

5 остается неизменным, а значение счетчика 40,подсчитывающего число тактов присутствия константы меняется. Таким образом, информация с выхода счетчика 4 записывается в одну

3 1 я «-йку блок» 7 памяти до тех пор, пока нс произойдет переполнения этого счетчика 4, сигнал с выхода переполнения которого прибавляет 1 к значению счетчика 5, получив новый адрес следующей ячейки блока памяти

7. Вход записи блока памяТи в режиме сбора поступающей информации находится в состоянии "0, вход записи которого согласно временной диаграмме на фиг.3 обрабатывает процедуру записи. Элемент 19 задержки с инвер— сией необходим для компенсации времени срабатывания элементов И-HE 9, счетчика 5 и элемента ИЛИ-НЕ с динамическими входами.

При записи поступающей с объекта информации в формате 1 в счетчик 3 переписывается смешанная информация.

В результате на выходах счетчика 3 присутствуют сигналы 1". Таким образом, 0-триггер первым тактирующим сигналом устанавливается в значение

"0", сигнал с которого переключает коммутатор 6 иа трансляцию информации с выходов счетчика 3 на информационную группу входов блока 7 памяти, по информационному входу которого записывается "О" — признак формата-1. Сигнал "О" на входе элемента

ИЛИ 13 разрешает прохождение сигнала на вход элемента И-HE 9, с выхода которого сигнал йоступает на вход счета счетчика 5, который прибавляет единицу к текущему адресу и т.д.

Элементы 17 задержки и элементы 18 и 19 задержки с инверсией необходимы для устойчивой безошибочной работы устройства в режиме сбора информации с объекта диагностирования.

При поступлении на вход 21 сигнала

"0" устройство переходит в режим анализа накопленной в блоке памяти

7 информации. Считывание и анализ накопленной информации осуществляется согласно временной диаграмме, представленной на фиг.2.

Формирование информации, записываемой в память 7, позволяет анализировать большие массивы поступающей информации, не снижая частоты ее сканирования.

2837/! 4

Логический щнй генератор гистр сдвига, мяти, элемент анализатор, содержатактовых импульсов, ретри счетчика, блок паНЕ, первый элемент И, Формула изобретения

f5

55 пер вый элемент 3 «держки прн чем «ит ход первого элемента задержки гоев динен с первым входом первого элемента И, выхоц генератора тактовых импульсов соединен с синхровходом регистра сдвига, информационный вход которого является информационным входом анализатора, группа выходов регистра соединена с группой информационных входов первого счетчика, адресные входы анализатора соединены с информационными входами второго счетчика, группа разрядных выходов которого соединена с адресной группой входов блока памяти, выходы которого являются выходами анализатора, вход задания режима которого соединен через элемент НЕ с входом записи блока памяти, вход синхронизации которого соединен с выходом первого элемента И, вход пуска анализатора соединен с входом записи второго счетчика и входом первого элемента задержки, о т л И ч а ю щ и и с я тем, что, с целью расширения области применения путем обеспечения возможности анализа информации с асинхронным периодом поступления, анализатор содержит коммутатор, делитель частоты, D-триггер, два элемента И-.НЕ, второй элемент И, элемент ИЛИ-НЕ, элемент ИЛИ, второй, третий .и четвертый элементы задержки, причем выход генератора .тактовых импульсов соединен с входом делителя частоты, выход которого соединен с входом записи первого счетчика и через второй элемент задержки с синхровходом D-триггера, синхровходом третьего счетчика и входами тре— тьего н четвертого элементов задержки, инверсные выходы которых соединены с первым входом элемента ИЛИ и вторым входом первого элемента И, выход В-триггера соединен с управляющим входом коммутатора, вторым вхо- .. дом элемента ИЛИ и информационным входом блока памяти, информационные входы которого соединены с выходами коммутатора, первая группа информационных входов которого соединена с группой разрядных выходов первого счетчика, вторая группа информацион- ных входов коммутатора соединена с разрядными выходами третьего счетчика и выходом старшего разряда первого счетчика, вход записи первого счетчика соединен с входом задания режима работы анализатора, инверс21

Адресиые

9лраЬяющ бХОд 2 блОК 7

ИнфО)0мОЦиО

Фый В11х од пере . )н J! еI "н%} я IB е . т fзе! о счетчика соединеH с первым входом первого элемента И-НЕ, второй вход которого соединен с выходом элемента ИЛИ-НЕ, с инверсным входом сброса третьего счетчика, выход переполнения второго счетчика соединен с вторым входом второго элемента И, выход которого соединен с входом пуска генератора тактовых импульсов, инверсный выход переполнения ервого счетчика соединен с первым нходо 1 второгс элемента И-НЕ и элемента

ИЛИ-НЕ, инверсный выход заема первого счетчика соединен с вторыми входами второго элемента И-НЕ и элемента ИЛИ-НЕ, выход элемента ИЛИ соединен с третьим входом первого элемента И-НЕ, выход которого соединен с синхровходом первого счетчика, вы10 ход второго элемента И-НЕ соединен с D-входом D-триггера.

1283771

Запуск РР

Вьио

Нь7ход Penumenz аслоты

Второ

Ин<р. Ухоить! Юл. 7

Инцюрмация достоберна

Фиг.З

1 е ° ° ° в ° ° К

° ° ° ° °

2 7

Формапг ° Значение Число такто6 константы при ФО.константы Значение сигнава при Ф1

Фиг. Ф

Составитель А. Сиротская

Редактор Л. Пчолинская Техред Л.Олейник Корректор Н. Король

Заказ 7443/48 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, . Ужгород, ул. Проектная, 4