Устройство для сопряжения цвм с памятью

Иллюстрации

Показать всеРеферат

Изобретение относится к области вычислительной техники в частности к устройствам сопряжения магистрального типа и может быть испальзовано для построения вычислительного комплекса со значительным объемом памяти . Целью изобретения является увеличение быстродействия. Устройство содержит компаратор адреса, компаратор . данных, элементы И-НЕ, триггер, блок памяти, регистры, блок элементов И, ЦВМ. 1 ил.

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИН (5D 4 G 06 F 13/00

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3910188/24-24 (22) 10.06.85 (46) 15.01.87. Бюл. 11- 2 (72) В.Н. Алешин и А.Н, Пресняков (53) 681.3 (088.8) (56) Авторское свидетельство СССР

У 881722, кл. G 06 F 3/04, 198i

Центральный процессор В 2. Техническое описание и инструкция по эксплуатации. 3.858.382ТО, 1982, с. 49, 199-202.

„.80„„12837?6 А1 (54) УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВИ

С ПАМЯТЬЮ (57) Изобретение относится к области вычислительной техники в частности к устройствам сопряжения магистрального типа и может быть использовано для построения вычислительного комплекса со значительным объемом памяти. Целью изобретения является увеличение быстродействия. Устройство содержит компаратор адреса, компаратор . данных, элементы -HE, триггер, блок памяти, регистры, блок элементов И, ЦВИ. 1 ил.

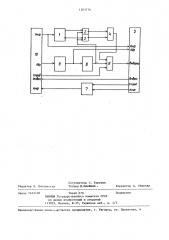

Единичный уровень с выхода триггера разрешает прохождение управляющих сигналов ЦВМ на блок памяти, т.е. осуществляется обращение к памяти.

1 12837 .Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения магистраль.ного тина, и может быть использовано для построения вычислительного 5 комплекса со значительным объемом памяти.

Цель изобретения — увеличение быстродействия устройства.

На чертеже представлена блок-схе- fo ма устройства.

Устройство содержит компаратор 1 данных, первый 2 и второй 3 элементы

И-НЕ, триггер 4, блок 5 памяти, первый 6 и второй 7 регистры, компаратор 8 адреса, блок 9 элементов И и

ЦВМ 10.

Устройство работает следующим образом.

В адресном цикле ЦВМ на шине адре- ZO са выставляет адрес, который запоминается в первом регистре 6 и, сравниваясь на компараторе 6 адреса с хранящимся в нем кодом, открывает элементы И-HE 2 и 3 (в случае совпадения), устанавливая на их вторых входах положительный потенциал. Затем в цикле вывода данных ЦВМ выставляет на своем информационном выходе двоичный код номера блока памяти, который сравнивается с заданным кодом на компараторе 1 данных. В случае совпадения на прямом выходе компаратора

1 появляется положительный потенциал, который -устанавливает, в единичное 35 состояние триггер 4, а в случае несовпадения сбрасывает его в нулевое состояние, активизируя сигнал на своем инверсном выходе, т.е. при наличии п блоков памяти, имеющих ана- 4О логичную схему сопряжения, всегда установлен только один триггер, а триггеры остальных блоков сброшены в нулевое состояние, 76 ? формула изобретения

Устройство для сопряжения ЦВМ с памятью, содержащее первый, второй регистры, компаратор адреса, триггер и блок элементов И, причем вход устройства для подключения информационно о выхода ЦВМ соединен с информационным входом блока памяти, адресный вход устройства соединен с входом первого регистра, выход которого подключен к входу компаратора адреса и к адресному входу блока памяти, стробирующнй вход устройства для подключения к управляющему выходу

IIBM соединен с входом синхронизации первого регистра И с первым входом блока элементов И, выход компаратора адреса подключен к второму входу блока элементов И, выход которого соединен с входом считывания блока памяти, выход строба данных и информационный выход которого соединен соответственно с синхронизирующим и информационным входами второго регистра, выход которого соединен с информационным выходом устройства для подключения к информационному входу

ЦВМ, управляющий выход устройства для подключения к входу подтверждения чтения-записи ЦВМ (: соединен с одноименным выходом блока памяти, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродействия устройства, в него введены компаратор данных и первый и второй элементы И-НЕ, причем информационный вход устройства для подключения к информационному выходу ЦВМ соединен с входом компаратора данных, прямой и инверсный выходы которого подключены к первым входам соответственно первого и второго элементов И-НЕ, вторые входы которых соединены с выходом компаратора адреса, выходы первого, второго элементов И-НЕ соединены с единичным и нулевым входамитриггера, выход которого соединен с третьим входом блока элементов И-.

1283?76

Составитель С. Бурухин

Техред Л.ОлейникРедактор Л. Пчолинскай

Корректор А. Обручар

Заказ 7443/48

Тираж 670

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д. 4/5

Подписное

Производственно-поли у, фпческое предприятие, г. Ужгород, ул. Проектная, 4