Синусно-косинусный преобразователь

Иллюстрации

Показать всеРеферат

Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования информации. Цель изобретения упрощение и првьппение разрешающей способности.преобразования. Преобразователь содержит два переключателя , регистр кода аргумента, селектор октанта, два преобразователя прямого кода в дополнительный, два блока постоянной памяти, два умножающих дифроаналоговых преобразователя, выходной коммутирующий блок. Селектор содержит трехразрядный блок слежения с единицей и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ. За счет инвертирования преобразуемого напряжения, изменения кодов с прямого на дополнительный и переключения выходных каналов формируются синусная и косинусная зависимости на полном периоде изменения аргумента при хранеш и в блоках постоянной памяти ординат синуса и косинуса в пределах первого октанта 1. ил. сл

СОЮЗ СОВЕТСНИХ

СОЦИАЛИСТИЧЕСНИХ

РЕСПУБЛИН

А1 (бд ф G 06 G 7/22

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ (21) 3862452/24-24 (22) 28.02.85 (46) 15.01.87. Бюл. 9 2 (72) В.Ф. Белов, В . Г. Домр ачев, И.Н.Мазов, Б.С Лейко и А.Н.Щавелкин (53) 681. 3 (088. 8) (56) Автор ское свидетель "тво СССР

У 1089588, кл. G 06 G 7/22, 1982.

Авторское свидетельство СССР

11 1183989, кл. G 06 G 7/22, 1984. (54) СИНУСНО-КОСИНУСНЫЙ ПРЕОБРАЗОВАТЕЛЬ (57) Изобретение относится к вычислительной технике и может быть использовано в устройствах преобра- . зования информации. Цель изобретенияупрощение и повышение разрешающей слособности.преобразования. Преоб„.SU„„1283804 разователь содержит два переключателя, регистр кода аргумента, селектор октанта, два преобразователя прямого кода в дополнительный, два блока постоянной памяти, два умножающих цифроаналоговых преобразователя, выходной коммутирующий блок. Селектор содержит трехразрядный блок слежения с единицей и элемент ИСКЛЮЧАЮЩЕЕ

ИЛИ. За счет инвертирования преобразуемого напряжения, изменения кодов с прямого на дополнительный и переключения вь1ходиых каналов формируются синусная и косинусная зависимости на полном периоде изменения аргумента при хранении в блоках Й постоянной памяти ординат синуса и косинуса в пределах первого октанта °

1. ил. С::

В таблице приведены значения управляющих сигналон в зависимости от номера октанта (кода трех стар— ших раэрядон регистра 3).

В таблице римскими цифрами обоз— начены старшие разряды регистра 3, Ф1 и Ф2 — управляющие входы первого и второго 2 переключателей соответственно, К вЂ” упранляюший вход выходного переключающего блока, С1 и С2 управляющие входы первого 5 и второго 6 преобразонателей прямого кода в дополнительный.

Ф о р м у л а и з о б р е т е н и я

Сину сно-косинусный преобразователь, содержащий регистр кода аргумента, информационный вход которого является входом преобразователя, а вход записи соединен с синхронизирующим входом преобразователя, выходы трех старших разрядов регистра соединены с входами селектора октанта, дна умножающих цифроаналоговых преобразователя, дна блока постоянной памяти, первый и второй переключатели, отличающийся тем, что, с целью упрощения и повышения разрешающей способности преобразования, он содержит инвертор, два преобразователя прямого кода в дополни гельный и выходной коммутирующий блок, содержащий дна переключателя, при этом селектор октанта содержит трехразрядный блок сложения с единицей и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, входы разрядов трехразрядного блока сложения с единицей являются соотПреобразователь работает следующим образом.

В первом, четвертом, пятом и восьмом октантах блок 7 использует- 3п ся для формирования синусной, а блок

8 — для формирования косинусной зависимости. В остальных октантах они меняются ролями . Это обеспечивается выходным коммутирующим блоком 12.

Преобразователи 5 и б прямого кода в дополнительный обеспечивают формирование нарастающих участков зависимостей, если код передается без изменения, и убывающих участков, если б на выходе преобразователей формируется дополнительный код.

Дополнительный код формируется на выходе преобразователя 16 н четырех октантах, а на выходе преобразователя 17 — в нечетных октантах. Кроме того, за счет подачи инвертированного или неивертированного напряжений через переключатели 1 и 2 обеспечивается требуемое изменение знака синусной и косинусной функций за полный период изменения аргумента.

Цикл преобразования начинается с записи н регистр 3 очередного значения аргумента. Частота повторения циклов преобразования лимитируется временем установления сигналов на выходах преобразователя и задается по синхронизирующему входу 15. нетствующими входами селектора октанта, группа выходов младших разрядов регистра кода аргумента соединена с информационными входами пер— ного и второго преобразователей пря— мого кода н дополнительный, выходы которых соединены с входами соответствующего блока постоянной памяти, выходы которых соединены с кодовыми входами первого и нторого умножающих цифроаналоговых преобразователей соответственно, выход первого иэ которых соединен с первым входом первого и вторым входом второго переключателей выходного коммутируюшего блока, а выход второго умножаю— щего цифроаналогового преобразователя — с вторым входом перного и первым входом второго переключателей выходного коммутирующего блока, пер1 1283804

Изобретение относится к вычислительной технике и может быть использовано в устройствах преобразования информации.

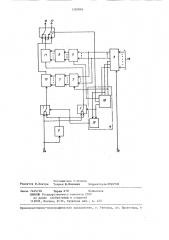

Цель изобретения — упрощение и повьппение разрешающей способности преобразования, На чертеже схематически представлен преобразователь.

Преобразователь содержит первый

1 и второй 2 переключатели, регистр

3 кода аргумента, селектор 4 октанта, первый 5 и второй б преобразователи .прямого кода в дополнительный. первый 7 и второй 8 блоки постоянной памяти, инвертор 9, первый 10 и второй 11 умножающие цифроаналоговые преобразователи, выходной коммутирующий блок 12, информационный вход 13, вход 14 преобразуемого на— пряжения, синхронизирующий вход 15, синусный 16 и косинусный 17 выходы.

Селектор 4 содержит трехраэрядный блок 18 сложения с единицей и элемент 19 ИСКЛЮЧАЮЩЕЕ ИЛИ.! 283804 4 щения преобразования второго преобразователя прямого кода в дополнительный соответственно.

Управляющие коды

ФТ Ф2 К CI С2

5 Коды регистра

I II III шего разряда трехразрядного блока сложения с единицей соединен с управ- !О ляющим входом второго переключателя и с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго разряда ре- 0 гистра кода аргумента, а выход — с управляющим входом первого переклю- 0 чателя, выход третьего разряда регистра кода аргумента соединен с 1 входом разрешения преобразования первого преобразователя прямого ко- 20 да в дополнительный, выходы второго и третьего разрядов трехразрядного блока сложения с единицей соединены с управляющим входом выходного ком— 1 мутирующего блока и с входом разре0 О 1 О 0 1 1 О

1 1 0

0 1 вый и второй выходы которого являют— ся соответственно синусным и косинусным выходами преобразователя, информационный вход преобразователя соединен с первыми входами первого и второго переключателей и через инвертор — с вторыми входами первого и второго переключателей, выход стар0 0 0 О 0 0 1

1 0 1 0 1 О 1

1 1 0 0 1 0

0 О 1 1 0 0 1

1 О 0 1 0 1

1 1 1 О 0 1 0

1283804

Составитель Г.Осипов

Техред И. Попович Корректор А.Обручар

Редактор В,Ковтун

Заказ 7445/50 Тираж 670 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, 7Н-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, r. Ужгород, ул. Проектная, 4