Устройство цикловой синхронизации

Иллюстрации

Показать всеРеферат

Изобретение относится к электросвязи и может использоваться в цифровых системах с импульсно-кодовой модуляцией. Цель изобрения - сокращение времени фазирования. На дискретный опознаватель 2 постуйает групповой сигнал. По сигналу цифрового фазирования, поступающему с циклового распределителя 1, дешифратор 3 отклика и дешифратор 4 ошибки формируют соответственно сигнал отклика при опознавании синхрогруппы и сигнал опшбки при отсутствии сигнала опознавания. Триггер 5 переключения осуществляет разделение двух соседних циклов, обеспечивая поочередную запись реализации откликов через ключи 8, 9 в блоки памяти 12, 13. Ключи 10, 11 осуществляют коммутацию тактовых импульсов на запись и считывание из блоков памяти 12, 13. Запись в ячейки памяти осуществляется по адресам, сформированным счетчиком 7 цикла. При появлении с дешифратора 4 сигнала ошибки триггер 6 фиксации подает сигнал на дешифратор 15 фазы, подготавливая его к определению новой фазы цикла. Сигнал на его выходе появляется только при совпадении в двух соседних циклах откликов , проходящих через элемент ИЛИ 14, после переключения триггера 6. 1 ил. (Л

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК

А1

09) (11) Ц11 4 Н 04 1 7/08

ОПИСАНИЕ ИЗОБРЕТЕНИЯ

И ASTOPCHOMV СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР пО делАм изОБРетений и oTHpblTHA (21) 3869128/24-09 (22) 21.03.85 (46) 15.01.87 ° Бюл. 9 2 (71) Ленинградский электротехнический институт связи им. проф. M.À.Áoí÷Бруевича (72) Н.В.Гольцова и А.В.Буданов (53) 621.394.662 (088 ° 8) (56) Заводское описание аппаратуры

"Думка", ТО,ч.11, ячейка 1 MC ЗТ.З.

089044. Минск, завод "Промсвязь", 1979. (54) УСТРОЙСТВО ЦИКЛОВОЙ СИНХРОНИЗАЦИИ (57) Изобретение относится к электросвязи и может использоваться в цифровых системах с импульсно-кодовой модуляцией. Цель иэобрения — сокращение времени фазирования. На дискретный опознаватель 2 поступает групповой сигнал. По сигналу цифрового фазирования, поступающему с циклового распределителя 1, дешифратор 3 отклика и дешифратор 4 ошибки формируют соответственно сигнал отклика при опознавании синхрогруппы и сигнал ошибки при отсутствии сигнала опознавания. Триггер 5 переключения осуществляет разделение двух соседних циклов, обеспечивая поочередную запись реализации откликов через ключи 8, 9 в блоки памяти 12, 13 °

Ключи 10, 11 осуществляют коммутацию тактовых импульсов на запись и считывание из блоков памяти 12, 13.

Запись в ячейки памяти осуществляется по адресам, сформированным счетчиком 7 цикла. При появлении с дешифратора 4 сигнала ошибки триггер 6 фиксации подает сигнал на дешифратор

15 фазы, подготавливая его к определению новой фазы цикла. Сигнал на его выходе появляется только при совпадении в двух соседних циклах откликов, проходящих через элемент ИЛИ

14 после переключения триггера 6.

1 ил.

1283873

Изобретение относится к электросвязи и может быть использовано в системах передачи данных, в том ч»еле г> цифровых системах с импульсно-кодовой модуляцией. 5

Цель»зь>брстенця -- сокращение време пи фаз п>ров а ни я.

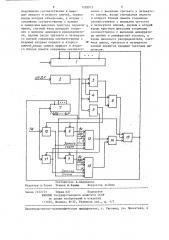

На чертеже изображена блок-схема предлагаемого устройства.

Устройство содержит цикловой рас пределитель 1, дискретный опознаватель 2, дешифратор 3 отклика, дешифратор 4 ошибки, триггер 5 переключения, триггер 6 фиксации, счетчик 7 цикла, первый 8, второй 9, третий 10 и четвертый 11 ключи, первый 12 и второй 13 блоки памяти, элемент ИЛИ 14, дешифратор IS фазы.

Устройство работает следующим ъ), образом.

/ut, Групповой сигHHJl из дискретного канала поступает на вход дискретного оно знав ателя 2. Ци клоп ой ра спределитель 1 формирует сигнал цикловой синхронизации, который поступает на первые входы дешифраторов 3 и 4. По сигналу циклового фазирования с циклового распределителя 1 на выходах дешифраторов 3 и 4 формируется сигнал отк30 лика при наличии сигнала об Опознавании синхрогруппы с дискретного опознавателя 2 и сигнал ошибки при отсутствии сигнала опознавания. При появлении сигнапа ошибки с выхода дешифратора 4 триггер 6 фиксации подает соответствующий сигнал на дешифратор 15 подготавливая его к определению новой фазы цикла. Очередной сигнал цикловой синхронизации с выхода циклового распределителя 1 посту40 пает на счетный вход триггера 5, который осуществляет разделение двух соседних циклов путем обеспечения поочередной записи реаггизаций откликов за цикл в пергзый 1? и второй 13 биоки памяти через первый и второ>г 9 ключи. Для этого с помощью третьего

10 и четвертого 11 ключей осуществляется коммутация тактовых импульсов

1 на входы записи и считывания блоков

12 и 13 памяти.

В любой конкретный цикл при установке триггера 5 в нуль открывается второй ключ 9 и осуществляется запись реализаций откликов во второй блок 13 памяти за этот цикп, Для этого на вход записи второго блока 13 памяти через четвертый кл.оч 11 подлются тактовые импульсы. Запись в ячейки памяти осуществляется !3 соотсетствии с состоянием со "133I02 па адресных гходахр пОступающих с выходОП счетчика 7.

Одновременно с этим тактовые импульсы поступают на вход считывания первого блока 12 памяти и осуществляют вывод реализаций откликов за предыдущий цикл.

Через элемент ИЛИ 14 реализация

Откликов за предыдущий цикл поступает на второй вход дешифратора 15, на первый вход которого поступает реализация откликов с выхода дискретного опознавателя 2. Сигнал на выходе дешифратора 15 фазы появляется только при совпадении Отклике.:. з дву .сосецних циклах после того каг". Осущестзлено переключение триггера 6.

Наиболее характерно проявление положительных свойств предлагаемого устройства в процессе фазирования при опознавании ложной синхрогруппы, так как поиск ведется одновременно в двух циклах и появление ложной синхрогруппы не приводит к необходимости наЧинать накапливание откликов сначала. формула изобретения

Устройство цикловой синхронизации. содержащее счетчик цикла, триггер фиксации и дешифратор фазы, выход которого соединен с установочными входами циклового распредепителя, выход которого соединен с первыми входами дешифратора отклика и дешифратора ошибки; вторые входь> которь>х соединены с выходом дискретного Опо=навателя и первыми входами дешифратора фазы и первого кггоча, О т л и ч аю щ е е с я тем, что, с целью сокращения времени фаэирования, э негогвведены первый и второй блоки памяти, второй, третий, и четвертые ключи„ триггер перек гючения, 1 элемент ИНИ, первый и второй вход которого соединены с выходами первого и второго блоков памяти, а выходс вторым входом дешифратора фазы, третий вход которого соединен с выходом триггера фиксации, а выход — с установочным входом счетчика цикла, выходы которого соединены с адресны ми входами первого и второго блоков ггамяти информационные входы которых

1283873

10 пульсов.

Составитель А. Андрианов

Редактор А. Ревин Техред В. Кадар - Корректор М. Пажа

Заказ 7452/53 Тираж 637 Подписное

ВНИИПО Гасударственного комитета СССР па делам изобретений и открытий

113035, Москва, iK-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 подключены соответственна к выходам первого и второго ключей, первые входы которь1х объеди. ены, а вторые соединены соответственно с прямым и инверсным выходами триггера переклю- 5 чения, счетный вход которого соединен с выходом циклового распределителя, первые входы третьего и четвертого ключей соединены соответственна с вторыми входами первого и второго ключей входы записи первого и второ 1 го блоков памяти соединены соатветст1 ванна с выходами третьего и четвертсго ключей, входы считывания первого и второго блоков памяти соединены соответственно с выходами третьего и четвертого ключей, первый и второй входы триггера фиксации соединены соответственно с выходами дешифратора ошибки и дешифратора отклика, а входы циклавого распределителя, счетчика цикла, третьего и четвертого ключей являются входами тактовых им