Преобразователь двоично-десятичного кода в двоичный

Иллюстрации

Показать всеРеферат

Изобретение относится к области. автоматики и вычислительной техники и может быть использовано при построении преобразователей целых и.дробных десятичных чисел в двоичные.Целью изобретения является повышение быстродействия преобразователя. Поставленная цель достигается за счет , того, что преобразователь, реализующий алгоритм суммирования эквивалентов , осуществляет одновременную обработку К десятичных разрядов с формированием уплотненного адреса ПЗУ при помощи промежуточного преобразо- «g вателя К-разрядного двоично-десятичного кода в двоичный код. 1 ил. //

СОЮЗ СОВЕТСКИХ

СОЦИАЛИСТИЧЕСКИХ

РЕСПУБЛИК дц4 Н 03 М 7!12

Р В(ЗРГ/ÐФФ Ъ у7 II Ч

13, ОПИСАНИЕ ИЗОБРЕТЕНИЯ

Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССР

ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ (21) 3912159/24-24 (22) 14. 06. 85 (46) 15.01.87, Бюл. Ф 2 (71) Минский радиотехнический институт (72) А,А. Жалковский и А.А. Шостак (53) 681.3?5(088.8) (56) Авторское свидетельство СССР

N- 760085, кл. G 06 F 5/02, 1980.

Авторское свидетельство СССР .N- 798800, кл, G 06 F, 1981.

„.SU, 1283978 A1 (54) ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНО-ДЕСЯТИЧНОТО КОДА В ДВОИЧНЫЙ (57) Изобретение относится к области, автоматики и вычислительной техники и может быть использовано при построении преобразователей целых и.дробных десятичных чисел в двоичные.Целью изобретения является повышение быстродействия преобразователя. Поставленная цель достигается за счет того, что преобразователь, реализующий алгоритм суммирования эквивалентов, осуществляет одновременную обработку К десятичных разрядов с формированием уплотненного адреса ПЗУ при помощи промежуточного преобразоФ вателя К-разрядного двоично-десятичного кода в двоичный код. 1 ил.

12819 (8

Первый 3 и второй 4 блоки предназначены для хранения двоичных экви— валентов первой и второй частей дво(ичного значения i-ой преобразуемой

lK-разрядной группы десятичных цифр соответственно. Количество двоичных разрядов на выходе первого 3 и вто:рого 4 блоков хранения двоичных эквивалентов определяется числом двоичных разрядов, содержашихся н максимальных значечиях двоичных эквивалентов. Первый 3 и второй 4 блоки могут быть реализованы на постаян-Ной памяти.

Изобретение относится к вычислительной технике и может быть использовано для быстрого преобразования ! как целых, так и,пробных десятичных чисел н двоичные, 5

Цель изобретения — повышение быстродействия преобразователя.

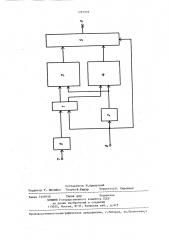

На чертеже приведена структурная схема предлагаемого преобразователя

ll0 двоично-десятичного кода н двоичный.

Преобразователь содержит входной регистр 1, переключатель 2 эквивалентов, первый и второй блоки 3 и 4 хранения эквивалентов, накапливающий сумматор 5, К-разрядный преобразователь 6 двоично-десятичного кода в двоичный, информационный вход 7 преобразователя, управляющий вход 8 преобразователя,выхрд 9 преобразователя.

Входной регистр предназначен для хранения в двоичном коде значения

i-ой К-разрядной группы десятичных цифр исходного операнда на время такта ее преобразования (i = 1, 2, )- ( где Х (— ближайп(ее целое, большее или равное Х; п — разрядность десятичного операнда). Лвоичные значения первой и второй частей входного регистра 1 являются младшими частями адресов, по которым происходит обращение к первому 3 и второму 4 блокам хранения двоичных эквивалентов, Входной регистр 1 целесообразно реализовать на двухтактных синхронных D-триггерах..

Переключатель 2 эквивалентов осуществляет формирование старшей части адресов двоичных эквивалентов, хранящихся в блоках 3 и 4. Fro разрядность определяется количеством К-разрядных групп десятичных цифр н преобразуе— мом числе. Он може г быть реализован

HB двухтактном синхронном двоичном счетчике. !

Пакаплинающий сумматор 3 нроизнодит суммирование двоичных экниналентон, выбранных из первого 3 и второго 4 блоков, с ранее накопленным результатом, Fго можно построить на комбинационном сумматоре с сохране-, нием переносов, приводящем трехрядный код к двухрядному, комбинационном сумматоре с ускоренным переносом и регистре для запоминания результата суммирования.

Преобразователь 6 предназначен для преобразования К-разрядной группы десятичных цифр в двоичный код.

При К = 2 его целесообразно реализовать на постоянной памяти, При

К > 2 наиболее приемлемым являются варианты его построения на комбинационных схемах.

В основу предлагаемого преобразователя двоично-десятичного кода в двоичный положен следующий принцип. Преобразование п-разрядного десятичного числа происходит за и

t--I тактов. В каждом такте обраК батывается К его десятичных иифр, причем они предварительно преобразуются из двоично-десятичного кода н более компактный двоичный ь.1д. По— скольку двоичное значение i-ой Кразрядной группы десятичных цифр может быть представлено н виде (A . + В ) V. где A и В, — первая (1 1 1 и вторая части двоичного значения

i-oA группы десятичных цифр, а ее вес, то преобразование этой группы десятичных цифр представляет собой суммирование двух двоичных эквивалентов значений А. Ъ и В. V. ! 1 с суммой предыдущих эквивалентон.

Рассмотрим работу предлагаемого преобразователя при К = 3.

Перед началом преобразования устанавливаются в ноль триггеры входного регистра 1, переключателя 2 эквивалентов и накапливающего сумматора 5 (эти цепи установки на чертеже не показаны). Через вход 7 преобразователя поступает двоично-десятичное значение трех первых десятичных цифр, которое преобразуется преобразователем 6 н 1((-разрядный двоичный код. Первый импульс, поступающий с управляющего входя 8 преобразователя, .записывает во входной регистр 1 двоичное значение первых трех десятич12ч3978 ных цифр, а в накапливающий сумматор 5 — нулевую информацию, выработанную блоками 3 и 4 по исходному (нулевому) состоянию входного реги— стра 1, Этот же импульс переводит переключатель 2 эквивалентов на формирование значения старшей части адресов двоичных эквивалентов для первой 3-разрядной группы десятичных цифр. Младшая часть адреса двоичного 10 эквивалента первого слагаемого

А V. определяется значением первых

1 пяти разрядов входного регистра 1, а младшая часть адреса двоичного эквивалента второго слагаемого В V

1 значением вторых пяти разрядов регистра 1. Двоичные эквиваленты первого и второго слагаемых хранятся в первом 3 и втором 4 блоках хранения двоичных эквивалентов (по 32 двоичных 20 эквивалента в каждом блоке на каждую

3-разрядную группу десятичных цифр соответственно).

Выбранные двоичные эквиваленты поступают параллельным кодом на входы накапливающего сумматора 5, где осуществляется их суммирование.

Второй импульс с управляющего входа 8 преобразователя записывает результат суммирования его исходного (нулевого) содержимого .со значением двух первых двоичных эквивалентов. Этот же импульс записывает во входной регистр

1 преобразованное в двоичный код зна-. чение вторых трех десятичных цифр и переводит переключатель 2 эквивалентов на формирование значения старшей части адресов двоичных эквивалентов для второй 3-разрядной группы. Работа преобразователя 6 выполняется параллельно с работой блоков 3, 4 и сумматора 5.

Подобным . бравом пролсходит преобразование каждой последующей 3-разрядной группы десятичных цифр до тех пор, пока не будут преобразованы все десятичные разряды исходного числа, а в накапливающем сумматоре 5 не сформируется искомое двоичное число, которое поступает на выход 9 преобразователя. Общее время преобразования и-разрядного десятичного числа опреп деляется выражением T = ) — (t где

3 — длительность выполнения одного такта, Формула и а б р е т е н и я

Преобразователь двоично-десятичного кода в двоичный, содержащий входной регистр, переключатель эквивален,тов, первый и второй блоки хранения эквивалентов и накапливаощий сумматор, выходы которого являются выходами преобразователя, управляющий вход которого соединен с синхровходом входного регистра переключателя эквивалентов и накапливающего сумматора, первый и второй входы которого соединены соответственно с выходами первого и второго блоков хранения эквивалентов, младший разряды адресных входов которых соединены соответственно с первым и вторым выходами входного регистра, а старшие разряды адресных входов. первого и второго блоков хранения эквивалентов соединены с выходом переключателя эквивалентов,о тл и ч а ю шийся тем, что, с целью повышения быстродействия преобразователя, в него введен К-разрядный преобразователь двоично-десятичного кода в двоичный, выход которого соединен со входом входного регистра, а вход — с информационным входом преобразователя.

1 28 3978

Составитель М, Аршавский

Редактор Т. Митейко Техред В. Кадар Корректор Е. Сирохман

Заказ 7459/58 Тираж*899 Подписное

ВНИИПИ Государственного комитета СССР по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб,, д.4/5

Производственно-полиграфическое предприятие, г,ужгород, ул.Проектная,4